- 您现在的位置:买卖IC网 > PDF目录385871 > ST72T85A5Q6 (意法半导体) 8-BIT MCU FOR RDS WITH 48K ROM, 3K RAM, ADC, TWO TIMERS, TWO SPIs, I2C AND SCI INTERFACES PDF资料下载

参数资料

| 型号: | ST72T85A5Q6 |

| 厂商: | 意法半导体 |

| 英文描述: | 8-BIT MCU FOR RDS WITH 48K ROM, 3K RAM, ADC, TWO TIMERS, TWO SPIs, I2C AND SCI INTERFACES |

| 中文描述: | 8位微控制器48,000铁路发展策略光盘,3K内存,ADC,两个定时器,2个SPI,I2C和脊髓损伤接口 |

| 文件页数: | 59/117页 |

| 文件大小: | 748K |

| 代理商: | ST72T85A5Q6 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页当前第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页

59/117

ST7285C

I

2

C BUS INTERFACE

(Cont’d)

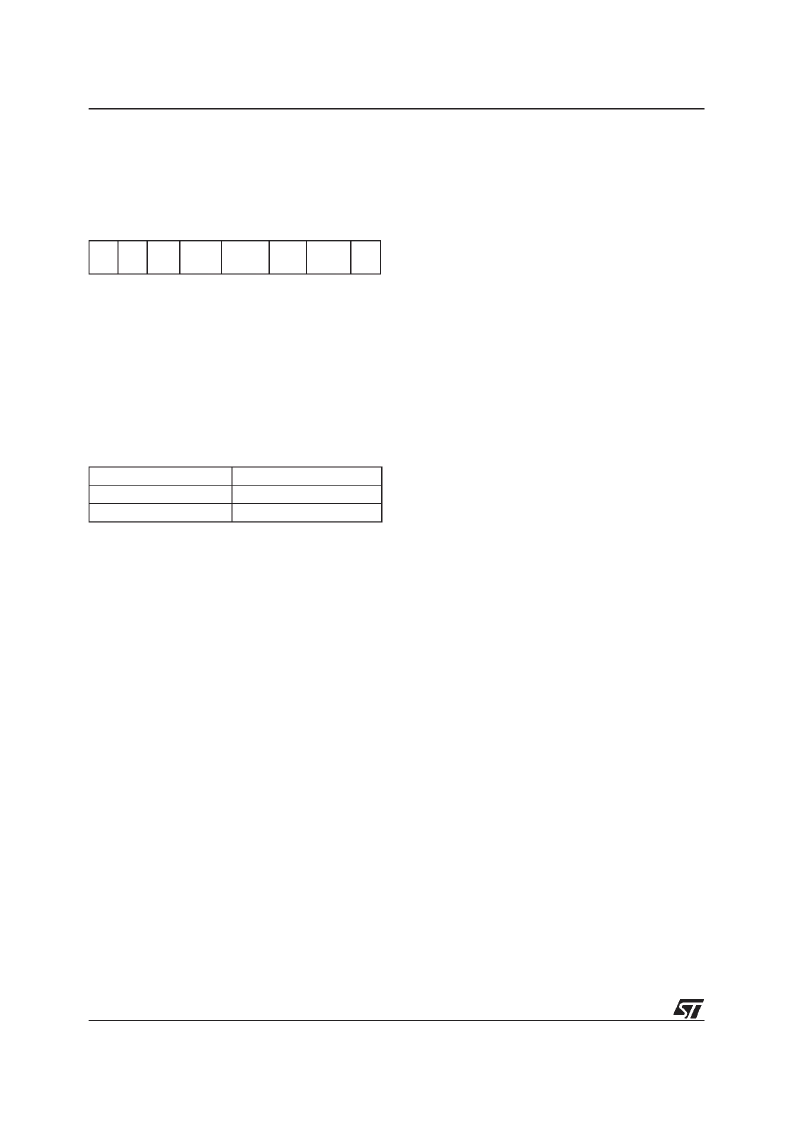

CONTROL REGISTER (CR)

Address: 0028h

Reset Value: 00h

—

Read / Write

b7-6 = reserved.

b5:

PE

Peripheral Enable

1 : Master/Slave capability.

0 : Peripheral disabled ( all outputs are released).

When this bit is reset, all the bits of the control reg-

ister and the status register except the Stop bit are

reset.

PE selects the alternate function on the corre-

sponding I/O.

This bit is set by software and it is cleared by soft-

ware or by a reset.

b4:

ENGC

Enable General call

When this bit is set, the peripheral acknowledges

the general call address.

Engc bit is set or cleared by software. It is cleared

when the peripheral is disabled (PE=0) or by reset.

b3:

START

Generation of a Start condition

When the Start bit is set in Slave mode, the inter-

face generates a Start condition as soon as the

bus is free. In Master mode, it generates a repeat-

ed Startcondition. Then an interrupt is generated if

ITE is set.

This bit is set by software and is cleared by soft-

ware, when the peripheral is disabled (PE=0) or by

reset. It is automatically cleared after the start con-

dition is sent.

b2:

ACK

Acknowledge level

When this bit is set, an acknowledge is returned

after an address byte is received or after a data

byte is received.

When it is cleared, no acknowledge is returned.

It is set by software and it is cleared by software,

when the peripheral is disabled (PE=0) or byreset.

b1:

STOP

Generation of a Stop condition

If the Stop bit is set in Master mode then a stop

condition is generated after the transfer of the cur-

rent byte or after that the current Start condition is

sent.

If it is set in Slave mode then both SCL and SDA

lines are released in order to recover from an error

condition and the peripheral waits for a detection

of a Start or a Stop condition. Then the interface

waits for a Stop or a Start condition on the lines.

This bit can be cleared by software. It is automati-

cally cleared after the stop condition is sent on the

SCL line in Master mode or by reset.

b0:

ITE

Interrupt Enable

When the Interrupt Enable bit is set, the I

2

C inter-

face interrupt is generated after anyone of these

following conditions

– A Start condition is generated in Master mode.

– The address is matched in Slave mode while the

ACK flag is at a logic high.

– A data byte has been received or is to be trans-

mitted.

– A loss of arbitration of the bus to another Master

in Master mode.

– A misplaced Start or Stop condition is detected

– There is no acknowledge.

– A Stop condition has been detected in Slave

mode. While the ITE flag is set, an interrupt is

generated, SCL is hold low and the transfer is

suspended except when a loss of arbitration or a

detection of a Stop condition have been detect-

ed. ITEis reset by software, when the peripheral

is disabled (PE=0) or by reset.

7

0

-

-

PE

ENGC

START

ACK

STOP

ITE

PE = 0

PA6 = normal I/O

PA4 = normal I/O

PE = 1

PA6 = I

2

C DATA

PA4 = I

2

C CLOCK

相关PDF资料 |

PDF描述 |

|---|---|

| ST730C08L3 | PHASE CONTROL THYRISTORS |

| ST730C08L3L | PHASE CONTROL THYRISTORS |

| ST730C12L0 | PHASE CONTROL THYRISTORS |

| ST730C12L0L | PHASE CONTROL THYRISTORS |

| ST730C12L1 | PHASE CONTROL THYRISTORS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST730 | 制造商:IRF 制造商全称:International Rectifier 功能描述:PHASE CONTROL THYRISTORS Hockey Puk Version |

| ST7-30 | 制造商:SUPERWORLD 制造商全称:Superworld Electronics 功能描述:POWER TRANSFORMER |

| ST-7300 | 制造商:GC Electronics 功能描述: |

| ST730186-3 | 制造商:KEMET Corporation 功能描述: 制造商:KET 功能描述: |

| ST730268-1 | 制造商:KEMET Corporation 功能描述: 制造商:KET 功能描述: |

发布紧急采购,3分钟左右您将得到回复。