- 您现在的位置:买卖IC网 > PDF目录385871 > ST72T85A5Q6 (意法半导体) 8-BIT MCU FOR RDS WITH 48K ROM, 3K RAM, ADC, TWO TIMERS, TWO SPIs, I2C AND SCI INTERFACES PDF资料下载

参数资料

| 型号: | ST72T85A5Q6 |

| 厂商: | 意法半导体 |

| 英文描述: | 8-BIT MCU FOR RDS WITH 48K ROM, 3K RAM, ADC, TWO TIMERS, TWO SPIs, I2C AND SCI INTERFACES |

| 中文描述: | 8位微控制器48,000铁路发展策略光盘,3K内存,ADC,两个定时器,2个SPI,I2C和脊髓损伤接口 |

| 文件页数: | 72/117页 |

| 文件大小: | 748K |

| 代理商: | ST72T85A5Q6 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页当前第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页

72/117

ST7285C

4.9 RDS G.B.S

4.9.1 Introduction

The main task of the GBS module is to acquire

Group and Block Synchronization of a received

RDS data steam, which is provided in a modified

shortened cyclic code.

In order to achieve synchronization, a syndrome is

calculated on every data clock pulse. Detection of

a valid syndrome is indicated by flag VSI with as-

sociated interrupt, while the corresponding block is

kept in BL(0:2). Starting in BIT_SYNC mode the

SW can use CNA zero count interrupt (CNA=1)

and VSI check for synchronization phase. If the

synchronization criteria is fulfilled, the SW can

switch to BLK_SYNC mode, setting counter CNA

to 26 and CNB to the current block code. The SW

maintains block synchronization easily by check-

ing VSI and ORD, which indicates a correct block

order.

An optional GRP_SYNC mode can be entered for

RDS standby operation using the appropriate

counter interrupt selection.

The combination of software triggered syndrome

calculation, a second 26-bit shift register and a 26-

bit quality register, allow highly flexible error cor-

rection by software.

Single quality errors, representing a 1 or 2 bit

RDSDAT error, are indicated by the SQE flag.

They can be corrected by SW with high security.

4.9.2 Features

– Hardware implemented decoding of RDS data

stream.

– Hardware triggered syndrome calculation with

every rising edge of RDSCLK.

– Storage of 26 RDS bits (1 block).

– Fast syndrome calculation

(within 2.4

μ

s at f

OSC

=8.664MHz).

– 5-bits RDS-counter CNA and 2-bit RDS-block

counter CNB.

– Selectable counter interrupt for BIT/BLOCK/

GROUP-SYNC mode.

– “Valid Syndrome” detection unit with interrupt

and block code output.

– Selectable MMBS Radio Paging option for block

E syndrome detection.

– “Valid Block Order” flag.

– Extended “error correction by software” support.

– Software triggered syndrome calculation.

– Parallel storage of 26 RDSDAT bits and 26

QUALITY bits for high flexibility.

– Single/Multiple quality-error flags.

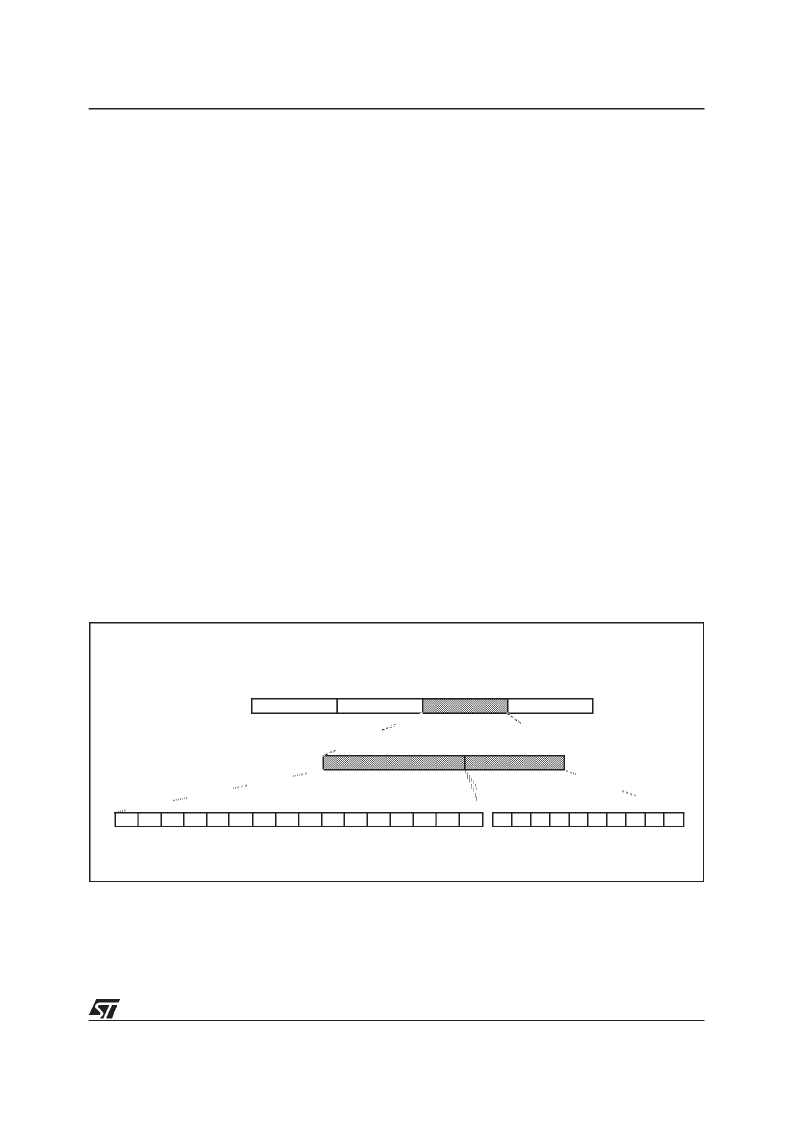

Figure 34. Principles of Baseband Coding

BLOCK1

BLOCK2

BLOCK3

BLOCK4

GROUP = 4 BLOCKS = 104 BITS

m

15

m

14

m

13

m

12

m

11

m

10

m

9

m

8

m

7

m

6

m

5

m

4

m

3

m

2

m

1

m

0

c

9

’

c

8

’

c

7

’

c

6

’

c

5

’

c

4

’

c

3

’

c

2

’

c

1

’

c

0

’

BLOCK = 26BITS

INFORMATION WORD =16-BITS

CHECK WORD = 10-BITS

相关PDF资料 |

PDF描述 |

|---|---|

| ST730C08L3 | PHASE CONTROL THYRISTORS |

| ST730C08L3L | PHASE CONTROL THYRISTORS |

| ST730C12L0 | PHASE CONTROL THYRISTORS |

| ST730C12L0L | PHASE CONTROL THYRISTORS |

| ST730C12L1 | PHASE CONTROL THYRISTORS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST730 | 制造商:IRF 制造商全称:International Rectifier 功能描述:PHASE CONTROL THYRISTORS Hockey Puk Version |

| ST7-30 | 制造商:SUPERWORLD 制造商全称:Superworld Electronics 功能描述:POWER TRANSFORMER |

| ST-7300 | 制造商:GC Electronics 功能描述: |

| ST730186-3 | 制造商:KEMET Corporation 功能描述: 制造商:KET 功能描述: |

| ST730268-1 | 制造商:KEMET Corporation 功能描述: 制造商:KET 功能描述: |

发布紧急采购,3分钟左右您将得到回复。