- 您现在的位置:买卖IC网 > PDF目录18758 > TRC105 (RFM)IC TXRX 300MHZ-510MHZ 32TQFN PDF资料下载

参数资料

| 型号: | TRC105 |

| 厂商: | RFM |

| 文件页数: | 14/67页 |

| 文件大小: | 0K |

| 描述: | IC TXRX 300MHZ-510MHZ 32TQFN |

| 标准包装: | 1 |

| 频率: | 300MHz ~ 510MHz |

| 数据传输率 - 最大: | 200kbps |

| 调制或协议: | FSK,OOK |

| 应用: | 通用 |

| 功率 - 输出: | 13dBm |

| 灵敏度: | -112dBm |

| 电源电压: | 2.1 V ~ 3.6 V |

| 电流 - 接收: | 3mA |

| 电流 - 传输: | 30mA |

| 数据接口: | PCB,表面贴装 |

| 天线连接器: | PCB,表面贴装 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 32-TQFN |

| 包装: | 标准包装 |

| 产品目录页面: | 583 (CN2011-ZH PDF) |

| 其它名称: | 583-1159-6 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页

�� �

�

�

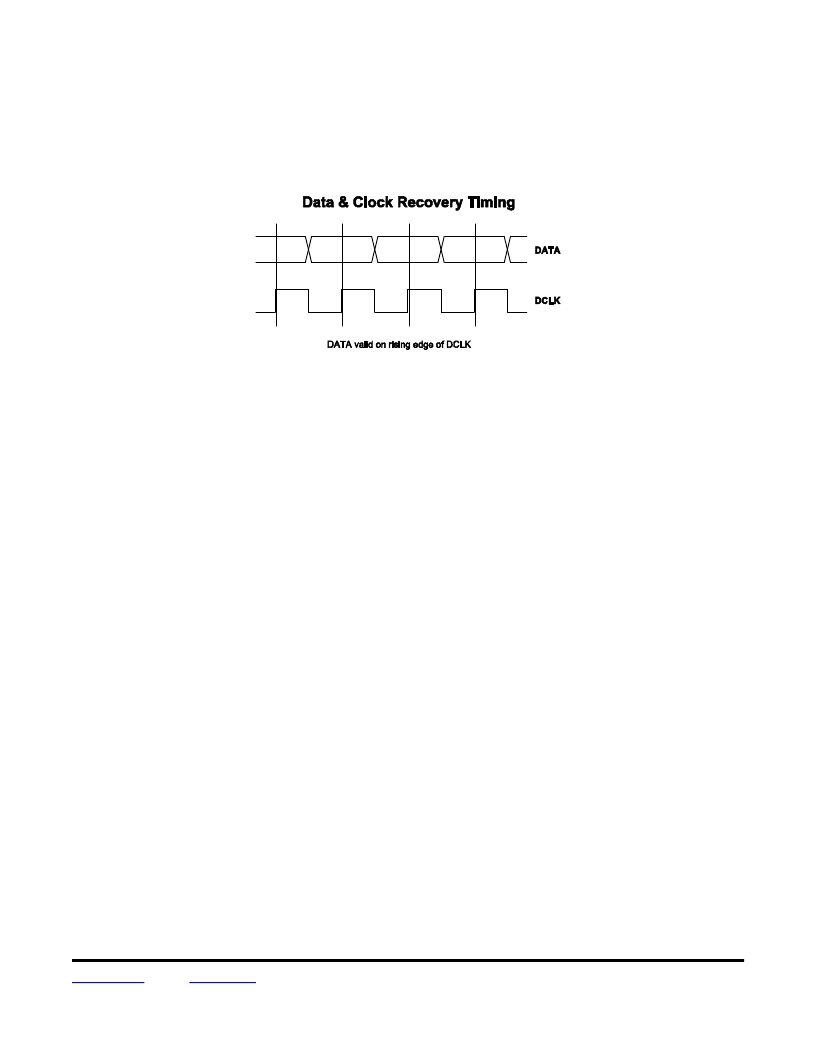

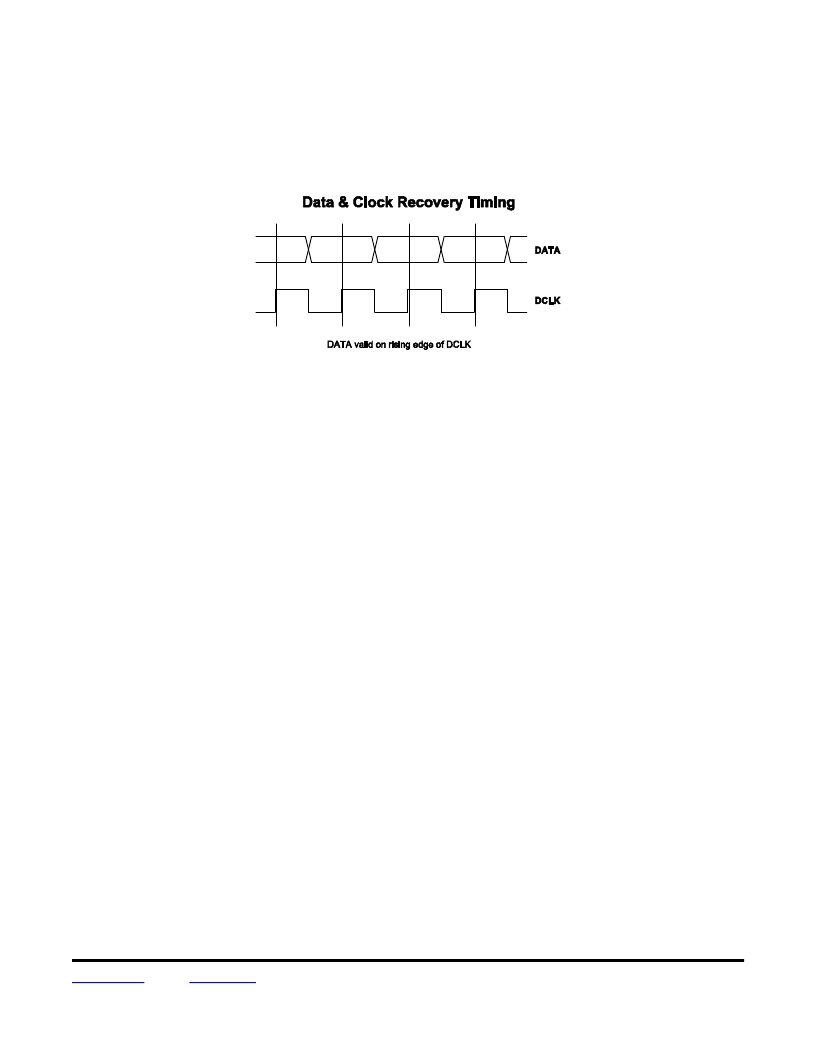

�3.2� Continuous� Mode� Data� and� Clock� Recovery�

�The� raw� output� signal� from� the� demodulator� may� contain� jitter� and� glitches.� Data� and� clock� recovery� converts� the�

�data� output� of� the� demodulator� into� a� glitch-free� bit-stream� DATA� and� generates� a� synchronized� clock� DCLK� to� be�

�used� for� sampling� the� DATA� output� as� shown� in� Figure� 8.� DCLK� is� available� on� pin� IRQ1� when� the� TRC105� oper-�

�ates� in� continuous� mode.�

�Figure� 8�

�To� ensure� correct� operation� of� the� data� and� clock� recovery� circuit,� the� following� conditions� have� to� be� satisfied:�

�?�

�?�

�?�

�A� 1-0-1-� 0…� preamble� of� at� least� 24� bits� is� required� for� synchronization�

�The� transmitted� bit� stream� must� have� at� least� one� transition� from� 0� to� 1� or� from� 1� to� 0� every� 8� bits� during�

�transmission�

�The� bit� rate� accuracy� must� be� better� than� 2� %.�

�Data� and� clock� recovery� is� enabled� by� default.� It� is� controlled� by� RXCFG12_DCLK_Dis[6]� .� If� data� and� clock� re-�

�covery� is� disabled,� the� output� of� the� demodulator� is� directed� to� DATA� and� the� DCLK� output� (IRQ1� Pin� in� continu-�

�ous� mode)� is� set� to� 0.�

�The� received� bit� rate� is� defined� by� the� values� of� the� MCFG03� and� MCFG04� configuration� registers,� and� is� calcu-�

�lated� as� follows:�

�BR� =� F� XTAL� /(2*(C� +� 1)*(D� +� 1)),� with� C� in� the� range� of� 0� to� 255,� and� D� =� 31� (suitable� for� most� applications)�

�with� BR� the� bit� rate� in� kb/s,� F� XTAL� the� crystal� frequency� in� kHz,� C� the� value� in� MCFG03,� and� D� the� value� in�

�MCFG04.� For� example,� using� a� 12.8� MHz� crystal� (12,800� kHz),� the� bit� rate� is� 25� kb/s� when� C� =� 7� and� D� =� 31.�

�3.3� Continuous� Mode� Start� Pattern� Detection�

�Start� pattern� detection� is� activated� by� setting� the� RXCFG12_Recog[5]� bit� to� 1.� The� demodulated� signal� is� com-�

�pared� with� a� pattern� stored� in� the� SYNCFG� registers.� The� Start� Pattern� Detect� signal� (PATTERN)� is� driven� by� the�

�output� of� this� comparator� and� is� synchronized� by� DCLK.� It� is� set� to� 1� when� a� pattern� match� is� detected,� otherwise�

�set� to� 0.� The� pattern� detect� output� is� updated� at� the� rising� edge� of� DCLK.� The� number� of� bytes� used� for� compari-�

�son� is� defined� in� the� RXCFG12_Pat_sz[4..3]� register� and� the� number� of� tolerated� bit� errors� for� pattern� detection�

�is� defined� in� the� RXCFG12_Ptol[2..1]� register.� Figure� 9� illustrates� the� pattern� detection� process.�

�www.RFM.com� E-mail:� info@rfm.com�

�?� 2009-2013� by� RF� Monolithics,� Inc.�

�Technical� support� +1.800.704.6079�

�Page� 14� of� 67�

�TRC105� -� 05/29/13�

�相关PDF资料 |

PDF描述 |

|---|---|

| MT-6-15 | XFRMR 115V 5V 1.75A 6VA 3OUT |

| IF-2-10 | XFRMR 115/230V 5V 400MA 2VA PCB |

| 14A-20-515 | XFRMR PWR 115/230V 5V 750MA 20VA |

| 14A-20-512 | XFRMR PWR 115/230V 5V 750MA 20VA |

| SI4421-A0-FT | IC TXRX FSK 915MHZ 3.8V 16-TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TRC1053 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:10/100M Single Port Transformer Modules |

| TRC1060 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:10/100M Single Port Transformer Modules |

| TRC1062 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:10/100M Single Port Transformer Modules |

| TRC1068 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:10/100M Single Port Transformer Modules |

| TRC1074 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:10/100M Single Port Transformer Modules |

发布紧急采购,3分钟左右您将得到回复。