- 您现在的位置:买卖IC网 > PDF目录17007 > USB-I2C/LIN-CONV-Z (Analog Devices Inc)USB TO I2C/LIN CONV BOARD PDF资料下载

参数资料

| 型号: | USB-I2C/LIN-CONV-Z |

| 厂商: | Analog Devices Inc |

| 文件页数: | 33/104页 |

| 文件大小: | 0K |

| 描述: | USB TO I2C/LIN CONV BOARD |

| 标准包装: | 1 |

| 附件类型: | 适配器板 |

| 适用于相关产品: | ARM7TDMI? |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页当前第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页

ADuC7019/20/21/22/24/25/26/27/28/29

Data Sheet

Rev. F | Page 34 of 104

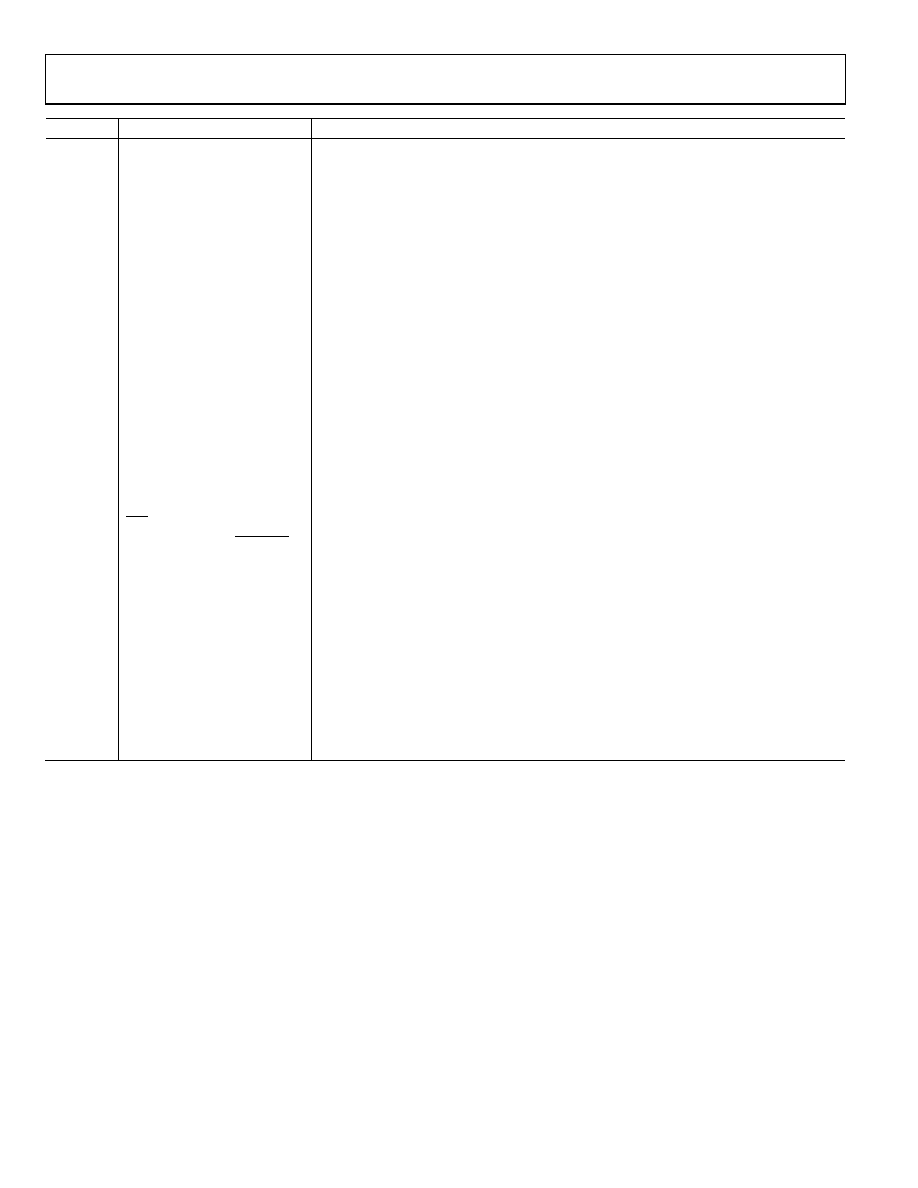

Ball No.

Mnemonic

Description

E1

TMS

JTAG Test Port Input, Test Mode Select. Debug and download access.

E2

BM/P0.0/CMPOUT/PLAI[7]

Multifunction I/O Pin. Boot mode. The ADuC7029 enters UART download mode if BM is low

at reset and executes code if BM is pulled high at reset through a 1 k resistor/General-

Purpose Input and Output Port 0.0/Voltage Comparator Output/Programmable Logic Array

Input Element 7.

E3

DAC2/ADC14

DAC2 Voltage Output/ADC Input 14.

E4

IOVDD

3.3 V Supply for GPIO (see Table 78) and Input of the On-Chip Voltage Regulator.

E5

P3.2/PWM1H/PLAI[10]

General-Purpose Input and Output Port 3.2/PWM Phase 1 High-Side Output/Programmable

Logic Array Input Element 10.

E6

P3.5/PWM2L/PLAI[13]

General-Purpose Input and Output Port 3.5/PWM Phase 2 Low-Side Output/Programmable

Logic Array Input Element 13.

E7

P0.7/ECLK/XCLK/SPM8/PLAO[4]

Serial Port Multiplexed. General-Purpose Input and Output Port 0.7/Output for External

Clock Signal/Input to the Internal Clock Generator Circuits/UART/Programmable Logic Array

Output Element 4.

F1

TDI

JTAG Test Port Input, Test Data In. Debug and download access.

F2

P0.6/T1/MRST/PLAO[3]

Multifunction Pin, Driven Low After Reset. General-Purpose Output Port 0.6/Timer1 Input/

Power-On Reset Output/Programmable Logic Array Output Element 3.

F3

IOGND

Ground for GPIO (see Table 78). Typically connected to DGND.

F4

P3.1/PWM0L/PLAI[9]

General-Purpose Input and Output Port 3.1/PWM Phase 0 Low-Side Output/Programmable

Logic Array Input Element 9.

F5

P3.0/PWM0H/PLAI[8]

General-Purpose Input and Output Port 3.0/PWM Phase 0 High-Side Output/Programmable

Logic Array Input Element 8.

F6

RST

Reset Input, Active Low.

F7

P2.0/SPM9/PLAO[5]/CONVSTART

Serial Port Multiplexed. General-Purpose Input and Output Port 2.0/UART/Programmable

Logic Array Output Element 5/Start Conversion Input Signal for ADC.

G1

TCK

JTAG Test Port Input, Test Clock. Debug and download access.

G2

TDO

JTAG Test Port Output, Test Data Out. Debug and download access.

G3

LVDD

2.6 V Output of the On-Chip Voltage Regulator. This output must be connected to a 0.47 F

capacitor to DGND only.

G4

DGND

Ground for Core Logic.

G5

P0.3/TRST/ADCBUSY

General-Purpose Input and Output Port 0.3/JTAG Test Port Input, Test Reset/ADCBUSY Signal

Output.

G6

IRQ0/P0.4/PWMTRIP/PLAO[1]

Multifunction I/O Pin. External Interrupt Request 0, Active High/General-Purpose Input and

Output Port 0.4/PWM Trip External Input/Programmable Logic Array Output Element 1.

G7

IRQ1/P0.5/ADCBUSY/PLAO[2]

Multifunction I/O Pin. External Interrupt Request 1, Active High/General-Purpose Input and

Output Port 0.5/ADCBUSY Signal Output/Programmable Logic Array Output Element 2.

相关PDF资料 |

PDF描述 |

|---|---|

| HBM10DSEI-S13 | CONN EDGECARD 20POS .156 EXTEND |

| EBC35DCSD-S288 | CONN EDGECARD 70POS .100 EXTEND |

| HBM15DRYN-S13 | CONN EDGECARD 30POS .156 EXTEND |

| RBC17DRES-S13 | CONN EDGECARD 34POS .100 EXTEND |

| HBM15DRYH-S13 | CONN EDGECARD 30POS .156 EXTEND |

相关代理商/技术参数 |

参数描述 |

|---|---|

| USB-I2C-SS | 功能描述:USB 接口集成电路 Driver-free USB to serl SPIslve intrfce RoHS:否 制造商:Cypress Semiconductor 产品:USB 2.0 数据速率: 接口类型:SPI 工作电源电压:3.15 V to 3.45 V 工作电源电流: 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:WLCSP-20 |

| USB-ICP-80C51ISP | 功能描述:程序设计器 - 基于处理器 In-System Programmer for NXP 80C51ISP RoHS:否 制造商:Olimex Ltd. 产品:Programmers 工具用于评估:XMEGA, MegaAVR, tinyAVR 核心:AVR 接口类型:USB 工作电源电压:1.8 V to 5.5 V |

| USB-ICP-LPC2K | 功能描述:程序设计器 - 基于处理器 In-System Programmer for NXP ARM7 LPC2xxx RoHS:否 制造商:Olimex Ltd. 产品:Programmers 工具用于评估:XMEGA, MegaAVR, tinyAVR 核心:AVR 接口类型:USB 工作电源电压:1.8 V to 5.5 V |

| USB-ICP-LPC9XX | 功能描述:程序设计器 - 基于处理器 In-Circuit Programer for NXP LPC9xx RoHS:否 制造商:Olimex Ltd. 产品:Programmers 工具用于评估:XMEGA, MegaAVR, tinyAVR 核心:AVR 接口类型:USB 工作电源电压:1.8 V to 5.5 V |

| USB-ICP-SAB9 | 功能描述:插座和适配器 Socket Adapter Brd USB-ICP-LPC9xx Drvr RoHS:否 制造商:Silicon Labs 产品:Adapter 用于:EM35x |

发布紧急采购,3分钟左右您将得到回复。