- 您现在的位置:买卖IC网 > PDF目录17007 > USB-I2C/LIN-CONV-Z (Analog Devices Inc)USB TO I2C/LIN CONV BOARD PDF资料下载

参数资料

| 型号: | USB-I2C/LIN-CONV-Z |

| 厂商: | Analog Devices Inc |

| 文件页数: | 77/104页 |

| 文件大小: | 0K |

| 描述: | USB TO I2C/LIN CONV BOARD |

| 标准包装: | 1 |

| 附件类型: | 适配器板 |

| 适用于相关产品: | ARM7TDMI? |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页当前第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页

ADuC7019/20/21/22/24/25/26/27/28/29

Data Sheet

Rev. F | Page 74 of 104

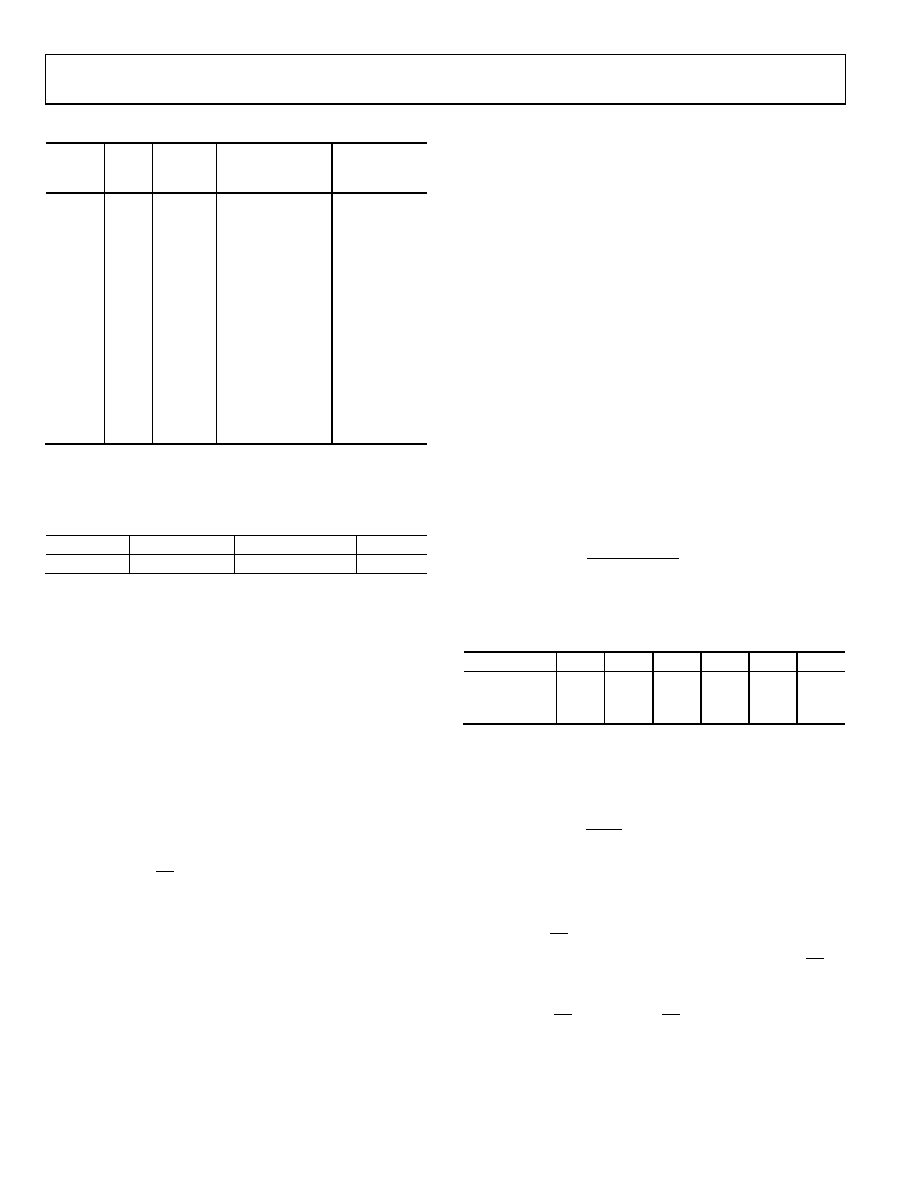

Table 116. COMIID1 MMR Bit Descriptions

Bit 3:1

Status

Bits

Bit 0

NINT

Priority

Definition

Clearing

Operation

000

1

No interrupt

110

0

2

Matching network

address

Read COMRX

101

0

3

Address

transmitted,

buffer empty

Write data to

COMTX or

read COMIID0

011

0

1

Receive line status

interrupt

Read

COMSTA0

010

0

2

Receive buffer full

interrupt

Read COMRX

001

0

3

Transmit buffer

empty interrupt

Write data to

COMTX or

read COMIID0

000

0

4

Modem status

interrupt

Read

COMSTA1

Note that to receive a network address interrupt, the slave must

ensure that Bit 0 of COMIEN0 (enable receive buffer full interrupt)

is set to 1.

Table 117. COMADR Register

Name

Address

Default Value

Access

COMADR

0xFFFF0728

0xAA

R/W

COMADR is an 8-bit, read/write network address register that

holds the address checked for by the network addressable

UART. Upon receiving this address, the device interrupts the

processor and/or sets the appropriate status bit in COMIID1.

SERIAL PERIPHERAL INTERFACE

The ADuC7019/20/21/22/24/25/26/27/28/29 integrate a complete

hardware serial peripheral interface (SPI) on-chip. SPI is an

industry standard, synchronous serial interface that allows eight

bits of data to be synchronously transmitted and simultaneously

received, that is, full duplex up to a maximum bit rate of 3.48 Mb,

as shown in Table 118. The SPI interface is not operational with

core clock divider (CD) bits. POWCON[2:0] = 6 or 7 in master

mode.

The SPI port can be configured for master or slave operation.

and typically consists of four pins: MISO (P1.5), MOSI (P1.6),

SCLK (P1.4), and CS (P1.7).

On the transmit side, the SPITX register (and a TX shift register

outside it) loads data onto the transmit pin (in slave mode,

MISO; in master mode, MOSI). The transmit status bit, Bit 0,

in SPISTA indicates whether there is valid data in the SPITX

register.

Similarly, the receive data path consists of the SPIRX register

(and an RX shift register). SPISTA, Bit 3 indicates whether there

is valid data in the SPIRX register. If valid data in the SPIRX

register is overwritten or if valid data in the RX shift register is

discarded, SPISTA, Bit 5 (the overflow bit) is set.

MISO (Master In, Slave Out) Pin

The MISO pin is configured as an input line in master mode

and an output line in slave mode. The MISO line on the master

(data in) should be connected to the MISO line in the slave

device (data out). The data is transferred as byte wide (8-bit)

serial data, MSB first.

MOSI (Master Out, Slave In) Pin

The MOSI pin is configured as an output line in master mode

and an input line in slave mode. The MOSI line on the master

(data out) should be connected to the MOSI line in the slave

device (data in). The data is transferred as byte wide (8-bit)

serial data, MSB first.

SCLK (Serial Clock I/O) Pin

The master serial clock (SCLK) is used to synchronize the data

being transmitted and received through the MOSI SCLK

period. Therefore, a byte is transmitted/received after eight SCLK

periods. The SCLK pin is configured as an output in master

mode and as an input in slave mode.

In master mode, the polarity and phase of the clock are

controlled by the SPICON register, and the bit rate is defined

in the SPIDIV register as follows:

)

1

(

2

SPIDIV

f

UCLK

CLOCK

SERIAL

+

×

=

The maximum speed of the SPI clock is dependent on the clock

divider bits and is summarized in Table 118.

Table 118. SPI Speed vs. Clock Divider Bits in Master Mode

CD Bits

0

1

2

3

4

5

SPIDIV in Hex

0x05

0x0B

0x17

0x2F

0x5F

0xBF

SPI dpeed

in MHz

3.482

1.741

0.870

0.435

0.218

0.109

In slave mode, the SPICON register must be configured with

the phase and polarity of the expected input clock. The slave

accepts data from an external master up to 10.4 Mb at CD = 0.

The formula to determine the maximum speed is as follows:

4

HCLK

CLOCK

SERIAL

f

=

In both master and slave modes, data is transmitted on one edge

of the SCL signal and sampled on the other. Therefore, it is

important that the polarity and phase be configured the same

for the master and slave devices.

Chip Select (CS Input) Pin

In SPI slave mode, a transfer is initiated by the assertion of CS,

which is an active low input signal. The SPI port then transmits

and receives 8-bit data until the transfer is concluded by

deassertion of CS. In slave mode, CS is always an input.

相关PDF资料 |

PDF描述 |

|---|---|

| HBM10DSEI-S13 | CONN EDGECARD 20POS .156 EXTEND |

| EBC35DCSD-S288 | CONN EDGECARD 70POS .100 EXTEND |

| HBM15DRYN-S13 | CONN EDGECARD 30POS .156 EXTEND |

| RBC17DRES-S13 | CONN EDGECARD 34POS .100 EXTEND |

| HBM15DRYH-S13 | CONN EDGECARD 30POS .156 EXTEND |

相关代理商/技术参数 |

参数描述 |

|---|---|

| USB-I2C-SS | 功能描述:USB 接口集成电路 Driver-free USB to serl SPIslve intrfce RoHS:否 制造商:Cypress Semiconductor 产品:USB 2.0 数据速率: 接口类型:SPI 工作电源电压:3.15 V to 3.45 V 工作电源电流: 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:WLCSP-20 |

| USB-ICP-80C51ISP | 功能描述:程序设计器 - 基于处理器 In-System Programmer for NXP 80C51ISP RoHS:否 制造商:Olimex Ltd. 产品:Programmers 工具用于评估:XMEGA, MegaAVR, tinyAVR 核心:AVR 接口类型:USB 工作电源电压:1.8 V to 5.5 V |

| USB-ICP-LPC2K | 功能描述:程序设计器 - 基于处理器 In-System Programmer for NXP ARM7 LPC2xxx RoHS:否 制造商:Olimex Ltd. 产品:Programmers 工具用于评估:XMEGA, MegaAVR, tinyAVR 核心:AVR 接口类型:USB 工作电源电压:1.8 V to 5.5 V |

| USB-ICP-LPC9XX | 功能描述:程序设计器 - 基于处理器 In-Circuit Programer for NXP LPC9xx RoHS:否 制造商:Olimex Ltd. 产品:Programmers 工具用于评估:XMEGA, MegaAVR, tinyAVR 核心:AVR 接口类型:USB 工作电源电压:1.8 V to 5.5 V |

| USB-ICP-SAB9 | 功能描述:插座和适配器 Socket Adapter Brd USB-ICP-LPC9xx Drvr RoHS:否 制造商:Silicon Labs 产品:Adapter 用于:EM35x |

发布紧急采购,3分钟左右您将得到回复。