参数资料

| 型号: | XRT83L34IV-F |

| 厂商: | Exar Corporation |

| 文件页数: | 7/99页 |

| 文件大小: | 0K |

| 描述: | IC LIU T1/E1/J1 QUAD 128TQFP |

| 标准包装: | 72 |

| 类型: | 线路接口装置(LIU) |

| 驱动器/接收器数: | 4/4 |

| 规程: | T1,E1,J1 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 128-LQFP |

| 供应商设备封装: | 128-TQFP(14x20) |

| 包装: | 托盘 |

| 其它名称: | XRT83L34IV-F-ND |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页

xr

XRT83L34

QUAD T1/E1/J1 LH/SH TRANSCEIVER WITH CLOCK RECOVERY AND JITTER ATTENUATOR REV. 1.0.1

12

TCLK_0

TCLK_1

TCLK_2

TCLK_3

1

128

103

102

I

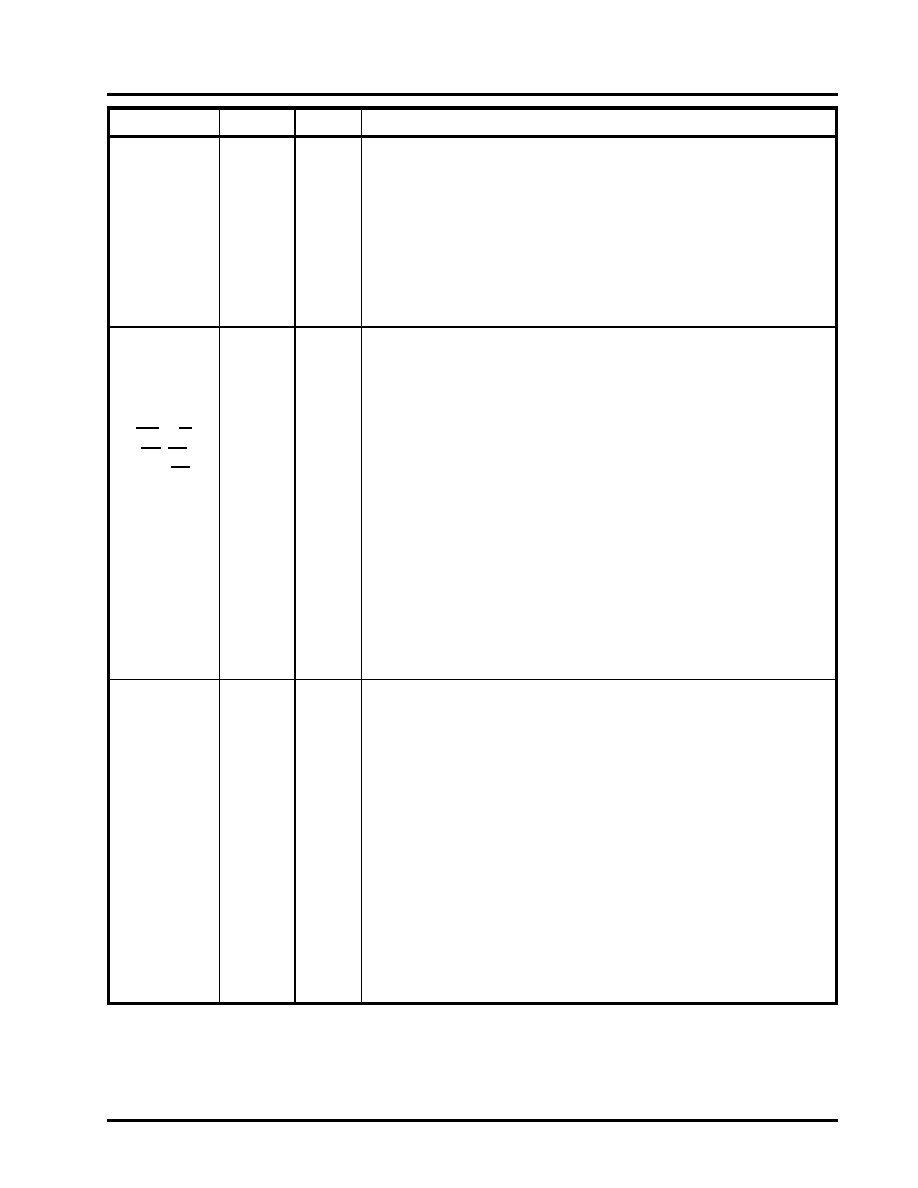

Transmit Line Clock Input - Channel n:

The Transmit Section of Channel n will use this input pin to sample and latch

the data that is present on the "TPOS_n/TDATA_n" and "TNEG_n" input pins.

This input clock signal also functions as the timing source for the "Transmit

Direction" signal within the Channel.

For T1 Applications, the user is expected to apply a 1.544MHz clock signal to

this input pin. Similarly, for E1 Applications, the user is expected to apply a

2.048MHz clock signal to this input pin.

NOTE: Internally pulled “Low” with a 50k

resistor for all channels.

TAOS_0

TAOS_1

TAOS_2

TAOS_3

WR_R/W

RD_DS

ALE_AS

CS

69

70

71

72

69

70

71

72

I

Transmit All Ones Command Input - Channel n: (Hardware Mode ONLY)

The exact function of these input pins depend upon whether the XRT83L34

device has been configured to operate in the HOST or Hardware Modes, as

described below.

Hardware Mode Operation - Transmit All Ones Command Input - Channel

n - TAOS_n:

These input pins permits the user to command a given Channel to transmit an

"Unframed, All Ones" pattern (via the outbound DS1/E1 line signal) to the

remote terminal equipment.

Setting this pin to the logic "HIGH" level configures the Transmit Section (of

the corresponding channel) to transmit an Unframed, All Ones pattern via the

outbound DS1/E1 line signal.

Setting this pin to the logic "LOW" level, configures the Transmit Section (of

the corresponding channel) to transmit normal traffic via the outbound DS1/E1

line signal.

Host Mode Operation: These pins act as various microprocessor functions.

NOTE: These pins are internally pulled “Low” with a 50k

resistor.

TXON_0

TXON_1

TXON_2

TXON_3

122

123

124

125

I

Transmitter Turn On for Channel _0

Hardware mode

Setting this pin "High" turns on the Transmit Section of Channel _0 and has no

control of the Channel_0 receiver. When TXON_0 = “0” then TTIP_0 and

TRING_0 driver outputs will be tri-stated.

NOTE: In Hardware mode only, all receiver channels will be turned on upon

power-up and there is no provision to power them off. The receive

channels can only be independently powered on or off in Host mode.

In Host mode

The TXON_n bits in the channel control registers turn each channel Transmit

section ON or OFF. However, control of the on/off function can be transferred

to the Hardware pins by setting the TXONCTL bit (bit 6) to “1” in the register at

address hex 0x42.

Transmitter Turn On for Channel _1

Transmitter Turn On for Channel _2

Transmitter Turn On for Channel _3

NOTE: Internally pulled "Low" with a 50k

resistor for all channels.

SIGNAL NAME

PIN #TYPE

DESCRIPTION

相关PDF资料 |

PDF描述 |

|---|---|

| XRT83L38IB-F | IC LIU T1/E1/J1 OCTAL 225BGA |

| XRT83SH314IB-F | IC LIU T1/E1/J1 14CH 304TBGA |

| XRT83SH38IB-F | IC LIU SH T1/E1/J1 8CH 225BGA |

| XRT86L30IV-F | IC LIU/FRAMER TI/E1/J1 SGL 128LQ |

| XRT86VL30IV-F | IC FRAMR/LIU T1/E1/J1 QD 128LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XRT83L34IVTR | 功能描述:外围驱动器与原件 - PCI RoHS:否 制造商:PLX Technology 工作电源电压: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:FCBGA-1156 封装:Tray |

| XRT83L34IVTR-F | 功能描述:外围驱动器与原件 - PCI RoHS:否 制造商:PLX Technology 工作电源电压: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:FCBGA-1156 封装:Tray |

| XRT83L38 | 制造商:EXAR 制造商全称:EXAR 功能描述:OCTAL T1/E1/J1 LH/SH TRANSCEIVER WITH CLOCK RECOVERY AND JITTER ATTENUATOR |

| XRT83L38_07 | 制造商:EXAR 制造商全称:EXAR 功能描述:OCTAL T1/E1/J1 LH/SH TRANSCEIVER WITH CLOCK RECOVERY AND JITTER ATTENUATOR |

| XRT83L38ES | 功能描述:外围驱动器与原件 - PCI RoHS:否 制造商:PLX Technology 工作电源电压: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:FCBGA-1156 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。