- 您现在的位置:买卖IC网 > PDF目录300164 > ZL30402/QCG1 (ZARLINK SEMICONDUCTOR INC) ATM/SONET/SDH SUPPORT CIRCUIT, PQFP80 PDF资料下载

参数资料

| 型号: | ZL30402/QCG1 |

| 厂商: | ZARLINK SEMICONDUCTOR INC |

| 元件分类: | 数字传输电路 |

| 英文描述: | ATM/SONET/SDH SUPPORT CIRCUIT, PQFP80 |

| 封装: | 14 X 14 MM, 1.40 MM HEIGHT, LEAD FREE, MS-026BEC, LQFP-80 |

| 文件页数: | 11/44页 |

| 文件大小: | 472K |

| 代理商: | ZL30402/QCG1 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

ZL30402

Data Sheet

19

Zarlink Semiconductor Inc.

RefSel: Reference Source Select. The RefSel (pin 47) input selects the PRI (primary) or SEC (secondary) input

as the reference clock for the Core PLL. The logic level at this input is sampled by the rising edge of F8o.

RefAlign: Reference Align. The RefAlign (pin 48) input controls phase realignment between the input reference

and the generated output clocks.

4.1.2

Status Pins

The ZL30402 has two dedicated status pins for indicating modes of operation. These pins are listed below:

LOCK. This output goes high when the core PLL is locked to the selected Acquisition PLL.

HOLDOVER - This output goes high when the Core PLL enters Holdover mode. The Core PLL will switch to

Holdover mode if the respective Acquisition PLL enters Holdover mode or if the mode select pins or bits are set to

Holdover (MS2, MS1 = 01).

4.2

Software Control

Software control is enabled by setting the HW pin to logic zero (HW = 0). In this mode all hardware control pins

(inputs) are disabled and status bits (outputs) are enabled. The ZL30402 has seventeen registers that provide all

the functionality available in Hardware control and in addition they offer advanced control and monitoring that is

only available in Software control (see Figure 6 "Hardware and Software Control options").

4.2.1

Control Bits

The ZL30402 has seven control bits as is shown in Figure 6 "Hardware and Software Control options". The first five

bits replace the five hardware control pins: MS2, MS1, FCS, RefSel and RefAlign and the last two bits support

recovery from Auto Holdover mode: AHRD and MHR. These bits are described in section 3.2.4.

In addition to the Control bits shown in Figure 6 "Hardware and Software Control options", the ZL30402 has a

number of bits and registers that are accessed infrequently or during configuration only e.g., Phase Offset

Adjustment or Master Clock Frequency Calibration.

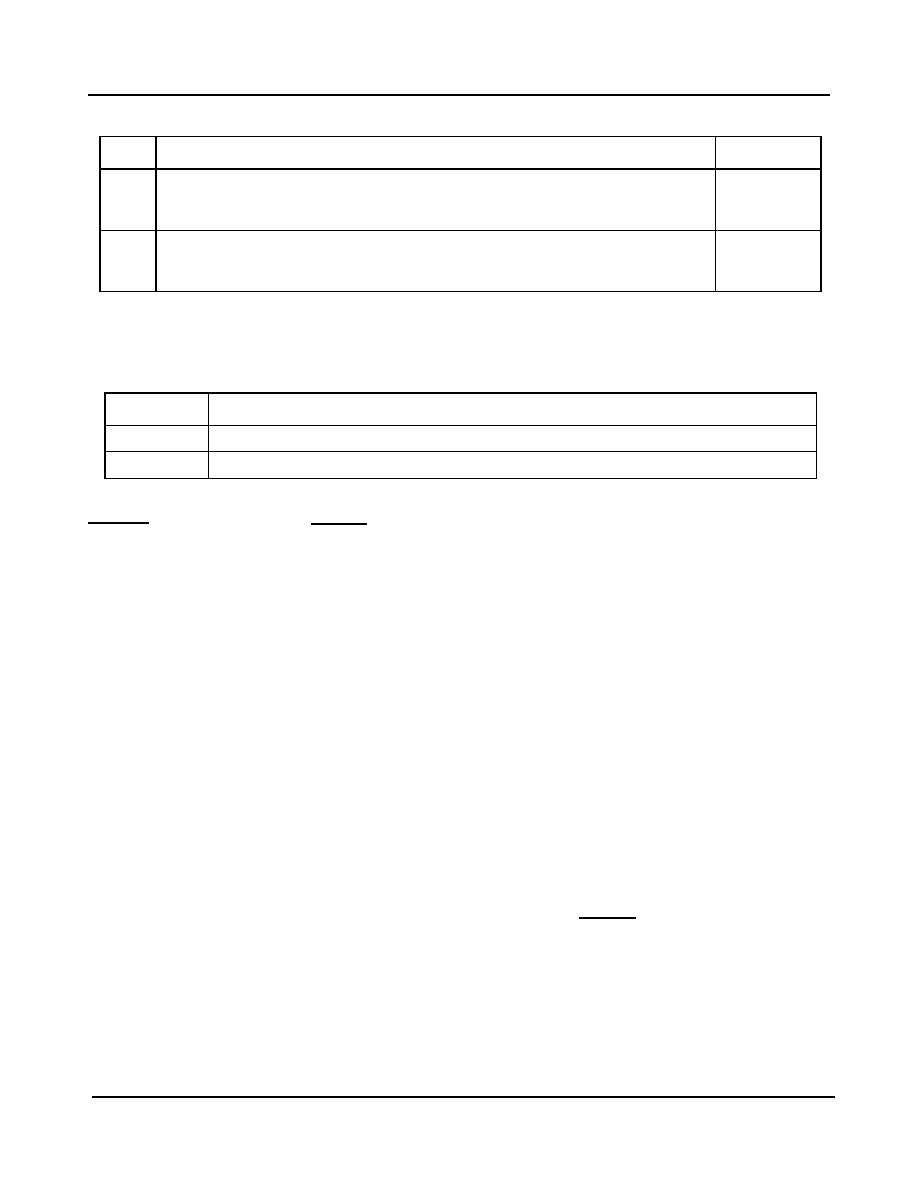

FCS

Filtering Characteristic

Phase Slope

0

Filter corner frequency set to 1.1 Hz.

This selection meets requirements of G.813 Option 1 and GR-1244 stratum 3

clocks.

41ns

in 1.326ms

1

Filter corner frequency set to 0.1 Hz.

This selection meets requirements of G.813 Option 2, GR-253 for SONET stratum 3

and GR-253 for SONET Minimum Clocks (SMC).

885ns/s

Table 2 - Filter Characteristic Selection

RefSel

Input Reference

0

Core PLL connected to the Primary Acquisition PLL

1

Core PLL connected to the Secondary Acquisition PLL

Table 3 - Reference Source Select

相关PDF资料 |

PDF描述 |

|---|---|

| ZL50112GAG2 | SPECIALTY TELECOM CIRCUIT, PBGA552 |

| ZL50112GAG | SPECIALTY TELECOM CIRCUIT, PBGA552 |

| ZL50114GAG2 | SPECIALTY TELECOM CIRCUIT, PBGA552 |

| ZL50114GAG | SPECIALTY TELECOM CIRCUIT, PBGA552 |

| ZL50232GD | DATACOM, ISDN ECHO CANCELLER, PBGA208 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ZL30406 | 制造商:ZARLINK 制造商全称:Zarlink Semiconductor Inc 功能描述:SONET/SDH Clock Multiplier PLL |

| ZL30406_06 | 制造商:ZARLINK 制造商全称:Zarlink Semiconductor Inc 功能描述:SONET/SDH Clock Multiplier PLL |

| ZL30406QGC | 制造商:Zarlink Semiconductor Inc 功能描述:PLL CLOCK MLTPLR SGL UP TO 19.44MHZ 64TQFP - Trays |

| ZL30406QGC1 | 制造商:ZARLINK 制造商全称:Zarlink Semiconductor Inc 功能描述:SONET/SDH Clock Multiplier PLL |

| ZL30406QGG1 | 制造商:Microsemi Corporation 功能描述:IC PB FREE T1/E1 SYS. SYNC+STRATUM 3 H/O 制造商:Microsemi Corporation 功能描述:PB FREE SONET/SDH CLOCK MULTIPLIER PLL - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC PLL SONET/SDH CLK MULT 64TQFP 制造商:Microsemi Corporation 功能描述:IC PLL SONET/SDH CLK MULT 64TQFP |

发布紧急采购,3分钟左右您将得到回复。