- 您现在的位置:买卖IC网 > PDF目录300164 > ZL30402/QCG1 (ZARLINK SEMICONDUCTOR INC) ATM/SONET/SDH SUPPORT CIRCUIT, PQFP80 PDF资料下载

参数资料

| 型号: | ZL30402/QCG1 |

| 厂商: | ZARLINK SEMICONDUCTOR INC |

| 元件分类: | 数字传输电路 |

| 英文描述: | ATM/SONET/SDH SUPPORT CIRCUIT, PQFP80 |

| 封装: | 14 X 14 MM, 1.40 MM HEIGHT, LEAD FREE, MS-026BEC, LQFP-80 |

| 文件页数: | 4/44页 |

| 文件大小: | 472K |

| 代理商: | ZL30402/QCG1 |

第1页第2页第3页当前第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

ZL30402

Data Sheet

12

Zarlink Semiconductor Inc.

2.2

Core PLL

The most critical element of the ZL30402 is its Core PLL, which generates a phase-locked clock, filters jitter and

wander and suppresses input phase transients. All of these features are in agreement with international standards:

- G.813 Option 1 and 2 clocks for SDH equipment

- GR-253 for SONET stratum 3 and SONET Minimum Clocks (SMC)

- GR-1244 for stratum 3 Clocks

The Core PLL supports three mandatory modes of operation: Free-run, Normal (Locked) and Holdover. Each of

these modes places specific requirements on the building blocks of the Core PLL.

- In Free-run Mode, the Core PLL locks to the 20 MHz Master Clock Oscillator connected to pin C20i. The

stability of the generated clock remains the same as the stability of the Master Clock Oscillator but frequency

accuracy is greatly improved by the Master Clock Frequency Calibration register. This register compensates

oscillator frequency, practically eliminating manufacturing tolerances.

- In Normal Mode, the Core PLL locks to one of the Acquisition PLLs. Both Acquisition PLLs provide

preprocessed phase data to the Core PLL including detection of reference clock quality. This preprocessing

reduces the load on the Core PLL and improves quality of the generated clock.

- In Holdover mode, the Core PLL generates a clock based on data collected from past reference signals. The

Core PLL enters Holdover mode if the attached Acquisition PLL switches into the Holdover state or under

external software or hardware control.

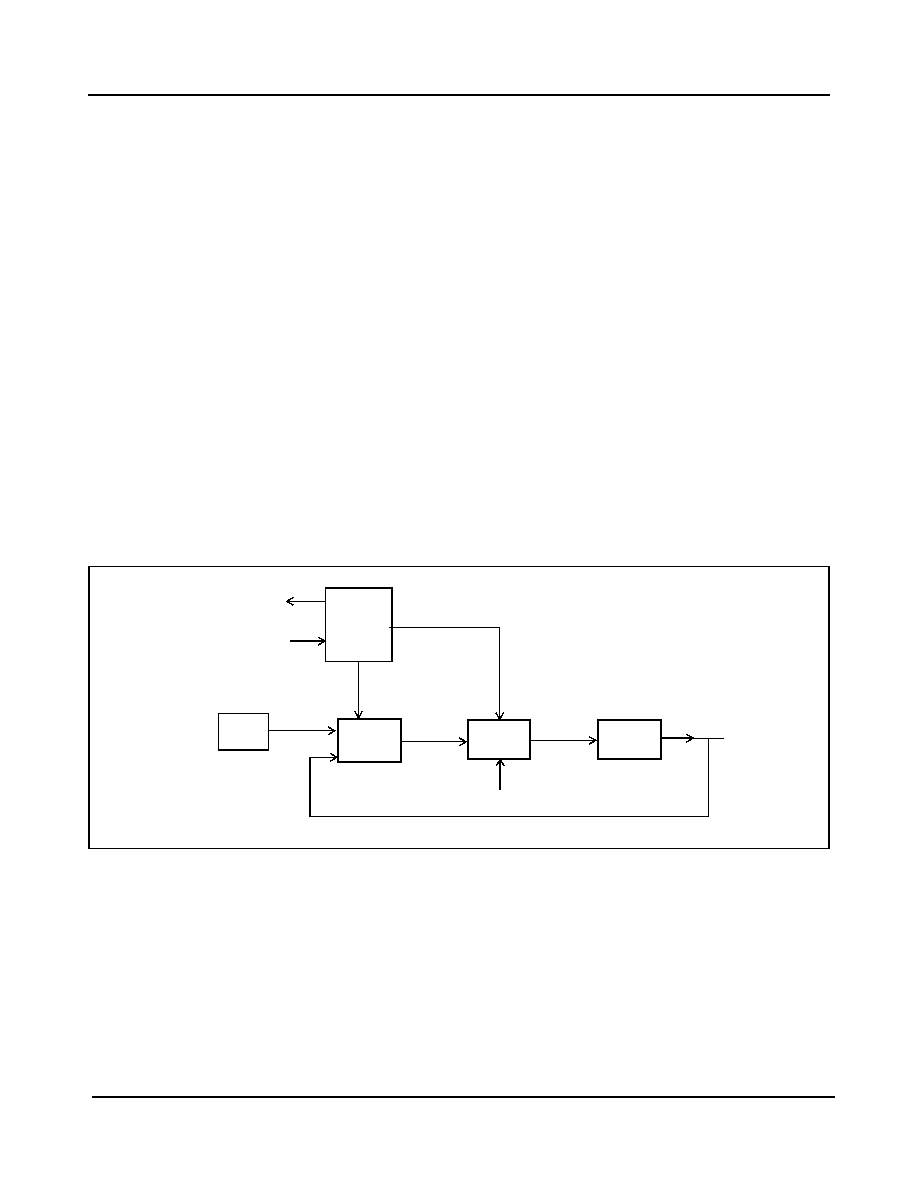

Some of the key elements of the Core PLL are shown in Figure 3 "Core PLL Functional Block Diagram".

Figure 3 - Core PLL Functional Block Diagram

Digitally Controlled Oscillator (DCO): The DCO is an arithmetic unit that continuously generates a stream of

numbers that represent the phase-locked clock. These numbers are passed to the Clock Synthesizer (see

section 2.3) where they are converted into electrical clock signals of different frequencies.

Filters: In Normal mode, the clock generated by the DCO is phase-locked to the input reference signal and band-

limited to meet network synchronization standards. The ZL30402 provides two software programmable (Control

Reg 1) and two hardware selectable (FCS pin) filtering options. The filtering characteristics are similar to a first

order low pass filter with corner frequencies that support international standards:

- 0.1 Hz filter: supports G.813 Option 2 Clock, GR-253 SONET stratum 3 and GR-253 SONET Minimum clock

- 1.1 Hz filter: supports G.813 Option 1 and GR-1244 stratum 3 clock

FSM

DCO

Filters

Phase

Detector

MUX

LOCK

RefAlign

FCS

相关PDF资料 |

PDF描述 |

|---|---|

| ZL50112GAG2 | SPECIALTY TELECOM CIRCUIT, PBGA552 |

| ZL50112GAG | SPECIALTY TELECOM CIRCUIT, PBGA552 |

| ZL50114GAG2 | SPECIALTY TELECOM CIRCUIT, PBGA552 |

| ZL50114GAG | SPECIALTY TELECOM CIRCUIT, PBGA552 |

| ZL50232GD | DATACOM, ISDN ECHO CANCELLER, PBGA208 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ZL30406 | 制造商:ZARLINK 制造商全称:Zarlink Semiconductor Inc 功能描述:SONET/SDH Clock Multiplier PLL |

| ZL30406_06 | 制造商:ZARLINK 制造商全称:Zarlink Semiconductor Inc 功能描述:SONET/SDH Clock Multiplier PLL |

| ZL30406QGC | 制造商:Zarlink Semiconductor Inc 功能描述:PLL CLOCK MLTPLR SGL UP TO 19.44MHZ 64TQFP - Trays |

| ZL30406QGC1 | 制造商:ZARLINK 制造商全称:Zarlink Semiconductor Inc 功能描述:SONET/SDH Clock Multiplier PLL |

| ZL30406QGG1 | 制造商:Microsemi Corporation 功能描述:IC PB FREE T1/E1 SYS. SYNC+STRATUM 3 H/O 制造商:Microsemi Corporation 功能描述:PB FREE SONET/SDH CLOCK MULTIPLIER PLL - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC PLL SONET/SDH CLK MULT 64TQFP 制造商:Microsemi Corporation 功能描述:IC PLL SONET/SDH CLK MULT 64TQFP |

发布紧急采购,3分钟左右您将得到回复。