- 您现在的位置:买卖IC网 > PDF目录300164 > ZL30402/QCG1 (ZARLINK SEMICONDUCTOR INC) ATM/SONET/SDH SUPPORT CIRCUIT, PQFP80 PDF资料下载

参数资料

| 型号: | ZL30402/QCG1 |

| 厂商: | ZARLINK SEMICONDUCTOR INC |

| 元件分类: | 数字传输电路 |

| 英文描述: | ATM/SONET/SDH SUPPORT CIRCUIT, PQFP80 |

| 封装: | 14 X 14 MM, 1.40 MM HEIGHT, LEAD FREE, MS-026BEC, LQFP-80 |

| 文件页数: | 19/44页 |

| 文件大小: | 472K |

| 代理商: | ZL30402/QCG1 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

ZL30402

Data Sheet

26

Zarlink Semiconductor Inc.

Address: 1A H

Address: 20 H

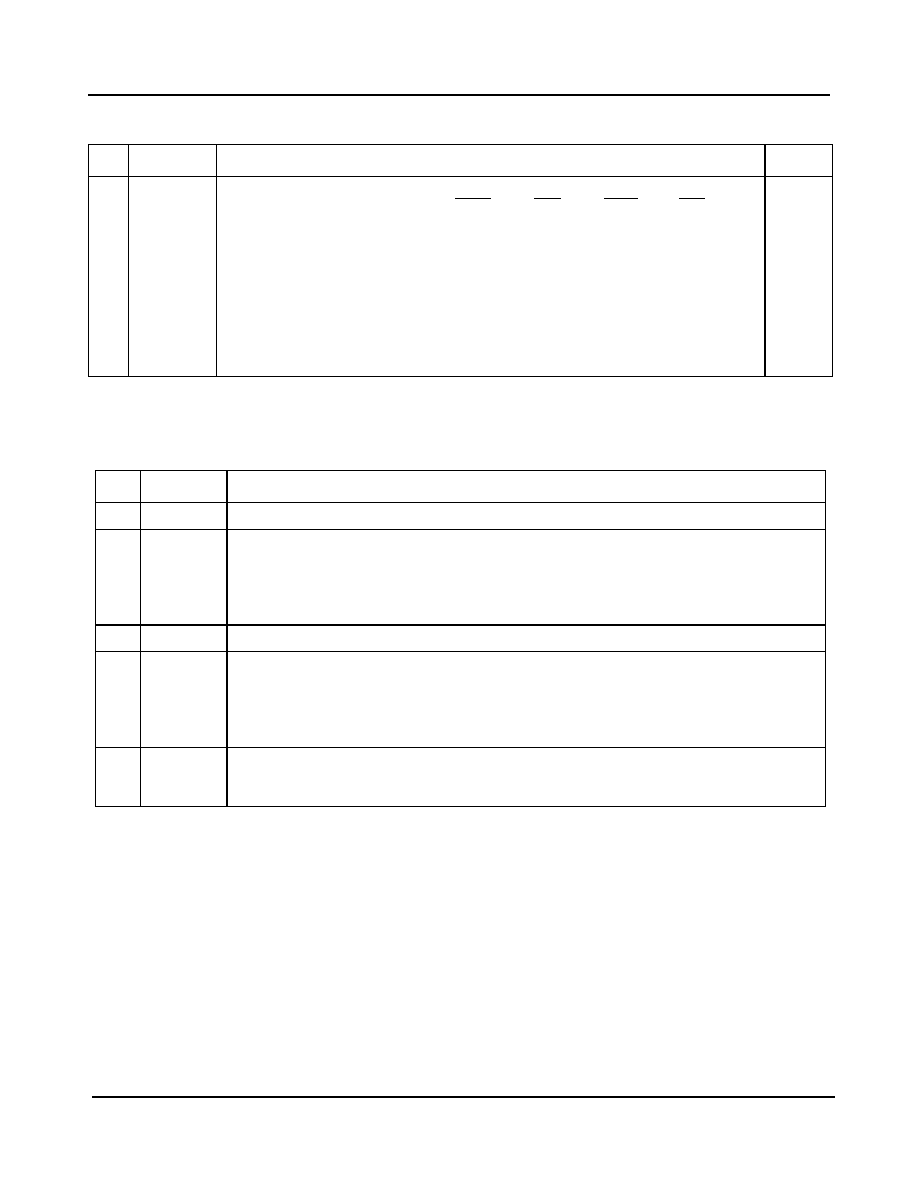

Bit

Name

Functional Description

Default

7-0

FPOA7 - 0

Fine Phase Offset Adjustment. This register allows phase offset adjustment of

all output clocks and frame pulses (C16o, C8o, C4o, C2o, F16o, F8o, F0o, C155,

C19o, C34/44, C1.5o, C6o) relative to the active input reference. The adjustment

can be positive (advance) or negative (delay) with a nominal step size of 477 ps

(61.035 ns / 128). The rate of phase change is limited to 885 ns/s for FCS = 1 and

41 ns in 1.326 ms for FCS = 0 selections. The phase offset value is a signed 2’s

complement number e.g.:

Advance: +1 step = 01H, +2 steps = 02H, +127 steps = EFH

Delay: -1 step = FFH, -2 steps = FEH, -128 steps = 80H

Example: Writing 08H advances all clocks by 3.8 ns and writing F3H delays all

clocks

00000

000

Table 15 - Fine Phase Offset Register (R/W)

Bit

Name

Functional Description

7-5

RSV

Reserved.

4-3

InpFreq1-

0

Input Frequency. These two bits identify the Primary Reference Clock frequency.

- 00 = 19.44 MHz

- 01 = 8 kHz

- 10 = 1.544 MHz

- 11 = 2.048 MHz

2RSV

Reserved.

1PAH

Primary Acquisition PLL Holdover. This bit goes high whenever the Acquisition PLL

enters Holdover mode. Holdover mode is entered when the reference frequency is

- lost completely

- drifts more than ±30 000 ppm off from the nominal frequency

- a large phase hit occurs on the reference clock.

0PAFL

Primary Acquisition PLL Frequency Limit. This bit goes high whenever the Acquisition

PLL exceeds its capture range of ±104 ppm. This bit can flicker high in the event of a large

excursion of still tolerable input jitter.

Table 16 - Primary Acquisition PLL Status Register (R)

相关PDF资料 |

PDF描述 |

|---|---|

| ZL50112GAG2 | SPECIALTY TELECOM CIRCUIT, PBGA552 |

| ZL50112GAG | SPECIALTY TELECOM CIRCUIT, PBGA552 |

| ZL50114GAG2 | SPECIALTY TELECOM CIRCUIT, PBGA552 |

| ZL50114GAG | SPECIALTY TELECOM CIRCUIT, PBGA552 |

| ZL50232GD | DATACOM, ISDN ECHO CANCELLER, PBGA208 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ZL30406 | 制造商:ZARLINK 制造商全称:Zarlink Semiconductor Inc 功能描述:SONET/SDH Clock Multiplier PLL |

| ZL30406_06 | 制造商:ZARLINK 制造商全称:Zarlink Semiconductor Inc 功能描述:SONET/SDH Clock Multiplier PLL |

| ZL30406QGC | 制造商:Zarlink Semiconductor Inc 功能描述:PLL CLOCK MLTPLR SGL UP TO 19.44MHZ 64TQFP - Trays |

| ZL30406QGC1 | 制造商:ZARLINK 制造商全称:Zarlink Semiconductor Inc 功能描述:SONET/SDH Clock Multiplier PLL |

| ZL30406QGG1 | 制造商:Microsemi Corporation 功能描述:IC PB FREE T1/E1 SYS. SYNC+STRATUM 3 H/O 制造商:Microsemi Corporation 功能描述:PB FREE SONET/SDH CLOCK MULTIPLIER PLL - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC PLL SONET/SDH CLK MULT 64TQFP 制造商:Microsemi Corporation 功能描述:IC PLL SONET/SDH CLK MULT 64TQFP |

发布紧急采购,3分钟左右您将得到回复。