- 您现在的位置:买卖IC网 > PDF目录300164 > ZL30402/QCG1 (ZARLINK SEMICONDUCTOR INC) ATM/SONET/SDH SUPPORT CIRCUIT, PQFP80 PDF资料下载

参数资料

| 型号: | ZL30402/QCG1 |

| 厂商: | ZARLINK SEMICONDUCTOR INC |

| 元件分类: | 数字传输电路 |

| 英文描述: | ATM/SONET/SDH SUPPORT CIRCUIT, PQFP80 |

| 封装: | 14 X 14 MM, 1.40 MM HEIGHT, LEAD FREE, MS-026BEC, LQFP-80 |

| 文件页数: | 22/44页 |

| 文件大小: | 472K |

| 代理商: | ZL30402/QCG1 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页当前第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

ZL30402

Data Sheet

29

Zarlink Semiconductor Inc.

5.1.2

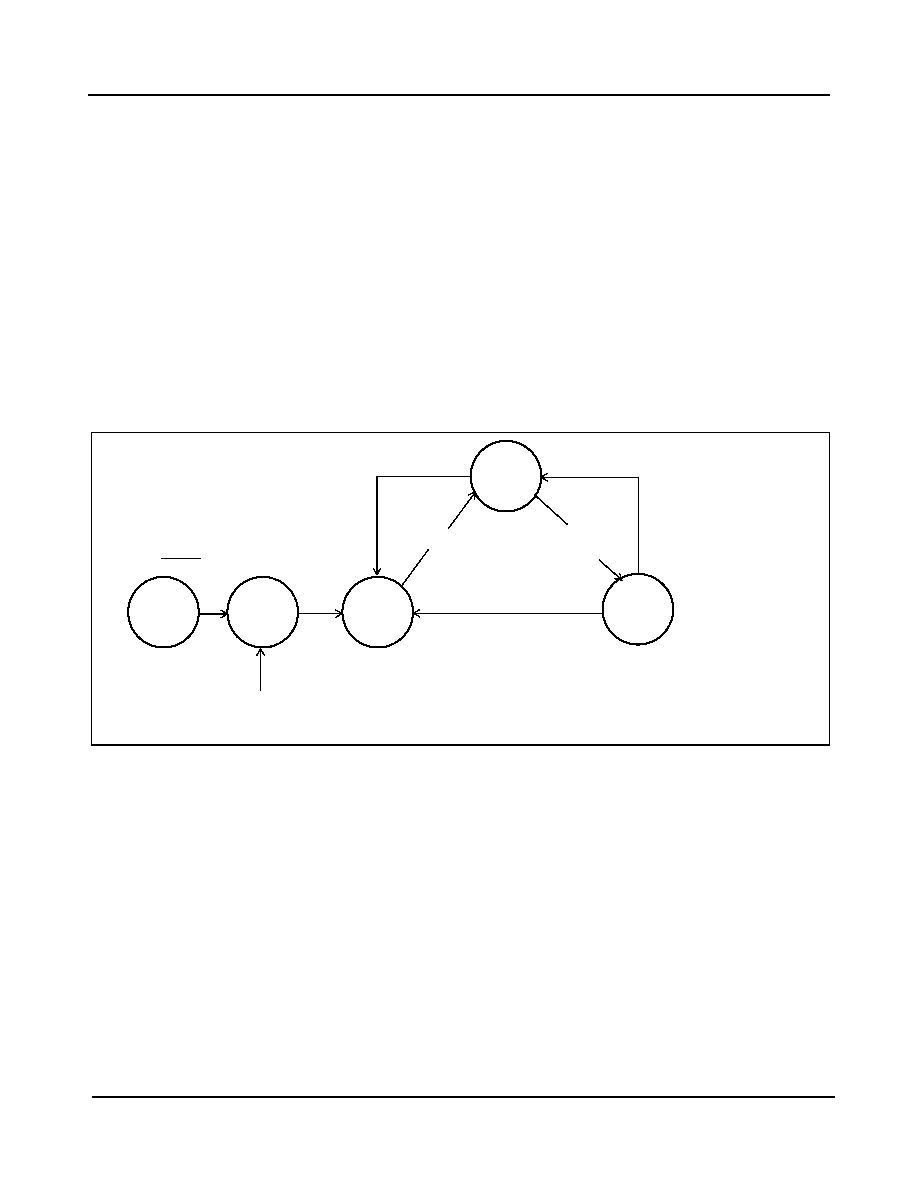

Single Reference Operation: NORMAL --> AUTO HOLDOVER --> NORMAL

The NORMAL to AUTO-HOLDOVER to NORMAL transition will usually happen when the Network Element loses

its single reference clock unexpectedly or when it has two references but switching to the secondary reference is

not a desirable option (unless primary reference is lost without chance of quick recovery).

The sequence starts with the unexpected failure of a reference signal shown as transition OK --> FAIL in Figure 7

"Transition from Free-Run to Normal Mode" at a time when ZL30402 operates in Normal mode. This failure is

detected by the active Acquisition PLL based on the following FAIL criteria:

Frequency offset on 8 kHz, 1.544 MHz, 2.048 MHz and 19.44 MHz reference clocks exceeds ±30000 ppm

(±3%).

Single phase hit on 1.544 MHz, 2.048 MHz and 19.44 MHz exceeds half of the cycle of the reference clock.

After detecting any of these anomalies on a reference clock the Acquisition PLL will switch itself into Holdover mode

forcing the Core PLL to automatically switch into the Auto Holdover state. This condition is flagged by LOCK = 0

and HOLDOVER = 1.

Figure 8 - Automatic Entry into Auto Holdover State and Eecovery into Normal mode

There are two possible returns to Normal mode after the reference signal is restored:

With the AHRD (Automatic Holdover Return Disable) bit set to 0. In this case the Core PLL will automatically

return to the Normal state after the reference signal recovers from failure. This transition is shown on the

state diagram as a FAIL --> OK change. This change becomes effective when the reference is restored and

there have been no phase hits detected for at least 64 clock cycles for 1.544/2.048 MHz reference, 512

clock cycles for 19.44 MHz reference and 1 clock cycle for 8 kHz reference.

With the AHRD bit set to high to disable automatic return to Normal and the change of MHR (Manual

Holdover Release) bit from 0 to 1 to trigger the transition from Auto Holdover to Normal. This option is

provided to protect the Core PLL against toggling between Normal and Auto Holdover states in case of an

intermittent quality reference clock. In the case when MHR has been changed when the reference is still not

available (Acquisition PLL in Holdover mode) the transition to Normal state will not occur and MHR 0 to 1

transition must be repeated.

This transition from Auto Holdover to Normal mode is performed as “hitless” reference switching.

NORMAL

(LOCKED)

00

AUTO

HOLD-

OVER

HOLD-

OVER

01

FREE-

RUN

10

RESET

Ref: OK &

MS2, MS1 == 00

{AUTO}

Ref: OK --> FAIL &

MS2, MS1 == 00

{AUTO}

MS2, MS1 == 01 OR

RefSel change

Ref: FAIL --> OK &

MS2, MS1 == 00 &

AHRD=1 &

MHR=0 -->1 then 1-->0

{MANUAL}

Ref: FAIL --> OK &

MS2, MS1 == 00 &

AHRD=0

{AUTO}

MS2, MS1 == 10 forces

unconditional return from

any state to Free-run

MS2, MS1! = 10

RESET == 1

RefSel Change

Automatic return to NORMAL: AHRD=0

OR

Manual return to NORMAL: AHRD=1 & MHR= 0-->1 then 1-->0

相关PDF资料 |

PDF描述 |

|---|---|

| ZL50112GAG2 | SPECIALTY TELECOM CIRCUIT, PBGA552 |

| ZL50112GAG | SPECIALTY TELECOM CIRCUIT, PBGA552 |

| ZL50114GAG2 | SPECIALTY TELECOM CIRCUIT, PBGA552 |

| ZL50114GAG | SPECIALTY TELECOM CIRCUIT, PBGA552 |

| ZL50232GD | DATACOM, ISDN ECHO CANCELLER, PBGA208 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ZL30406 | 制造商:ZARLINK 制造商全称:Zarlink Semiconductor Inc 功能描述:SONET/SDH Clock Multiplier PLL |

| ZL30406_06 | 制造商:ZARLINK 制造商全称:Zarlink Semiconductor Inc 功能描述:SONET/SDH Clock Multiplier PLL |

| ZL30406QGC | 制造商:Zarlink Semiconductor Inc 功能描述:PLL CLOCK MLTPLR SGL UP TO 19.44MHZ 64TQFP - Trays |

| ZL30406QGC1 | 制造商:ZARLINK 制造商全称:Zarlink Semiconductor Inc 功能描述:SONET/SDH Clock Multiplier PLL |

| ZL30406QGG1 | 制造商:Microsemi Corporation 功能描述:IC PB FREE T1/E1 SYS. SYNC+STRATUM 3 H/O 制造商:Microsemi Corporation 功能描述:PB FREE SONET/SDH CLOCK MULTIPLIER PLL - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC PLL SONET/SDH CLK MULT 64TQFP 制造商:Microsemi Corporation 功能描述:IC PLL SONET/SDH CLK MULT 64TQFP |

发布紧急采购,3分钟左右您将得到回复。