- 您现在的位置:买卖IC网 > PDF目录11767 > AD9882KSTZ-100 (Analog Devices Inc)IC INTERFACE/DVI 100MHZ 100LQFP PDF资料下载

参数资料

| 型号: | AD9882KSTZ-100 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 5/40页 |

| 文件大小: | 0K |

| 描述: | IC INTERFACE/DVI 100MHZ 100LQFP |

| 标准包装: | 1 |

| 应用: | 视频 |

| 接口: | 模拟,DVI |

| 电源电压: | 3.15 V ~ 3.45 V |

| 封装/外壳: | 100-LQFP |

| 供应商设备封装: | 100-LQFP(14x14) |

| 包装: | 管件 |

| 安装类型: | 表面贴装 |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

AD9882A

Rev. 0 | Page 13 of 40

THEORY OF OPERATION AND DESIGN GUIDE: ANALOG INTERFACE

GENERAL DESCRIPTION

The AD9882A is a fully integrated solution for capturing analog

RGB signals and digitizing them for display on flat panel moni-

tors or projectors. The device is ideal for implementing a com-

puter interface for HDTV monitors or as the front end to high

performance video scan converters.

Implemented in a high performance CMOS process, the inter-

face can capture signals with pixel rates of up to 140 MHz.

The AD9882A includes all necessary input buffering, signal dc

restoration (clamping), offset and gain (brightness and contrast)

adjustment, pixel clock generation, sampling phase control, and

output data formatting. All controls are programmable via a

2-wire serial interface. Full integration of these sensitive analog

functions makes the system design straightforward and less

sensitive to the physical and electrical environment.

With a typical power dissipation of only 875 mW and an oper-

ating temperature range of 0°C to 70°C, the device requires no

special environmental considerations.

INPUT SIGNAL HANDLING

The AD9882A has three high impedance analog input pins for

the red, green, and blue channels. They will accommodate

signals ranging from 0.5 V to 1.0 V p-p.

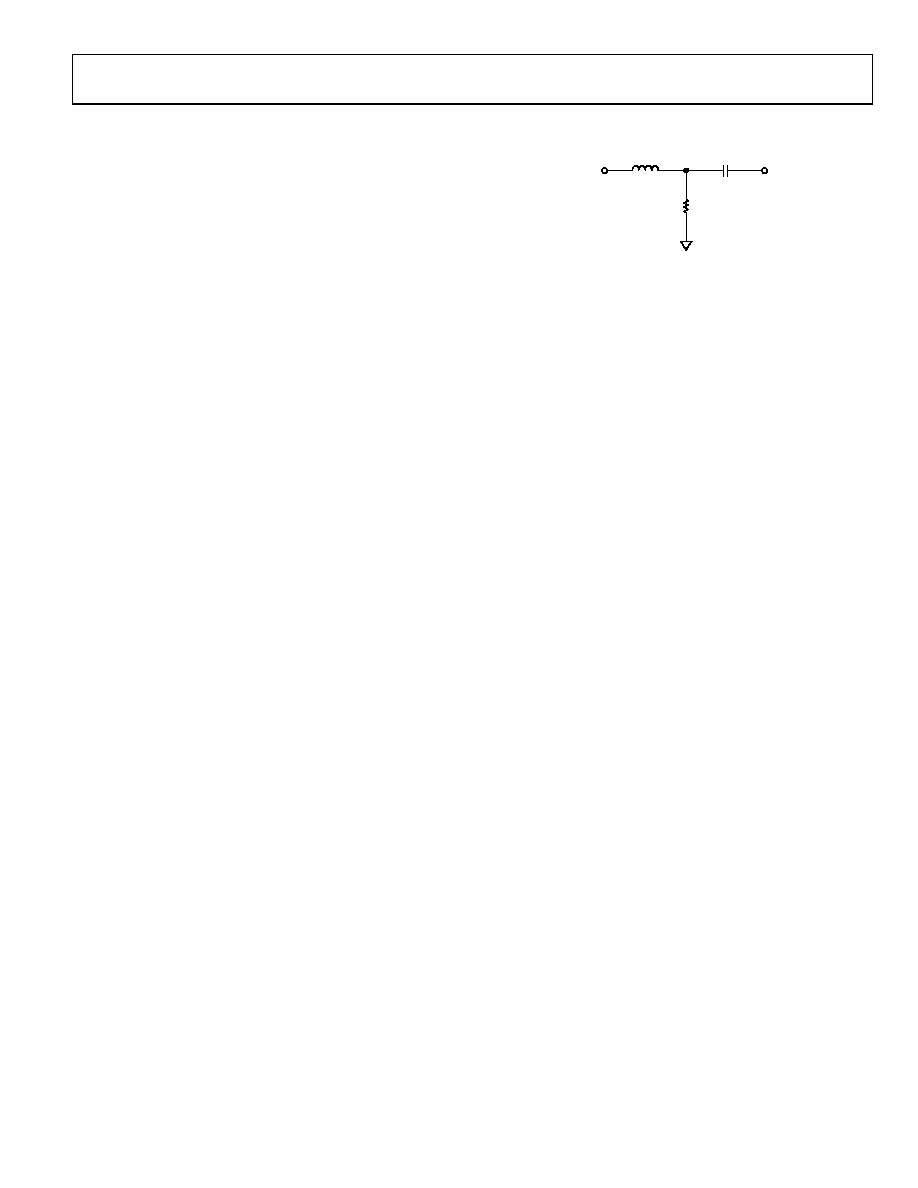

Signals are typically brought onto the interface board via a

DVI-I connector, a 15-pin D connector, or BNC connectors.

The AD9882A should be located as close as practical to the

input connector. Signals should be routed via matched-

impedance traces (normally 75 ) to the IC input pins.

At that point, the signal should be resistively terminated (75

to the signal ground return) and capacitively coupled to the

AD9882A inputs through 47 nF capacitors. These capacitors

form part of the dc restoration circuit (see Figure 9).

In an ideal world of perfectly matched impedances, the best

performance can be obtained with the widest possible signal

bandwidth. The wide bandwidth inputs of the AD9882A

(300 MHz) can track the input signal continuously as it moves

from one pixel level to the next and digitize the pixel during a

long, flat pixel time. In many systems, however, there are

mismatches, reflections, and noise, which can result in excessive

ringing and distortion of the input waveform. This makes it

more difficult to establish a sampling phase that provides good

image quality. It has been shown that a small inductor in series

with the input is effective in rolling off the input bandwidth

slightly and providing a high quality signal over a wider range

of conditions. Using a Fair-Rite #2508051217Z0 high speed

signal chip bead inductor in the circuit of Figure 9 gives good

results in most applications.

05123-003

RGB

INPUT

RAIN

GAIN

BAIN

47nF

75

Figure 3. Analog Input Interface Circuit

HSYNC AND VSYNC INPUTS

The AD9882A receives a horizontal sync signal and uses it to

generate the pixel clock and clamp timing. This can be either a

sync signal directly from the graphics source or a preprocessed

TTL or CMOS level signal.

The Hsync input includes a Schmitt trigger buffer and is

capable of handling signals with long rise times, with superior

noise immunity. In typical PC-based graphic systems, the sync

signals are simply TTL level drivers, feeding unshielded wires in

the monitor cable. As such, no termination is required.

SERIAL CONTROL PORT

The serial control port is designed for 3.3 V logic. If there are

5 V drivers on the bus, these pins should be protected with

150 series resistors placed between the pull-up resistors and

the input pins.

OUTPUT SIGNAL HANDLING

The digital outputs are designed and specified to operate from a

3.3 V power supply (VDD). They can also work with a VDD as low

as 2.5 V for compatibility with other 2.5 V logic.

CLAMPING

RGB Clamping

To properly digitize the incoming signal, the dc offset of the

input must be adjusted to fit the range of the on-board ADCs.

Most graphics systems produce RGB signals with black at

ground and white at approximately 0.75 V. However, if sync

signals are embedded in the graphics, the sync tip is often at

ground, and black is at 300 mV; white will be approximately

1.0 V. Some common RGB line amplifier boxes use emitter-

follower buffers to split signals and increase drive capability.

This introduces a 700 mV dc offset to the signal, which is

removed by clamping for proper capture by the AD9882A.

The key to clamping is to identify a portion (time) of the signal

when the graphics system is known to be producing black.

Originating from CRT displays, the electron beam is blanked by

sending a black level during horizontal retrace to prevent

disturbing the image. Most graphics systems maintain this

format of sending a black level between active video lines.

相关PDF资料 |

PDF描述 |

|---|---|

| MS27473E16B55PA | CONN PLUG 55POS STRAIGHT W/PINS |

| LTC4305IGN#TR | IC BUFFER BUS 2WR ADDRESS 16SSOP |

| VI-B43-IW-F2 | CONVERTER MOD DC/DC 24V 100W |

| AD9983AKCPZ-170 | IC INTRFACE 8BIT 170MSPS 64LFCSP |

| VI-B42-IX-F4 | CONVERTER MOD DC/DC 15V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9882KSTZ-140 | 功能描述:IC INTERFACE/DVI 100MHZ 100LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:- 特色产品:NXP - I2C Interface 标准包装:1 系列:- 应用:2 通道 I²C 多路复用器 接口:I²C,SM 总线 电源电压:2.3 V ~ 5.5 V 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:剪切带 (CT) 安装类型:表面贴装 产品目录页面:825 (CN2011-ZH PDF) 其它名称:568-1854-1 |

| AD9883 | 制造商:AD 制造商全称:Analog Devices 功能描述:110 MSPS Analog Interface for Flat Panel Displays |

| AD9883/PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:110 MSPS Analog Interface for Flat Panel Displays |

| AD9883A | 制造商:AD 制造商全称:Analog Devices 功能描述:110 MSPS/140 MSPS Analog Interface for Flat Panel Displays |

| AD9883A/PCB | 制造商:Analog Devices 功能描述:110MHZ ANALOG INTERFACE FOR SG |

发布紧急采购,3分钟左右您将得到回复。