- 您现在的位置:买卖IC网 > PDF目录1894 > AD9887AKSZ-140 (Analog Devices Inc)IC INTRFACE ANALOG/DVI 160-MQFP PDF资料下载

参数资料

| 型号: | AD9887AKSZ-140 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 16/52页 |

| 文件大小: | 0K |

| 描述: | IC INTRFACE ANALOG/DVI 160-MQFP |

| 标准包装: | 24 |

| 应用: | 图形卡,VGA 接口 |

| 接口: | 模拟和数字 |

| 电源电压: | 3.15 V ~ 3.45 V |

| 封装/外壳: | 160-BQFP |

| 供应商设备封装: | 160-MQFP(28x28) |

| 包装: | 托盘 |

| 安装类型: | 表面贴装 |

| 产品目录页面: | 788 (CN2011-ZH PDF) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页

AD9887A

Rev. B | Page 23 of 52

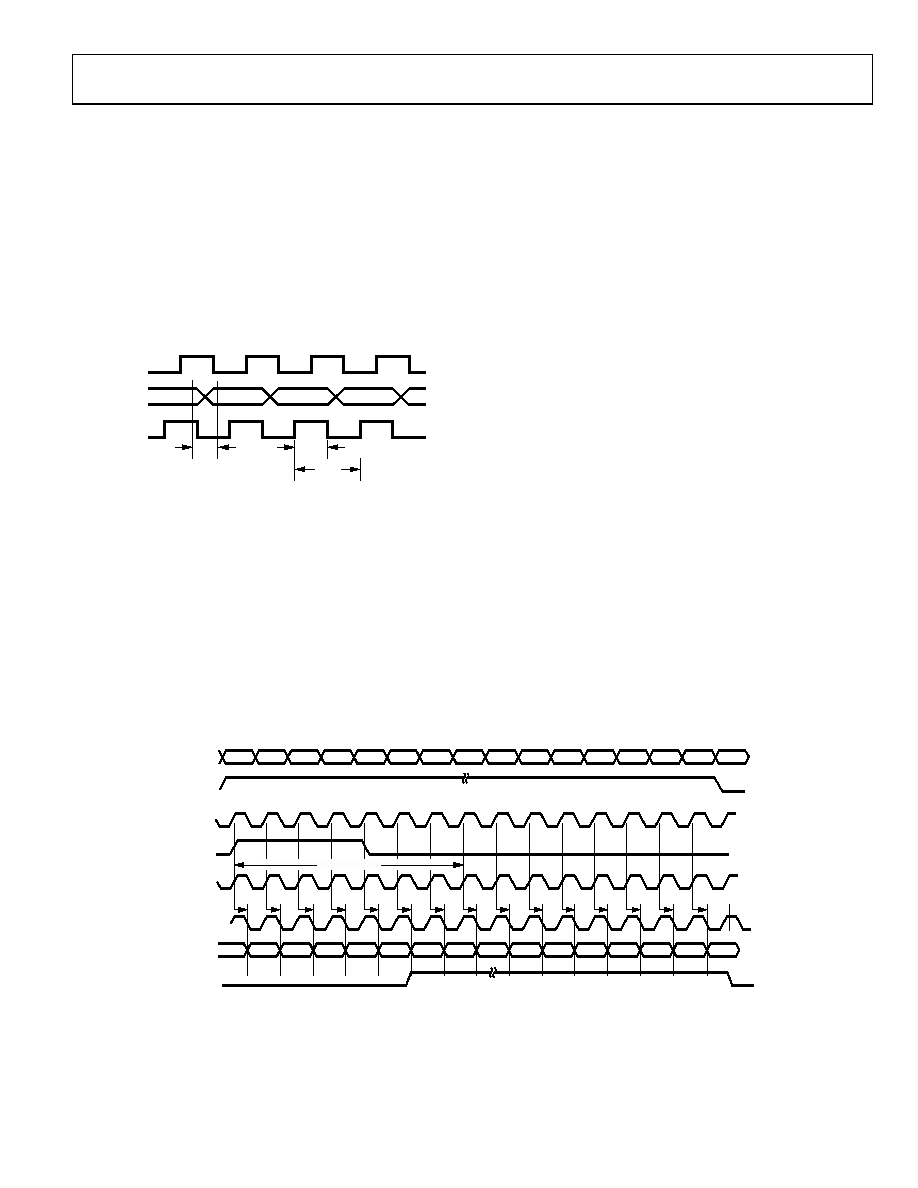

TIMING—ANALOG INTERFACE

Three things happen to Hsync in the AD9887A. First, the polarity

of the HSYNC input is determined and, thus, has a known output

polarity. The known output polarity can be programmed either

active high or active low (Register 0x04, Bit 4). Second, HSOUT

is aligned with DATACK and data outputs. Third, the duration

of HSOUT (in pixel clocks) is set via Register 0x07. Use the

HSOUT signal to drive the rest of the display system.

operation of the AD9887A analog interface in all clock modes.

The part establishes timing by sending the pixel corresponding

with the leading edge of Hsync to Data Port A. In dual-channel

mode, the next sample is sent to Data Port B. Subsequent samples

are alternated between the A and B data ports. In single-channel

mode, data is only sent to Data Port A, and Data Port B is placed

in a high impedance state.

Coast Timing

In most computer systems, the Hsync signal is provided

continuously on a dedicated wire. In these systems, the coast

input and function are unnecessary and should not be used.

In some systems, however, Hsync is disturbed during the vertical

sync (Vsync) period, and sometimes Hsync pulses disappear.

In other systems, such as those that use composite sync (Csync)

signals or those that embed sync-on-green (SOG), Hsync includes

equalization pulses or other distortions during Vsync. To avoid

upsetting the clock generator during Vsync, it is important to

ignore these distortions. If the pixel clock PLL sees extraneous

pulses, it attempts to lock on to this new frequency and changes

frequency by the end of the Vsync period. It then requires a few

lines of correct Hsync timing to recover at the beginning of a new

frame, resulting in a tearing of the image at the top of the display.

The output data clock signal is created so that its rising edge

always occurs between transitions of Data Port A and can be

used to latch the output data externally.

PXCK

ANY OUTPUT

SIGNAL

DATACK

(OUTPUT)

tSKEW

tDCYCLE

tPER

DATA OUT

0

28

38

-0

19

Figure 17. Analog Output Timing

Hsync Timing

Horizontal sync is processed in the AD9887A to eliminate

ambiguity in the timing of the leading edge with respect to the

phase-delayed pixel clock and data.

The coast input is provided to eliminate this problem. It is an

asynchronous input that disables the PLL input and holds the

clock at its current frequency. The PLL can operate in this manner

for several lines without significant frequency drift.

The HSYNC input is used as a reference to generate the pixel

sampling clock. The sampling phase can be adjusted with respect

to Hsync through a full 360° in 32 steps via the phase adjust

register to optimize the pixel sampling time. Display systems

use Hsync to align memory and display write cycles; therefore,

it is important to have a stable timing relationship between the

HSYNC output (HSOUT) and data clock (DATACK).

Coast can be provided by the graphics controller, or it can be

internally generated by the AD9887A sync processing engine.

P0

P1

P2

P3

P4

P5

P6

P7

D1

D2

D3

D4

D5

D6

RGBIN

HSYNC

PXCK

HS

ADCCK

DATACK

DOUTA

HSOUT

02

83

8-

0

20

7-PIPE DELAY

Figure 18. Single-Channel Mode (Analog Interface)

相关PDF资料 |

PDF描述 |

|---|---|

| AD9888KSZ-170 | IC ANALOG INTRFC 170MSPS 128MQFP |

| AD9895KBCZRL | IC CCD SIGNAL PROC/GEN 64-CSPBGA |

| AD9910BSVZ-REEL | IC DDS 1GSPS 14BIT PAR 100TQFP |

| AD9911BCPZ-REEL7 | IC DDS 500MSPS DAC 10BIT 56LFCSP |

| AD9912ABCPZ | IC DDS 1GSPS DAC 14BIT 64LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9887AKSZ-1401 | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual Interface for Flat Panel Display |

| AD9887AKSZ-170 | 功能描述:IC INTRFACE ANALOG/DVI 160-MQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:- 特色产品:NXP - I2C Interface 标准包装:1 系列:- 应用:2 通道 I²C 多路复用器 接口:I²C,SM 总线 电源电压:2.3 V ~ 5.5 V 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:剪切带 (CT) 安装类型:表面贴装 产品目录页面:825 (CN2011-ZH PDF) 其它名称:568-1854-1 |

| AD9887AKSZ-170 | 制造商:Analog Devices 功能描述:IC DUAL DISPLAY INTERFACE |

| AD9887AKSZ-1701 | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual Interface for Flat Panel Display |

| AD9887APCB | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual Interface for Flat Panel Displays |

发布紧急采购,3分钟左右您将得到回复。