- 您现在的位置:买卖IC网 > PDF目录19504 > ADSP-21363KSWZ-1AA (Analog Devices Inc)IC DSP 32BIT 333MHZ EPAD 144LQFP PDF资料下载

参数资料

| 型号: | ADSP-21363KSWZ-1AA |

| 厂商: | Analog Devices Inc |

| 文件页数: | 26/60页 |

| 文件大小: | 0K |

| 描述: | IC DSP 32BIT 333MHZ EPAD 144LQFP |

| 产品培训模块: | SHARC Processor Overview |

| 标准包装: | 1 |

| 系列: | SHARC® |

| 类型: | 浮点 |

| 接口: | DAI,SPI |

| 时钟速率: | 333MHz |

| 非易失内存: | ROM(512 kB) |

| 芯片上RAM: | 384kB |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 1.20V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 144-LQFP 裸露焊盘 |

| 供应商设备封装: | 144-LQFP(20x20) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页当前第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页

�� �

�

�

�ADSP-21362/ADSP-21363/ADSP-21364/ADSP-21365/ADSP-21366�

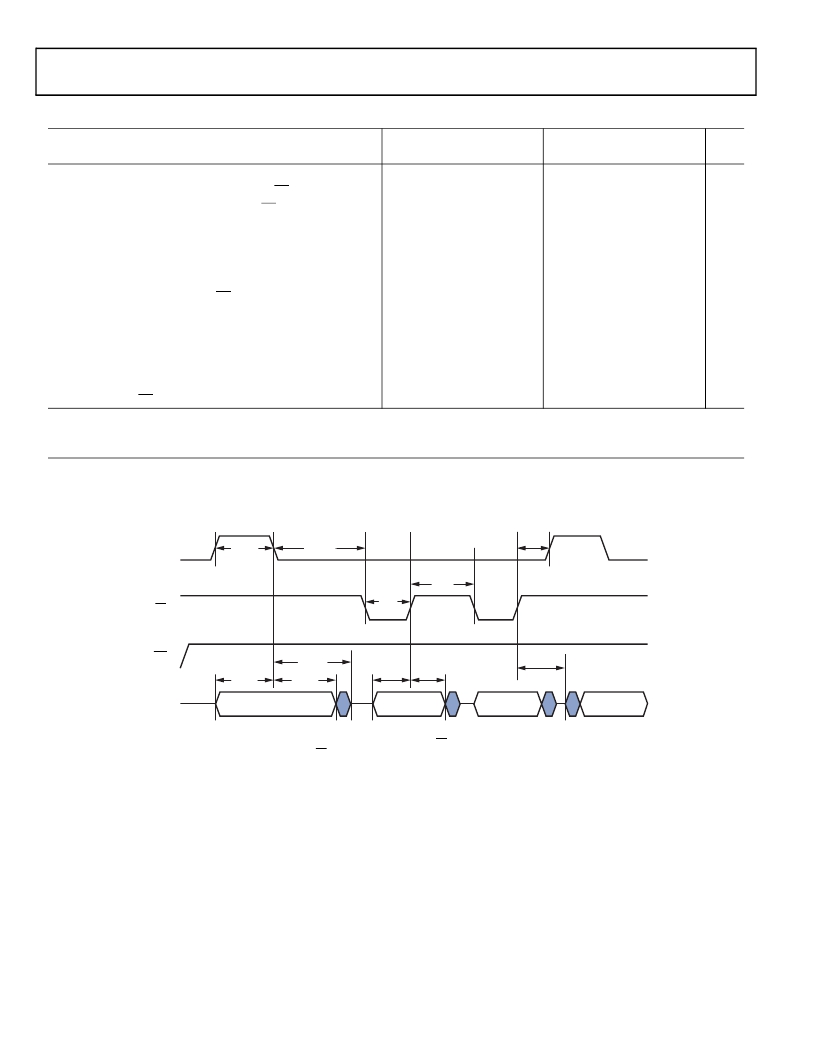

�Table� 21.� 16-Bit� Memory� Read� Cycle�

�K� and� B� Grade�

�Y� Grade�

�Parameter�

�Min�

�Max�

�Min�

�Max�

�Unit�

�Timing� Requirements�

�t� DRS�

�t� DRH�

�AD15–0� Data� Setup� Before� RD� High� 3.3�

�AD15–0� Data� Hold� After� RD� High� 0�

�4.5�

�0�

�ns�

�ns�

�Switching� Characteristics�

�t� ALEW�

�t� ADAS� 1�

�t� ALERW�

�ALE� Pulse� Width� 2� ×� t� PCLK� –� 2.0�

�AD15–0� Address� Setup� Before� ALE� Deasserted� t� PCLK� –� 2.5�

�ALE� Deasserted� to� Read� Asserted� 2� ×� t� PCLK� –� 3.8�

�2� ×� t� PCLK� –� 2.0�

�t� PCLK� –� 2.5�

�2� ×� t� PCLK� –� 3.8�

�ns�

�ns�

�ns�

�t� RRH� 2�

�Delay� Between� RD� Rising� Edge� to� Next� Falling�

�H� +� t� PCLK� –� 1.4�

�H� +� t� PCLK� –� 1.4�

�ns�

�Edge�

�t� ADAH�

�t� RWALE�

�t� RDDRV�

�1�

�Read� Deasserted� to� ALE� Asserted� F� +� H� +� 0.5�

�ALE� Address� Drive� After� Read� High� F� +� H� +� t� PCLK� –� 2.3�

�AD15–0� Address� Hold� After� ALE� Deasserted� t� PCLK� –� 2.3�

�F� +� H� +� 0.5�

�F� +� H� +� t� PCLK� –� 2.3�

�t� PCLK� –� 2.3�

�ns�

�ns�

�ns�

�t� ALEHZ1�

�t� RW�

�ALE� Deasserted� to� Address/Data15–0� in� High-Z� t� PCLK�

�RD� Pulse� Width� D� –� 2.0�

�t� PCLK� +� 3.0� t� PCLK�

�D� –� 2.0�

�t� PCLK� +� 3.8�

�ns�

�ns�

�D� =� (The� value� set� by� the� PPDUR� Bits� (5–1)� in� the� PPCTL� register)� ×� t� PCLK�

�H� =� t� PCLK� (if� a� hold� cycle� is� specified,� else� H� =� 0)�

�F� =� 7� � t� PCLK� (if� FLASH_MODE� is� set,� else� F� =� 0)�

�1�

�2�

�On� reset,� ALE� is� an� active� high� cycle.� However,� it� can� be� configured� by� software� to� be� active� low.�

�This� parameter� is� only� available� when� in� EMPP� =� 0� mode.�

�ALE�

�t� ALEW�

�t� ALERW�

�t� RWALE�

�t� RRH�

�RD�

�t� RW�

�WR�

�t� ALEHZ�

�t� RDDRV�

�t� ADAS�

�t� ADAH�

�t� DRS�

�t� DRH�

�AD15–0�

�VALID� ADDRESS�

�VALID� DATA�

�VALID� DATA�

�VALID�

�ADDRESS�

�NOTE:� FOR� 16-BIT� MEMORY� READS,� WHEN� EMPP�

�0,� ONLY� ONE� RD� PULSE� OCCURS� BETWEEN� ALE� CYCLES.�

�WHEN� EMPP� =� 0,� MULTIPLE� RD� PULSES� OCCUR� BETWEEN� ALE� CYCLES.� FOR� COMPLETE� INFORMATION,�

�SEE� THE� ADSP-2136x� SHARC� PROCESSOR� HARDWARE� REFERENCE.�

�Figure� 18.� Read� Cycle� for� 16-Bit� Memory� Timing�

�Rev.� J� |�

�Page� 26� of� 60� |�

�July� 2013�

�相关PDF资料 |

PDF描述 |

|---|---|

| ADSP-BF537KBCZ-6AV | IC DSP CTLR 16BIT 182CSPBGA |

| V300A2E160BL | CONVERTER MOD DC/DC 2V 160W |

| ADSP-2191MKSTZ-160 | IC DSP CONTROLLER 16BIT 144LQFP |

| MLP2012S2R2T | INDUCTOR MULTILAYER 2.2UH 0805 |

| 10090098-S254VLF | DSUB STR 25POS SOCKET |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-21363SBBC-ENG | 制造商:AD 制造商全称:Analog Devices 功能描述:SHARC Processor |

| ADSP-21363SBBCZENG | 制造商:AD 制造商全称:Analog Devices 功能描述:SHARC Processor |

| ADSP-21363SBSQ-ENG | 制造商:AD 制造商全称:Analog Devices 功能描述:SHARC Processor |

| ADSP-21363SBSQZENG | 制造商:AD 制造商全称:Analog Devices 功能描述:SHARC Processor |

| ADSP-21363SCSQ-ENG | 制造商:AD 制造商全称:Analog Devices 功能描述:SHARC Processor |

发布紧急采购,3分钟左右您将得到回复。