- 您现在的位置:买卖IC网 > PDF目录19504 > ADSP-21363KSWZ-1AA (Analog Devices Inc)IC DSP 32BIT 333MHZ EPAD 144LQFP PDF资料下载

参数资料

| 型号: | ADSP-21363KSWZ-1AA |

| 厂商: | Analog Devices Inc |

| 文件页数: | 4/60页 |

| 文件大小: | 0K |

| 描述: | IC DSP 32BIT 333MHZ EPAD 144LQFP |

| 产品培训模块: | SHARC Processor Overview |

| 标准包装: | 1 |

| 系列: | SHARC® |

| 类型: | 浮点 |

| 接口: | DAI,SPI |

| 时钟速率: | 333MHz |

| 非易失内存: | ROM(512 kB) |

| 芯片上RAM: | 384kB |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 1.20V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 144-LQFP 裸露焊盘 |

| 供应商设备封装: | 144-LQFP(20x20) |

| 包装: | 托盘 |

第1页第2页第3页当前第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页

�� �

�

�

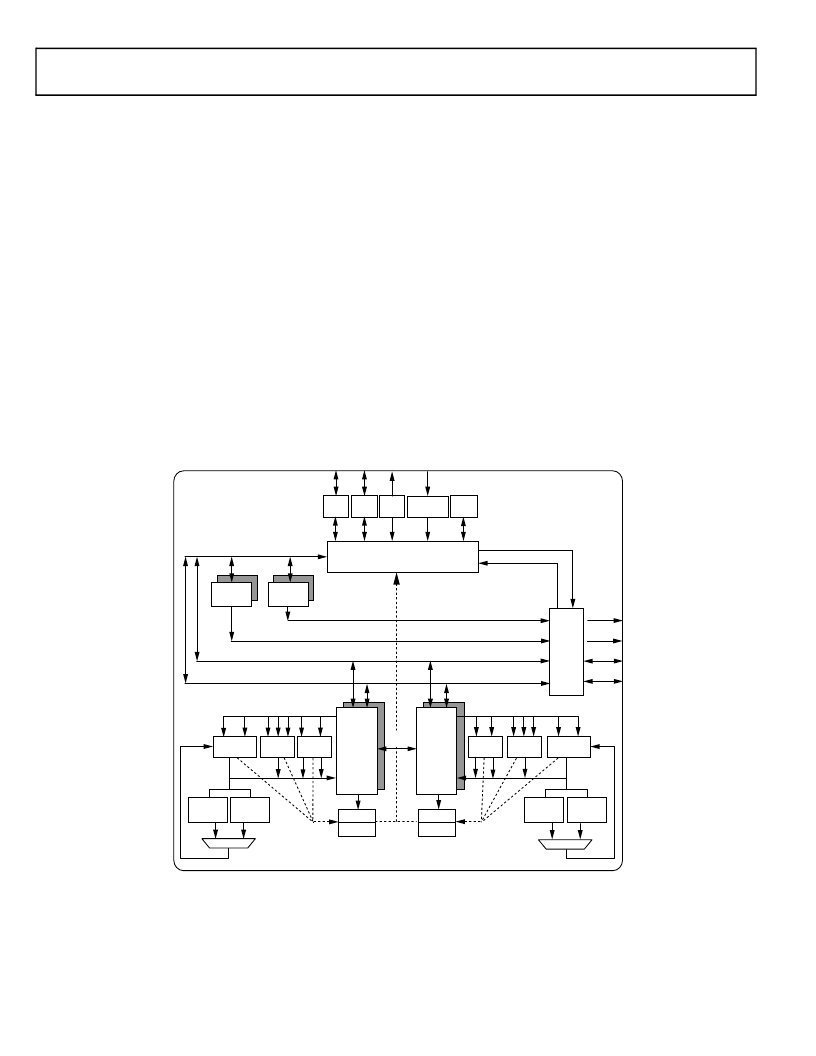

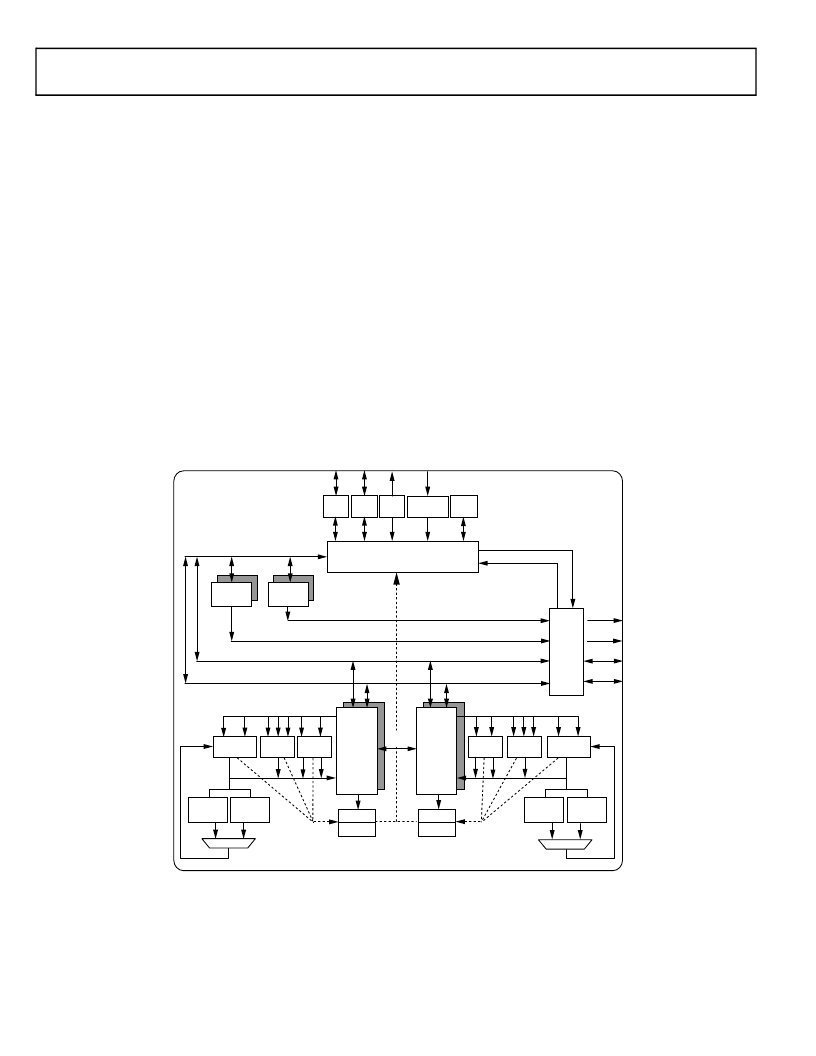

�ADSP-21362/ADSP-21363/ADSP-21364/ADSP-21365/ADSP-21366�

�SHARC� FAMILY� CORE� ARCHITECTURE�

�The� ADSP-2136x� is� code-compatible� at� the� assembly� level� with�

�the� ADSP-2126x,� ADSP-21160,� and� ADSP-21161,� and� with� the�

�first� generation� ADSP-2106x� SHARC� processors.� The�

�ADSP-2136x� shares� architectural� features� with� the� ADSP-2126x�

�and� ADSP-2116x� SIMD� SHARC� processors,� as� shown� in�

��SIMD� Computational� Engine�

�The� processor� contains� two� computational� processing� elements�

�that� operate� as� a� single-instruction,� multiple-data� (SIMD)�

�engine.� The� processing� elements� are� referred� to� as� PEX� and� PEY�

�and� each� contains� an� ALU,� multiplier,� shifter,� and� register� file.�

�PEX� is� always� active,� and� PEY� can� be� enabled� by� setting� the�

�PEYEN� mode� bit� in� the� MODE1� register.� When� this� mode� is�

�enabled,� the� same� instruction� is� executed� in� both� processing� ele-�

�ments,� but� each� processing� element� operates� on� different� data.�

�This� architecture� is� efficient� at� executing� math� intensive� signal�

�processing� algorithms.�

�Entering� SIMD� mode� also� has� an� effect� on� the� way� data� is� trans-�

�ferred� between� memory� and� the� processing� elements.� When� in�

�SIMD� mode,� twice� the� data� bandwidth� is� required� to� sustain�

�computational� operation� in� the� processing� elements.� Because� of�

�this� requirement,� entering� SIMD� mode� also� doubles� the�

�bandwidth� between� memory� and� the� processing� elements.�

�When� using� the� DAGs� to� transfer� data� in� SIMD� mode,� two� data�

�values� are� transferred� with� each� access� of� memory� or�

�the� register� file.�

�Independent,� Parallel� Computation� Units�

�Within� each� processing� element� is� a� set� of� computational� units.�

�The� computational� units� consist� of� an� arithmetic/logic� unit�

�(ALU),� multiplier,� and� shifter.� These� units� perform� all� opera-�

�tions� in� a� single� cycle.� The� three� units� within� each� processing�

�element� are� arranged� in� parallel,� maximizing� computational�

�throughput.� Single� multifunction� instructions� execute� parallel�

�ALU� and� multiplier� operations.� In� SIMD� mode,� the� parallel�

�ALU� and� multiplier� operations� occur� in� both� processing�

�elements.� These� computation� units� support� IEEE� 32-bit,�

�single-precision� floating-point,� 40-bit� extended-precision�

�floating-point,� and� 32-bit� fixed-point� data� formats.�

�S�

�SIMD� Core�

�JTAG�

�FLAG�

�TIMER� INTERRUPT� CACHE�

�PM� ADDRESS� 24�

�DMD/PMD� 64�

�5� STAGE�

�PROGRAM� SEQUENCER�

�PM� DATA� 48�

�DAG1�

�16x32�

�DAG2�

�16x32�

�PM� ADDRESS� 32�

�SYSTEM�

�DM� ADDRESS� 32�

�PM� DATA� 64�

�DM� DATA� 64�

�I/F�

�USTAT�

�4x32-BIT�

�PX�

�64-BIT�

�RF�

�DATA�

�RF�

�MULTIPLIER�

�SHIFTER�

�ALU�

�Rx/Fx�

�PEx�

�SWAP�

�Sx/SFx�

�PEy�

�ALU�

�SHIFTER�

�MULTIPLIER�

�16x40-BIT�

�16x40-BIT�

�MRF�

�MRB�

�MSB�

�MSF�

�80-BIT�

�80-BIT�

�ASTATx�

�ASTATy�

�80-BIT�

�80-BIT�

�STYKx�

�STYKy�

�Figure� 2.� SHARC� Core� Block� Diagram�

�Rev.� J� |�

�Page� 4� of� 60� |�

�July� 2013�

�相关PDF资料 |

PDF描述 |

|---|---|

| ADSP-BF537KBCZ-6AV | IC DSP CTLR 16BIT 182CSPBGA |

| V300A2E160BL | CONVERTER MOD DC/DC 2V 160W |

| ADSP-2191MKSTZ-160 | IC DSP CONTROLLER 16BIT 144LQFP |

| MLP2012S2R2T | INDUCTOR MULTILAYER 2.2UH 0805 |

| 10090098-S254VLF | DSUB STR 25POS SOCKET |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-21363SBBC-ENG | 制造商:AD 制造商全称:Analog Devices 功能描述:SHARC Processor |

| ADSP-21363SBBCZENG | 制造商:AD 制造商全称:Analog Devices 功能描述:SHARC Processor |

| ADSP-21363SBSQ-ENG | 制造商:AD 制造商全称:Analog Devices 功能描述:SHARC Processor |

| ADSP-21363SBSQZENG | 制造商:AD 制造商全称:Analog Devices 功能描述:SHARC Processor |

| ADSP-21363SCSQ-ENG | 制造商:AD 制造商全称:Analog Devices 功能描述:SHARC Processor |

发布紧急采购,3分钟左右您将得到回复。