- 您现在的位置:买卖IC网 > PDF目录19383 > ADSP-BF561SKBCZ-6V (Analog Devices Inc)IC DSP 32BIT 600MHZ 256CSPBGA PDF资料下载

参数资料

| 型号: | ADSP-BF561SKBCZ-6V |

| 厂商: | Analog Devices Inc |

| 文件页数: | 14/64页 |

| 文件大小: | 0K |

| 描述: | IC DSP 32BIT 600MHZ 256CSPBGA |

| 产品培训模块: | Blackfin® Processor Core Architecture Overview Blackfin® Device Drivers Blackfin® Optimizations for Performance and Power Consumption Blackfin® System Services |

| 标准包装: | 1 |

| 系列: | Blackfin® |

| 类型: | 定点 |

| 接口: | SPI,SSP,UART |

| 时钟速率: | 600MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 328kB |

| 电压 - 输入/输出: | 2.50V,3.30V |

| 电压 - 核心: | 1.35V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 256-LFBGA,CSPBGA |

| 供应商设备封装: | 256-CSPBGA(12x12) |

| 包装: | 托盘 |

| 配用: | ADZS-BFAUDIO-EZEXT-ND - BOARD EVAL AUDIO BLACKFIN ADZS-BF561-EZLITE-ND - BOARD EVAL ADSP-BF561 ADZS-BF561-MMSKIT-ND - KIT STARTER MULTIMEDIA BF561 ADZS-BFAV-EZEXT-ND - BOARD DAUGHT ADSP-BF533,37,61KIT |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页

�� �

�

�

�ADSP-BF561 �

�The� core� clock� (CCLK)� frequency� can� also� be� dynamically�

�changed� by� means� of� the� CSEL1–0� bits� of� the� PLL_DIV� register.�

�Supported� CCLK� divider� ratios� are� 1,� 2,� 4,� and� 8,� as� shown� in�

��fast� core� frequency� modifications.�

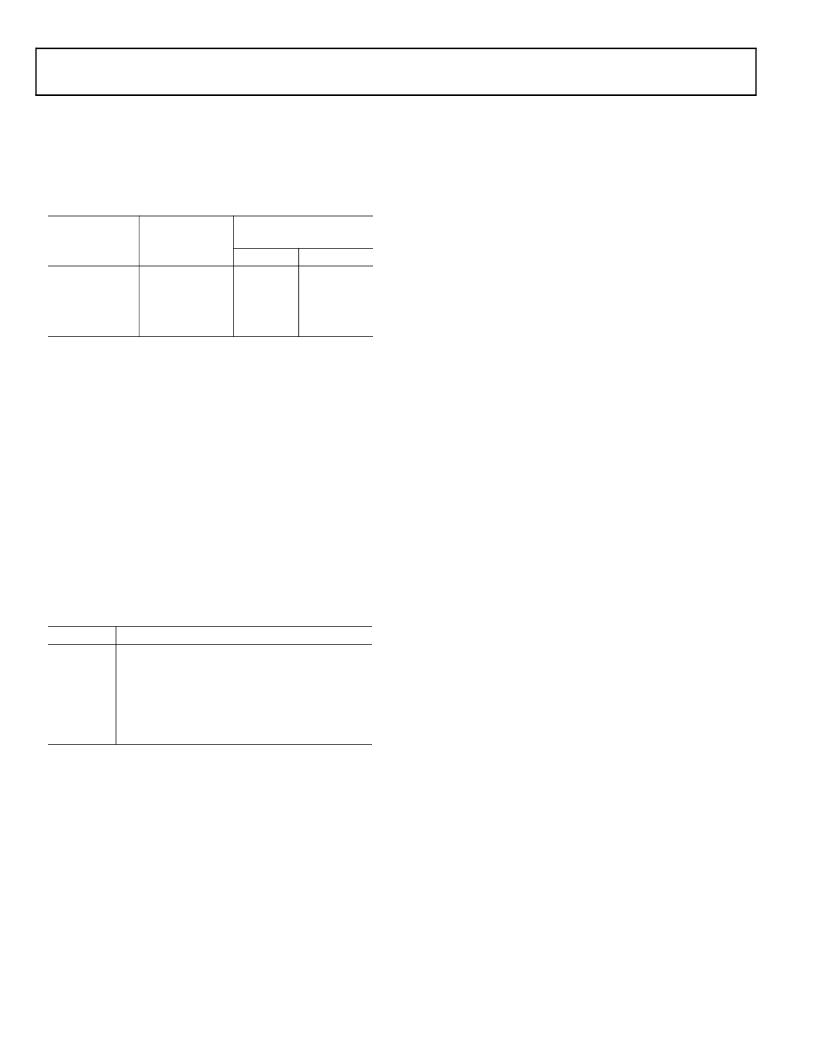

�Table� 6.� Core� Clock� Ratios�

�Example� Frequency�

�All� configuration� settings� are� set� for� the� slowest� device� pos-�

�sible� (3-cycle� hold� time;� 15-cycle� R/W� access� times;� 4-cycle�

�setup).�

�?� Boot� from� SPI� host� device� –� The� Blackfin� processor� oper-�

�ates� in� SPI� slave� mode� and� is� configured� to� receive� the� bytes�

�of� the� .LDR� file� from� an� SPI� host� (master)� agent.� To� hold�

�off� the� host� device� from� transmitting� while� the� boot� ROM�

�is� busy,� the� Blackfin� processor� asserts� a� GPIO� pin,� called�

�Signal� Name�

�CSEL1–0�

�00�

�01�

�10�

�Divider� Ratio�

�VCO/CCLK�

�1:1�

�2:1�

�4:1�

�Ratios� (MHz)�

�VCO� CCLK�

�500� 500�

�500� 250�

�200� 50�

�host� wait� (HWAIT),� to� signal� the� host� device� not� to� send�

�any� more� bytes� until� the� flag� is� deasserted.� The� flag� is� cho-�

�sen� by� the� user� and� this� information� is� transferred� to� the�

�Blackfin� processor� via� bits� 10:5� of� the� FLAG� header.�

�?� Boot� from� SPI� serial� EEPROM� (16-,� 24-bit� addressable)� –�

�The� SPI� uses� the� PF2� output� pin� to� select� a� single� SPI�

�11�

�8:1�

�200�

�25�

�EPROM� device,� submits� a� read� command� at� address�

�0x0000,� and� begins� clocking� data� into� the� beginning� of� L1�

�The� maximum� PLL� clock� time� when� a� change� is� programmed�

�via� the� PLL_CTL� register� is� 40� μs.� The� maximum� time� to� change�

�the� internal� voltage� via� the� internal� voltage� regulator� is� also�

�40� μs.� The� reset� value� for� the� PLL_LOCKCNT� register� is� 0x200.�

�This� value� should� be� programmed� to� ensure� a� 40� μs� wakeup�

�time� when� either� the� voltage� is� changed� or� a� new� MSEL� value� is�

�programmed.� The� value� should� be� programmed� to� ensure� an�

�80� μs� wakeup� time� when� both� voltage� and� the� MSEL� value� are�

�changed.� The� time� base� for� the� PLL_LOCKCNT� register� is� the�

�period� of� CLKIN.�

�BOOTING� MODES�

�The� ADSP-BF561� has� three� mechanisms� (listed� in� Table� 7� )� for�

�automatically� loading� internal� L1� instruction� memory,� L2,� or�

�external� memory� after� a� reset.� A� fourth� mode� is� provided� to� exe-�

�cute� from� external� memory,� bypassing� the� boot� sequence.�

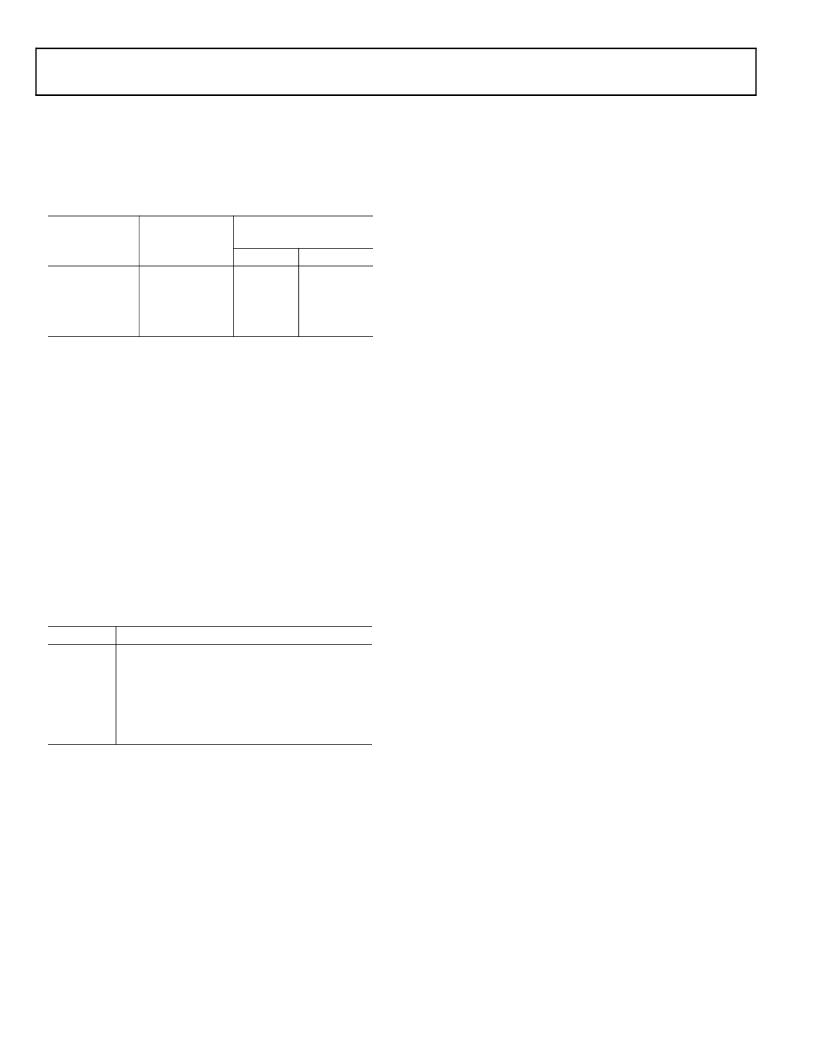

�Table� 7.� Booting� Modes�

�BMODE1� –0� Description�

�instruction� memory.� A� 16-,� 24-bit� addressable� SPI-compat-�

�ible� EPROM� must� be� used.�

�For� each� of� the� boot� modes,� a� boot� loading� protocol� is� used� to�

�transfer� program� and� data� blocks� from� an� external� memory�

�device� to� their� specified� memory� locations.� Multiple� memory�

�blocks� may� be� loaded� by� any� boot� sequence.� Once� all� blocks� are�

�loaded,� Core� A� program� execution� commences� from� the� start� of�

�L1� instruction� SRAM� (0xFFA0� 0000).� Core� B� remains� in� a� held-�

�off� state� until� Bit� 5� of� SICA_SYSCR� is� cleared� by� Core� A.� After�

�that,� Core� B� will� start� execution� at� address� 0xFF60� 0000.�

�In� addition,� Bit� 4� of� the� reset� configuration� register� can� be� set� by�

�application� code� to� bypass� the� normal� boot� sequence� during� a�

�software� reset.� For� this� case,� the� processor� jumps� directly� to� the�

�beginning� of� L1� instruction� memory.�

�INSTRUCTION� SET� DESCRIPTION�

�The� Blackfin� processor� family� assembly� language� instruction� set�

�employs� an� algebraic� syntax� that� was� designed� for� ease� of� coding�

�and� readability.� The� instructions� have� been� specifically� tuned� to�

�00�

�01�

�10�

�11�

�Execute� from� 16-bit� external� memory�

�(Bypass� Boot� ROM)�

�Boot� from� 8-bit/16-bit� flash�

�Boot� from� SPI� host� slave� mode�

�Boot� from� SPI� serial� EEPROM�

�(16-,� 24-bit� address� range)�

�provide� a� flexible,� densely� encoded� instruction� set� that� compiles�

�to� a� very� small� final� memory� size.� The� instruction� set� also� pro-�

�vides� fully� featured� multifunction� instructions� that� allow� the�

�programmer� to� use� many� of� the� processor� core� resources� in� a�

�single� instruction.� Coupled� with� many� features� more� often� seen�

�on� microcontrollers,� this� instruction� set� is� very� efficient� when�

�compiling� C� and� C++� source� code.� In� addition,� the� architecture�

�supports� both� a� user� (algorithm/application� code)� and� a� super-�

�The� BMODE� pins� of� the� reset� configuration� register,� sampled�

�during� power-on� resets� and� software� initiated� resets,� implement�

�the� following� modes:�

�?� Execute� from� 16-bit� external� memory� –� Execution� starts�

�from� address� 0x2000� 0000� with� 16-bit� packing.� The� boot�

�ROM� is� bypassed� in� this� mode.� All� configuration� settings�

�are� set� for� the� slowest� device� possible� (3-cycle� hold� time,�

�15-cycle� R/W� access� times,� 4-cycle� setup).� Note� that,� in�

�bypass� mode,� only� Core� A� can� execute� instructions� from�

�external� memory.�

�?� Boot� from� 8-bit/16-bit� external� flash� memory� –� The�

�8-bit/16-bit� flash� boot� routine� located� in� boot� ROM� mem-�

�ory� space� is� set� up� using� Asynchronous� Memory� Bank� 0.�

�visor� (O/S� kernel,� device� drivers,� debuggers,� ISRs)� mode� of�

�operation—allowing� multiple� levels� of� access� to� core� processor�

�resources.�

�The� assembly� language,� which� takes� advantage� of� the� proces-�

�sor’s� unique� architecture,� offers� the� following� advantages:�

�?� Seamlessly� integrated� DSP/CPU� features� are� optimized� for�

�both� 8-bit� and� 16-bit� operations.�

�?� A� multi-issue� load/store� modified� Harvard� architecture,�

�which� supports� two� 16-bit� MAC� or� four� 8-bit� ALU� plus�

�two� load/store� plus� two� pointer� updates� per� cycle.�

�Rev.� E� |�

�Page� 14� of� 64� |�

�September� 2009�

�相关PDF资料 |

PDF描述 |

|---|---|

| VE-B1T-CV-F3 | CONVERTER MOD DC/DC 6.5V 150W |

| MC7915ACT | IC REG LDO -15V 1A TO220AB |

| MC7912ACT | IC REG LDO -12V 1A TO220AB |

| ADSP-2183KSTZ-210 | IC DSP CONTROLLER 16BIT 128-LQFP |

| ECM12DTBN-S189 | CONN EDGECARD 24POS R/A .156 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-BF561SKBCZC70 | 制造商:Analog Devices 功能描述: |

| ADSPBF561SKBCZ-C70 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| ADSP-BF561SKBCZENG | 制造商:Analog Devices 功能描述:- Trays |

| ADSP-BF561SKBZ500 | 功能描述:IC DSP 32BIT 500MHZ 297PBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-BF561SKBZ500 | 制造商:Analog Devices 功能描述:Digital Signal Processor IC |

发布紧急采购,3分钟左右您将得到回复。