- 您现在的位置:买卖IC网 > PDF目录295886 > EP20K60EFC484-2 (ALTERA CORP) LOADABLE PLD, PBGA484 PDF资料下载

参数资料

| 型号: | EP20K60EFC484-2 |

| 厂商: | ALTERA CORP |

| 元件分类: | PLD |

| 英文描述: | LOADABLE PLD, PBGA484 |

| 封装: | 23 X 23 MM, 1 MM PITCH, FINE LINE, BGA-484 |

| 文件页数: | 113/114页 |

| 文件大小: | 4116K |

| 代理商: | EP20K60EFC484-2 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页当前第113页第114页

IGLOO nano DC and Switching Characteristics

2- 84

Advance v0.2

Part Number and Revision Date

Part Number 51700110-002-1

Revised November 2008

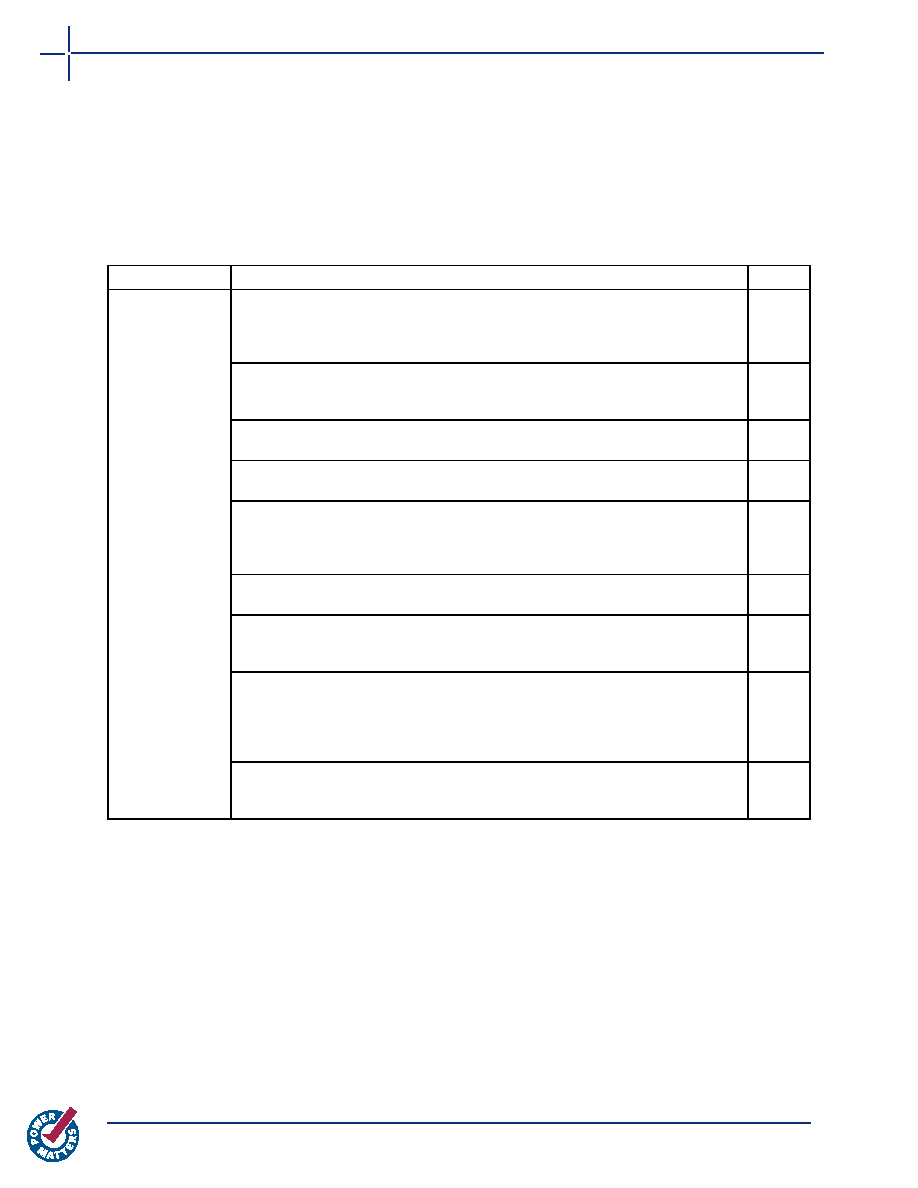

List of Changes

The following table lists critical changes that were made in the current version of the chapter.

Actel Safety Critical, Life Support, and High-Reliability

Applications Policy

The Actel products described in this advance status datasheet may not have completed Actel’s

qualification process. Actel may amend or enhance products during the product introduction and

qualification process, resulting in changes in device functionality or performance. It is the

responsibility of each customer to ensure the fitness of any Actel product (but especially a new

product) for a particular purpose, including appropriateness for safety-critical, life-support, and

other high-reliability applications. Consult Actel’s Terms and Conditions for specific liability

exclusions relating to life-support applications. A reliability report covering all of Actel’s products is

available on the Actel website at http://www.actel.com/documents/ORT_Report.pdf. Actel also

offers a variety of enhanced qualification and lot acceptance screening procedures. Contact your

local Actel sales office for additional reliability information.

Previous Version

Changes in Current Version (Advance v0.2)

Page

Advance v0.1

(October 2008)

The table notes and references were revised in Table 2-2 Recommended

stating, "VMV pins must be connected to the corresponding VCCI pins. See Pin

Descriptions for further information." Please review carefully.

added for AGLN010, AGLN015, and AGLN030 for 1.5 V.

Values for ICCA current were updated for AGLN010, AGLN015, and AGLN030 in

Values for PAC1 and PAC2 were added to Table 2-14 Different Components

Table notes regarding wide range support were added to Table2-20Summary

1.2 V LVCMOS wide range values were added to Table 2-21 Summary of

The following table note was added to Table 2-24 Summary of I/O Timing

Timing Characteristics—Software Default Settings: "All LVCMOS 3.3 V software

macros support LVCMOS 3.3 V wide range, as specified in the JESD8-B

specification."

3.3 V LVCMOS Wide Range and 1.2 V Wide Range were added to Table 2-27 I/O

相关PDF资料 |

PDF描述 |

|---|---|

| EP20K60EFC484-3 | LOADABLE PLD, PBGA484 |

| EP20K60EFC484 | LOADABLE PLD, PBGA484 |

| EP20K60EFC672-1 | LOADABLE PLD, PBGA672 |

| EP20K60EFC672-2 | LOADABLE PLD, PBGA672 |

| EP20K60EFC672-3 | LOADABLE PLD, PBGA672 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EP20K60EFI144-1ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

| EP20K60EFI144-2ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

| EP20K60EFI144-3ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

| EP20K60EFI324-1ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

| EP20K60EFI324-2ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

发布紧急采购,3分钟左右您将得到回复。