- 您现在的位置:买卖IC网 > PDF目录4578 > IDT88P8342BHGI (IDT, Integrated Device Technology Inc)IC SPI3-SPI4 EXCHANGE 820-PBGA PDF资料下载

参数资料

| 型号: | IDT88P8342BHGI |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 11/98页 |

| 文件大小: | 0K |

| 描述: | IC SPI3-SPI4 EXCHANGE 820-PBGA |

| 标准包装: | 24 |

| 系列: | * |

| 其它名称: | 88P8342BHGI |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页

19

IDT88P8342 SPI EXCHANGE 2 x SPI-3 TO SPI-4

INDUSTRIALTEMPERATURERANGE

APRIL 10, 2006

Manual phase selection

The automatic phase adjustment can be overruled by the processor when

theFORCEflagissetseeTable99,SPI-4 ingressbitalignmentcontrolregister

(register_offset 0x11). The PHASE_ASSIGN field see Table 113, SPI-4

ingressmanualalignmentphase/resultregister(0x0Cto0x1F)nowdefinesthe

selectedphase.

Word alignment

The de-skew block searches for the Training Control Word 0x0FFF. If the

Training Control Word is found, then training data is expected to follow the

Training Control Word. The orthogonal training data will be used to align the

word.

Ade-skewcontrolbit(I_DSCinTable89-SPI-4ingressconfigurationregister

at Block_base 0x0300 + Register_offset 0x00) is used to protect against a

random data error during de-skew. If I_DSC=1, then two consecutive de-skew

results are required. It is recommended to set I_DSC to a logic 1.

For diagnostics, an out of range offset between lines is provided. If the offset

is more than two bits between the earliest and latest samples, I_DSK_OOR is

set to a logic one. I_DSK_OOR is cleared to a logic zero when the offset is in

range.

Transfer decode and dispatch

In the OUT_OF_SYNCH state, the de-skew block will decode the transfer,

and check the DIP-4 for validation.

AnumberofconsecutiveerrorfreeDIP-4ingressburstswillleadtoatransition

totheIN_SYNCH.ThenumberisdefinedbytheI_INSYNC_THRfieldinTable

89-SPI-4ingressconfigurationregister(Block_base0x0300+Register_offset

0x00).

Inthe IN_SYNCHstate,thePFPdecodesthestatustransfer,checktheDIP-

4, and dispatches the data.

A number of consecutive DIP-4 errors will lead to the OUT_OF_SYNCH

state. The number is defined by the I_OUTSYNC_THR field in Table 89-SPI-

4 ingress configuration register (Block_base 0x0300 + Register_offset 0x00).

A number of consecutive training patterns will lead to OUT_OF_SYNCH.

ThenumberisdefinedbytheSTRT_TRAINfieldintheTable100SPI-4ingress

startuptrainingthresholdregister(Block_base0x0300+Register_offset0x12).

This feature is disabled if STRT_TRAIN=0.

Control word and data

AcontrolwordisdistinguishedbytheSPI-4RTCLsignal.(logicone=control

word).

DIP-4 check

For the DIP-4 check algorithm refer to the OIF SPI-4 document [Glossary].

In both IN_SYNCH and OUT_OF_SYNCH states, only control word previous

and following data is checked. Any transition on synch status will be captured.

In IN_SYNCH state, each DIP-4 error is captured and counted.

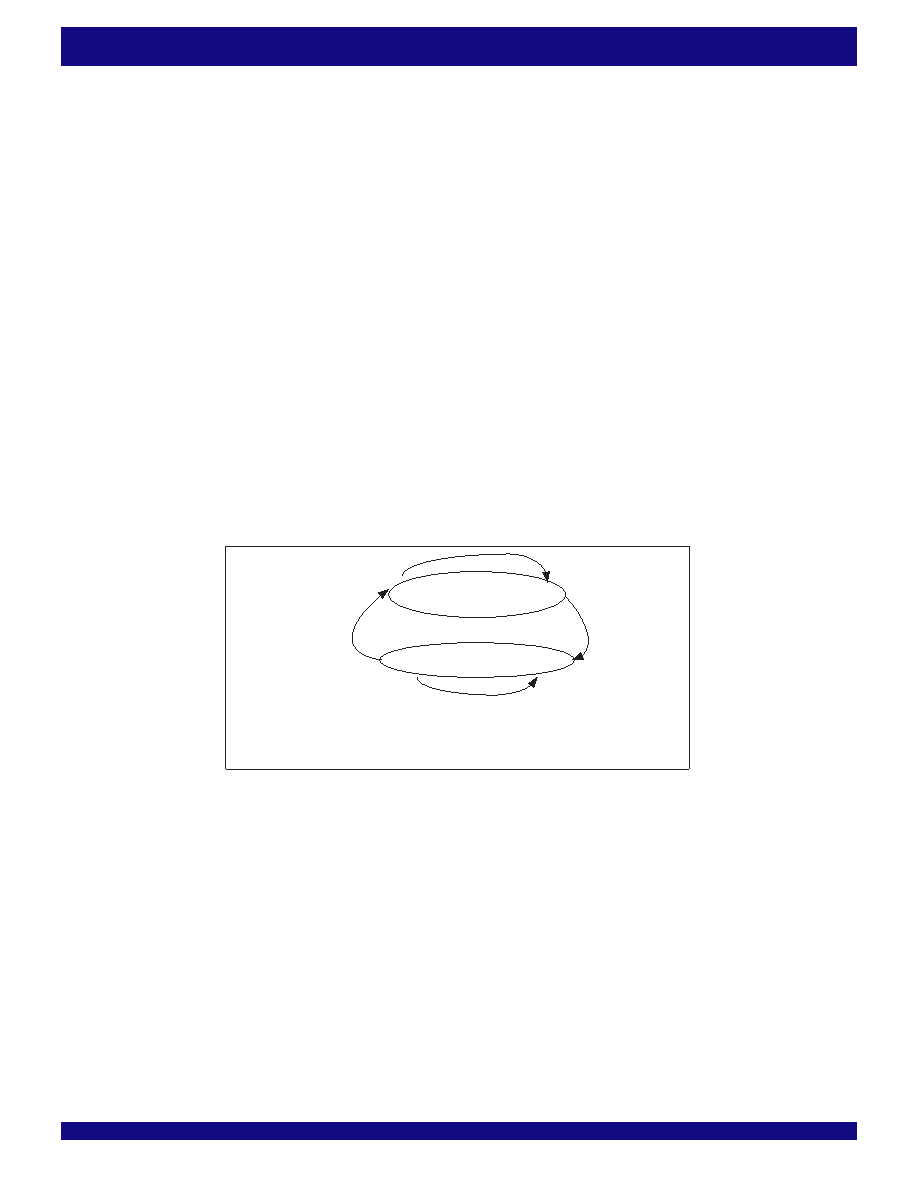

IN_SYNCH

OUT_OF_SYNCH

A= A number of consecutive DIP-4 error or reset or interface disabled

or a number of consecutive training pattern received

B= A number of consecutive DIP-4 error free

A

B

6370 drw35

Figure 8. SPI-4 ingress state diagram

Transfer decode

TheSPI-4ingresscontrolwordcontainsvariousfields.RefertotheOIFSPI-

4 document [Glossary] for details. If reserved control word, BIT[15:12]=0011,

0001, 0101, or 0111 is detected, a BUS_ERROR event is generated. If a

payload control word is not followed by a data word, or a data word does not

follow a payload control word, a BUS_ERROR event is generated. If abort is

detected, the next packet will be tagged with an error.

Data dispatch

Theportaddressfieldofapayloadcontrolwordisextractedasasearchkey.

The search key is used to search the dispatch info in Table 86, SPI-4 ingress

LP to LID map (256 entries, one per LP). If the searched port is active, transfer

dataissenttotheassociatedPFPwithSOP,EOP,LENGTH,PACKET_ERROR.

If the searched port is inactive, a SPI4_INACTIVE_TRANSFER event is

generated.ASPI-4inactive transfereventwithit'sassociatedLPwillbecaptured

in the Table 40, SPI-4 status register (0x22 in the direct accessed space).

SPI-4 ingress status channel

Calendar structure and swapping

TheSPIExchangesupportsoneortwosetsofcalendars. IfI_CSW_ENfield

in the Table 89, SPI-4 ingress configuration register (0x00)=1, two sets of

calendars are supported. A calendar selection word must be placed following

theframingbit.RefertotheOIFSPI-4document[seeGlossary]formoredetails.

SPI-4 ingress status channel frame generation

The status frame can be one of the following cases:

All ‘11’ when LVTTL is in the out of synch state

TrainingpatternwhenLVDSisintheoutofsynchstateorinperiodictraining

相关PDF资料 |

PDF描述 |

|---|---|

| LT1528CT | IC REG LDO 3.3V/ADJ 3A TO220-5 |

| RCE40DHFT | CONN EDGECARD 80POS 1MM SMD |

| RBE40DHFT | CONN EDGECARD 80POS 1MM SMD |

| MIC5295-3.0YD TR | IC REG LDO 3V .15A TO-252-5 |

| LT3015IMSE#TRPBF | IC REG LDO NEG ADJ 1.5A 12MSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT88P8342BHI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT88P8344 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:SPI EXCHANGE 4 x SPI-3 TO SPI-4 Issue 1.0 |

| IDT88P8344BHGI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:是 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT88P8344BHI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT89H10T4BG2ZBBC | 制造商:Integrated Device Technology Inc 功能描述:IC PCI SW 10LANE 4PORT 324BGA |

发布紧急采购,3分钟左右您将得到回复。