- 您现在的位置:买卖IC网 > PDF目录4578 > IDT88P8342BHGI (IDT, Integrated Device Technology Inc)IC SPI3-SPI4 EXCHANGE 820-PBGA PDF资料下载

参数资料

| 型号: | IDT88P8342BHGI |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 24/98页 |

| 文件大小: | 0K |

| 描述: | IC SPI3-SPI4 EXCHANGE 820-PBGA |

| 标准包装: | 24 |

| 系列: | * |

| 其它名称: | 88P8342BHGI |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页

30

IDT88P8342 SPI EXCHANGE 2 x SPI-3 TO SPI-4

INDUSTRIALTEMPERATURERANGE

APRIL 10, 2006

4.2 SPI-4 to SPI-3 datapath and flow control

TwoPacketFragmentProcessormodulesfromSPI4ingresstoSPI-3egress

are provided, all connected to one SPI-4 ingress interface.

PacketburstsfromtheSPI-4ingressarereceivedintotheSPI-4ingressport

buffers.Apacketfragmentprocessortransferscompletepacketburstsfromthe

SPI-4 ingress port buffers to memory segments previously reserved on a per-

LP basis in the buffer segment pool. The SPI-4 ingress port buffer watermarks

andtheper-LPfreebuffersegmentthresholdinformationiscombinedtoproduce

SPI-4 ingress FIFO status (per-LP starving, hungry, or satisfied) towards the

attachedSPI-4device.Per-LPbuffersegmentthresholdinformationisusedto

produce FIFO status information for the attached SPI-3 device. Packets or

packetfragmentsareforwardedtotheSPI-3interfacewhenapacketiscomplete

or a predefined number of bytes have been received. Packets or packet

fragments received on one SPI4 logical port are cross connected to an SPI3

logical port through an intermediate mapping to a Link identification, or LID. Its

modeofoperationissimilartotheSPI-3ingresstoSPI-4egresspacketfragment

processor, with the following differences:

1) The PFP4-3 data input has three sources, listed in descending priority:

SPI-4 buffers, redirect buffers, and insert buffers.

2) The PFP3-4 data output has only three destinations. There is no SPI-3

to SPI-4 redirect path.

Each SPI-3 interface feeds ingress buffer available or ingress buffer

unavailable status information to its packet fragment processor.

If the number of free segments available to a LP exceeds the starving

threshold,theSPI-4statusismovedtostarvingforthatLP.Ifthenumberoffree

segments available to a LP exceeds the hungry but not the starving threshold,

the SPI-4 status is moved to hungry for that LP. If the hungry threshold is not

exceeded, the SPI-4 FIFO status channel will indicate satisfied for that LP.

SPI-4 ingress to SPI-3 egress datapath

The following is a description of the path taken by a burst of data through the

device from the SPI-4 ingress to a SPI-3 egress.

Data enters on the SPI-4 ingress interface in bursts. Bursts are normally of

equallengthexceptthelastburstofapacketwhichmaybeshorter.Thecontrol

word is in-band with the data. Burst data enters a SPI-4 ingress buffer. SPI-4

LP address, error information, SOP, EOP are stored with the burst data. A SPI-

4 LP address is mapped to a Logical IDentifier (LID). The burst is stored in per

LID allocated buffer segments reserved from the buffer segment pool.

The appropriate SPI-3 egress control register (Table 80 - SPI-3 egress Port

Descriptor Table (64 entries)) is consulted, and it determines to send this LID

to a prescribed SPI-3 egress port.

TheselectionofwhichLPistobetransmittednextisdependentonthestatus

of the LP and the availability of a complete fragment. Data is moved to the

appropriate SPI-3 egress buffer along with the LP address. SPI-3 LP address,

errorinformation,SOP,andEOPinformationisstoredwiththepacketfragment.

Next,dataistransmittedinpacketfragmentsovertheselectedSPI-3interface.

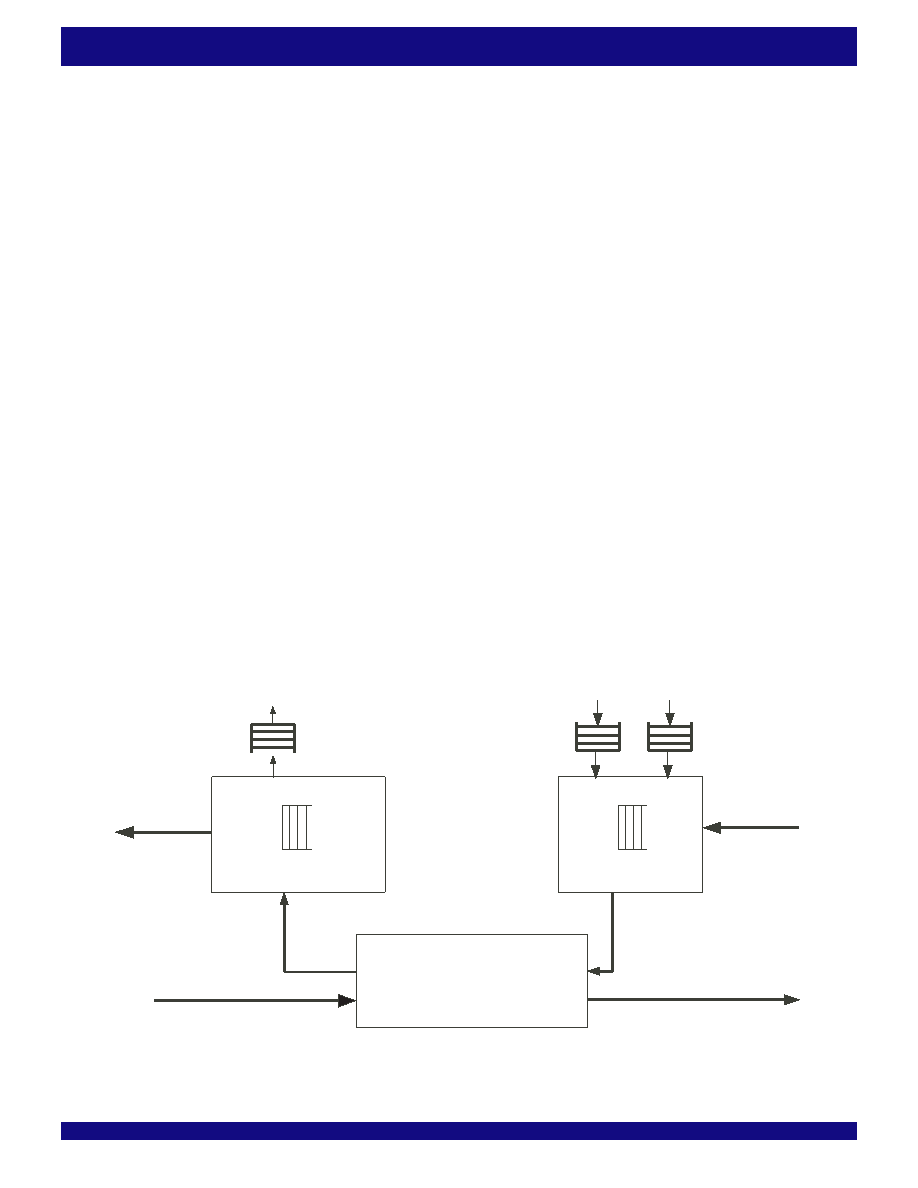

Figure 18. SPI-4 ingress to SPI-3 egress packet fragment processor

6370 drw37

FIFO Status

SPI4 Ingress

uP

capture

buffer

uP

insert

buffer

Associated

ingress PFP

SPI-3

redirect

buffers

buffer segment pool

SPI-3 egress port

buffers

SPI-4 ingress port

buffers

FIFO Status

Egress

SPI-3

相关PDF资料 |

PDF描述 |

|---|---|

| LT1528CT | IC REG LDO 3.3V/ADJ 3A TO220-5 |

| RCE40DHFT | CONN EDGECARD 80POS 1MM SMD |

| RBE40DHFT | CONN EDGECARD 80POS 1MM SMD |

| MIC5295-3.0YD TR | IC REG LDO 3V .15A TO-252-5 |

| LT3015IMSE#TRPBF | IC REG LDO NEG ADJ 1.5A 12MSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT88P8342BHI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT88P8344 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:SPI EXCHANGE 4 x SPI-3 TO SPI-4 Issue 1.0 |

| IDT88P8344BHGI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:是 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT88P8344BHI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT89H10T4BG2ZBBC | 制造商:Integrated Device Technology Inc 功能描述:IC PCI SW 10LANE 4PORT 324BGA |

发布紧急采购,3分钟左右您将得到回复。