- 您现在的位置:买卖IC网 > PDF目录4578 > IDT88P8342BHGI (IDT, Integrated Device Technology Inc)IC SPI3-SPI4 EXCHANGE 820-PBGA PDF资料下载

参数资料

| 型号: | IDT88P8342BHGI |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 83/98页 |

| 文件大小: | 0K |

| 描述: | IC SPI3-SPI4 EXCHANGE 820-PBGA |

| 标准包装: | 24 |

| 系列: | * |

| 其它名称: | 88P8342BHGI |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页当前第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页

84

IDT88P8342 SPI EXCHANGE 2 x SPI-3 TO SPI-4

INDUSTRIALTEMPERATURERANGE

APRIL 10, 2006

Inputs

Unit

Min.

Typ.

Max.

Description

Duty cycle

%

45

50

55

I_DCLK ingress clock duty cycle

Frequency (DDR)

MHz

80

—

200

Ingress clock frequency, I_LOW=1

Frequency (DDR)

MHz

200

311

400

Ingress clock frequency, I_LOW=0

TR, TF

ps

300

—

500

Input rise or fall time ( 20%, 80% )

Deskew

UI

—

+/- 1

Bit line deskew

Outputs

Duty cycle

%

45

50

55

E_DCLK Egress clock duty cycle

Frequency (DDR)

MHz

80

—

200

Egress clock frequency, E_LOW=1

Frequency (DDR)

MHz

200

311

400

Egress clock frequency, E_LOW=0

TR, TF

ps

300

—

500

Output rise or fall time ( 20%, 80% )

Tskew

ps

—

50

Output differential skew, P to N

SYNTH Jitter

UI

—

0.1

PLL jitter as a fraction of the clock cycle

TD

ns

—

Adjustable

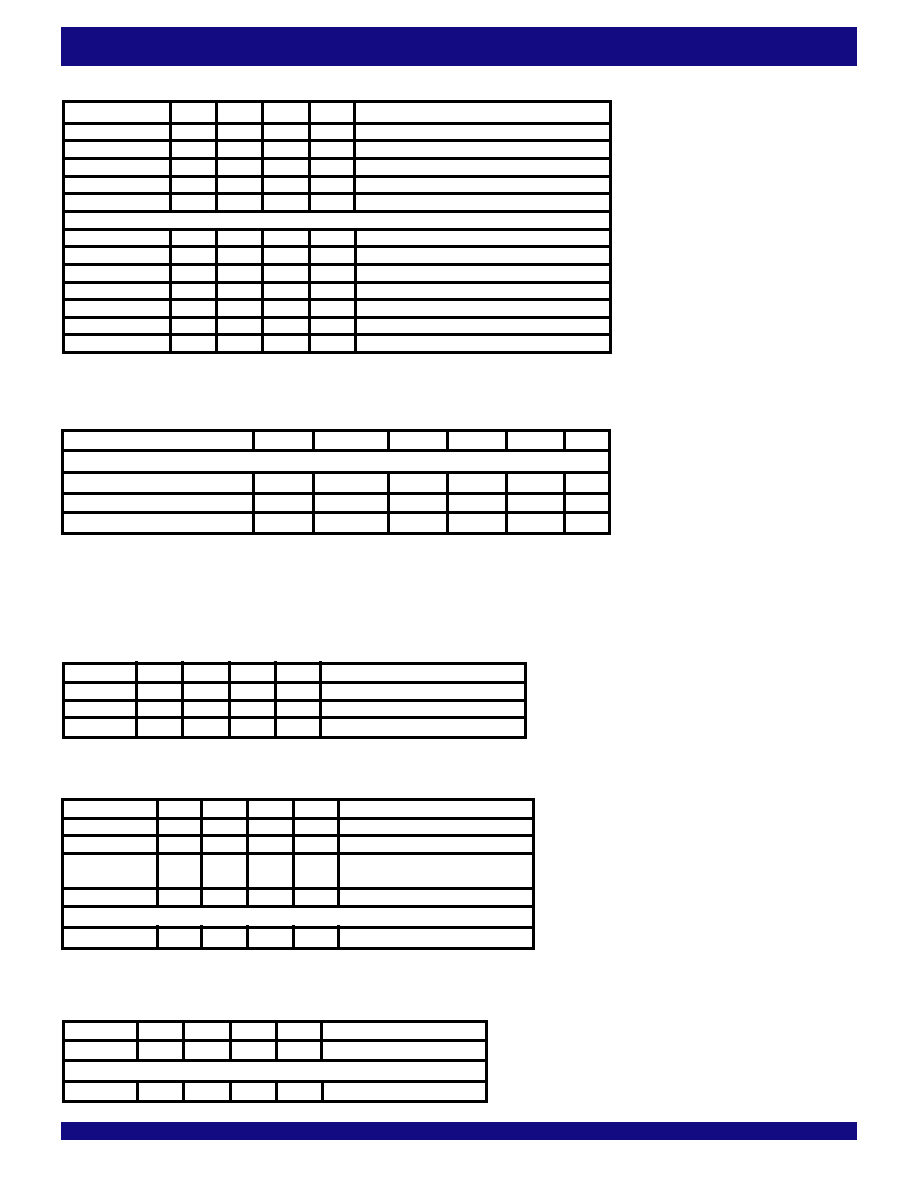

TABLE 133 – SPI-4.2 LVDS AC INPUT / OUTPUT TIMING SPECIFICATIONS

REF_CLK

Unit

Min.

Typ.

Max.

Duty cycle

%

30

50

70

REF_CLK clock input duty cycle

FREF_CLK

MHz

12.5

19.44

25

Main reference clock input

TR, TF

ns

—

5

Rise fall time ( 20%, 80% )

11.6.4 REF_CLK clock input

11.6.5 MCLK internal clock and OCLK[3:0] clock outputs

11.6.6 Microprocessor interface

All outputs

Unit

Min.

Typ.

Max.

Description

TR, Tf

ns

10

Rise, fall time (20%, 80%)

All inputs

TR, TF

ns

10

Rise, fall time (20%,80%)

Parameter

Symbol

Conditions

Min

Typ

Max

Unit

SPI-4 LVTTL Status(1)

STAT_T[1:0] to SCLK_T setup time

TSU

2ns

SCLK_T to STAT_T [1:0] hold time

TH

0.5

ns

SCLK_T to STAT_T [1:0] delay

TD

1

1.2

ns

11.6.3 SPI-4 LVTTL Status AC characteristics

TABLE 134 – SPI-4 LVTTL STATUS AC CHARACTERISTICS

TABLE 135 – REF_CLK CLOCK INPUT

TABLE 136 – OCLK[3:0] CLOCK OUTPUTS AND MCLK INTERNAL CLOCK

TABLE 137 – MICROPROCESSOR INTERFACE

NOTE:

1. For the SPI-4 LVTTL valid, hold & setup the edge is configurable. The SPI-4 ingress LVTTL status clock active edge is

configured by I_CLK_EDGE field in Table 89-SPI-4 Ingress Configuration Register on page 69. The SPI-4 egress LVTTL

status clock active edge is configured by E_CLK_EDGE field in Table 104-SPI-4 Egress Configuration Register on page 73.

OCLK[3:0]

Unit

Min.

Typ.

Max.

Description

Duty cycle

%

45

50

55

OCLK[3:0] outputs, clock duty cycle

Frequency

MHz

40

104

133

OCLK[3:0], programmable

Outputskew

One pll_oclk cycle of deliberate

between OCLKs

skew between each OCLK[3:0]

TR, TF

ns

1

2

OCLK[3:0] rise, fall time (20%,80%)

MCLK

Frequency

MHz

80

—

100

Programmable

相关PDF资料 |

PDF描述 |

|---|---|

| LT1528CT | IC REG LDO 3.3V/ADJ 3A TO220-5 |

| RCE40DHFT | CONN EDGECARD 80POS 1MM SMD |

| RBE40DHFT | CONN EDGECARD 80POS 1MM SMD |

| MIC5295-3.0YD TR | IC REG LDO 3V .15A TO-252-5 |

| LT3015IMSE#TRPBF | IC REG LDO NEG ADJ 1.5A 12MSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT88P8342BHI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT88P8344 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:SPI EXCHANGE 4 x SPI-3 TO SPI-4 Issue 1.0 |

| IDT88P8344BHGI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:是 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT88P8344BHI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT89H10T4BG2ZBBC | 制造商:Integrated Device Technology Inc 功能描述:IC PCI SW 10LANE 4PORT 324BGA |

发布紧急采购,3分钟左右您将得到回复。