- 您现在的位置:买卖IC网 > PDF目录4578 > IDT88P8342BHGI (IDT, Integrated Device Technology Inc)IC SPI3-SPI4 EXCHANGE 820-PBGA PDF资料下载

参数资料

| 型号: | IDT88P8342BHGI |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 3/98页 |

| 文件大小: | 0K |

| 描述: | IC SPI3-SPI4 EXCHANGE 820-PBGA |

| 标准包装: | 24 |

| 系列: | * |

| 其它名称: | 88P8342BHGI |

第1页第2页当前第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页

11

IDT88P8342 SPI EXCHANGE 2 x SPI-3 TO SPI-4

INDUSTRIALTEMPERATURERANGE

APRIL 10, 2006

Generic Name

Specific Name

I/O type

Description

Mode

Link

PHY

I_DCLK (P & N) SPI4_I_DCLK_P

I LVDS

Ingress data clock

RDCLK

TDCLK

SPI4_I_DCLK_N

I_DAT[15:0]

SPI4_I_DAT_P[15:0]

I LVDS

Ingress data bus

RDAT

TDAT

(P & N)

SPI4_I_DAT_N[15:0]

I_CRTL (P & N) SPI4_I_CTRL_P

I LVDS

Ingress control word

RCTL

TCTL

SPI4_I_CTRL_N

I_SCLK_L

SPI4_I_SCLK_P

O LVDS

Ingressstatusclock

RSCLK

TSCLK

(P & N)

SPI4_I_SCLK_N

I_STAT_L[1:0]

SPI4_I_STAT_P[1:0]

O LVDS

Ingressstatusinfo

RSTAT

TSTAT

(P & N)

SPI4_I_STAT_N[1:0]

I_SCLK_T

SPI4_I_SCLK_T

O LVTTL Ingressstatusclock

RSCLK

TSCLK

I_STAT_T[1:0]

SPI4_I_STAT_T[1:0]

O LVTTL Ingressstatusinfo

RSTAT

TSTAT

BIAS

Analog

Use an external 3K Ohm

----------

1% resistor to VSS

LVDS_STA

I-PU

LVDS(high)/LVTTL (low) status

----------

selection (See note below)

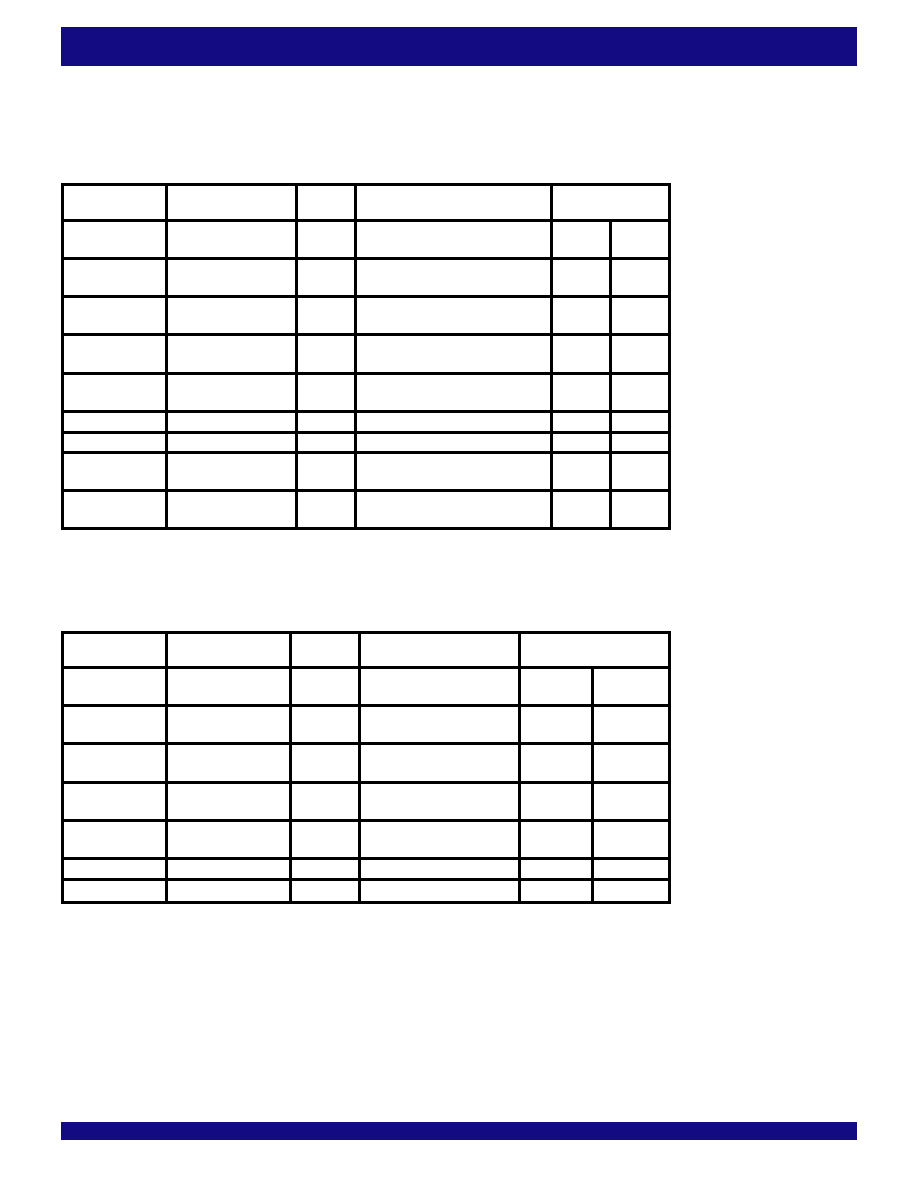

TABLE 5 – SPI-4 INGRESS INTERFACE DEFINITION

Generic Name

Specific Name

I/O type

Description

Mode

Link

PHY

E_DCLK (P & N) SPI4_E_DCLK_P

O LVDS Egress data clock

TDCLK

RDCLK

SPI4_E_DCLK_N

E_DAT[15:0]

SPI4_E_DAT_P[15:0]

O LVDS

Egress data bus

TDAT[15:0] RDAT[15:0]

(P & N)

SPI4_E_DAT_N[15:0]

E_CRTL (P & N) SPI4_E_CTRL_P

O LVDS

Egress control word

TCTL

RCTL

SPI4_E_CTRL_N

E_SCLK_L

SPI4_E_SCLK_P

I LVDS

Egressstatusclock

TSCLK

RSCLK

(P & N)

SPI4_E_SCLK_N

E_STAT_L[1:0]

SPI4_E_STAT_P[1:0]

I LVDS

Egressstatusinfo

TSTAT[1:0] RSTAT[1:0]

(P & N)

SPI4_E_STAT_N[1:0]

E_SCLK_T

SPI4_E_SCLK_T

I-ST LVTTL Egressstatusclock

TSCLK

RSCLK

E_STAT_T[1:0]

SPI4_E_STAT_T[1:0] I-PU LVTTL Egressstatusinfo

TSTAT

RSTAT[1:0]

TABLE 6 – SPI-4 EGRESS INTERFACE DEFINITION

SPI-4 (one instantiation)

For the SPI-4 interface, each pin is used differently depending whether the

SPI-4 is in Link mode or in PHY mode. The pin is given a generic name, shown

in the Name column, and mapped to the OIF standard pin name according to

the mode of operation of the interface (Link to PHY).

NOTE

:

1. A hardware reset or software reset must be performed after changing the level of this pin.

相关PDF资料 |

PDF描述 |

|---|---|

| LT1528CT | IC REG LDO 3.3V/ADJ 3A TO220-5 |

| RCE40DHFT | CONN EDGECARD 80POS 1MM SMD |

| RBE40DHFT | CONN EDGECARD 80POS 1MM SMD |

| MIC5295-3.0YD TR | IC REG LDO 3V .15A TO-252-5 |

| LT3015IMSE#TRPBF | IC REG LDO NEG ADJ 1.5A 12MSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT88P8342BHI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT88P8344 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:SPI EXCHANGE 4 x SPI-3 TO SPI-4 Issue 1.0 |

| IDT88P8344BHGI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:是 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT88P8344BHI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT89H10T4BG2ZBBC | 制造商:Integrated Device Technology Inc 功能描述:IC PCI SW 10LANE 4PORT 324BGA |

发布紧急采购,3分钟左右您将得到回复。