- 您现在的位置:买卖IC网 > PDF目录98082 > SLC88B17QFP (STANDARD MICROSYSTEMS CORP) ISA BUS CONTROLLER, PQFP160 PDF资料下载

参数资料

| 型号: | SLC88B17QFP |

| 厂商: | STANDARD MICROSYSTEMS CORP |

| 元件分类: | 总线控制器 |

| 英文描述: | ISA BUS CONTROLLER, PQFP160 |

| 封装: | QFP-160 |

| 文件页数: | 3/54页 |

| 文件大小: | 333K |

| 代理商: | SLC88B17QFP |

第1页第2页当前第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页

SMSC DS – SLC88B17

Page 11

Rev. 09/28/99

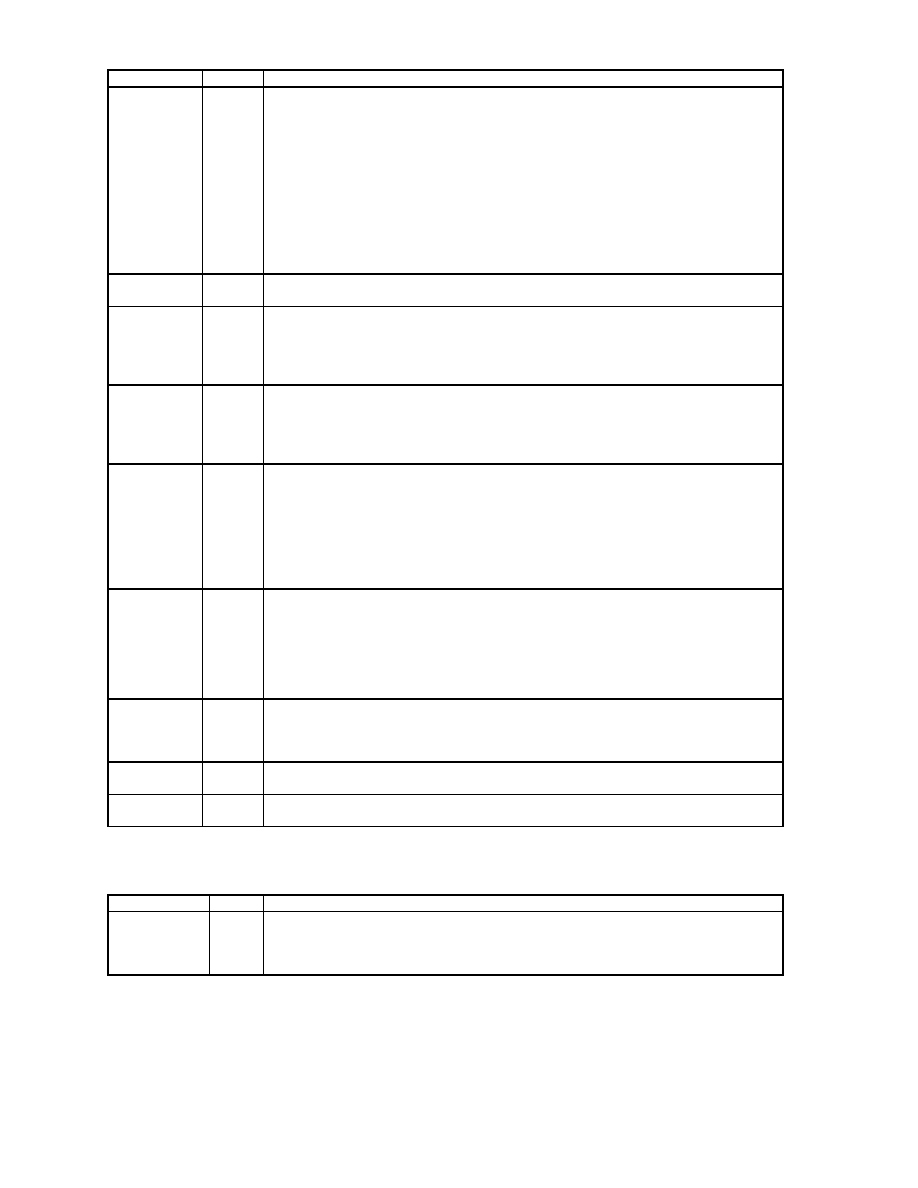

NAME

TYPE

DESCRIPTION

IOCHRDY

I/O

IO Channel Ready.

When asserted, the signal indicates that wait states are

required to complete the cycle. This signal is normally high. IOCHRDY is an input

when the SLC88B17 owns the ISA bus and the CPU or a PCI agent is accessing an

ISA slave, or during DMA transfers. It becomes an output when an external ISA

master owns the ISA bus and is accessing DRAM or a SLC88B17 register. As an

output, the signal is driven low from the falling edge of the ISA commands by the

SLC88B17. After data is available for the ISA master to read or the SLC88B17

latches the data for a write cycle, IOCHRDY is asserted for 70ns. After that, the

IOCHRDY is floated. The SLC88B17 does not drive the signal when it is not the

target of a bus master cycle.

During Reset: High-Z

After Reset: High-Z

nIOCS16

I

16-Bit IO Chip Select. When asserted, it indicates that the ISA IO device supports

16-bit I/O bus cycles.

nIOR

I/O

IO Read. ISA I/O Read command to an ISA I/O device. The I/O device must hold

the data valid until after nIOR is negated. nIOR is an input when an external ISA

master owns the ISA bus.

During Reset: High-Z

After Reset: High

nIOW

I/O

IO Write. ISA I/O Write command to an ISA I/O device. The I/O device may latch

data from the ISA data bus. nIOW is an input when an external ISA master owns the

ISA bus.

During Reset: High-Z

After Reset: High

nMEMCS16

I/O

Memory Chip Select 16.

nMEMCS16 is a decode of LA[23-17] without any

qualification of the command signals. ISA devices that are 16-bit memory devices

drive this signal low. The SLC88B17 ignores nMEMCS16 during I/O and refresh

cycles. It is used by byte-swap logic during DMA cycles. This signal is an output

when an ISA master owns the ISA bus. The SLC88B17 drives this signal low during

ISA master to DRAM cycles.

During Reset: High-Z

After Reset: High-Z

nZEROWS

I

Zero Wait States. The signal is asserted by an ISA slave to indicate that the current

cycle can be shortened after the address and command signals are decoded.

16-Bit ISA memory cycle can be reduced to 2 SYSCLKs. 8-Bit memory or I/O cycle

can be reduced to 3 SYSCLKs. 16-Bit IO cycle is not affected.

If IOCHRDY is de-asserted and nZEROWS is asserted during the same clock, then

nZEROWS is ignored and wait states are added while IOCHRDY is de-asserted.

RSTDRV

O

Reset Drive. The SLC88B17 asserts RSTDRV to reset devices that reside on the

ISA bus. The SLC88B17 asserts the signal during hard reset and power-up.

During Reset: High

After Reset: Low

nMASTER

I

Master. The signal is used with a DREQ line by an ISA master to gain control of the

ISA Bus.

DSPWRGD

I

Docking Station Power Good. The signal should be asserted active when the

SLC88B17 power source is stable.

DMA Signals

NAME

TYPE

DESCRIPTION

DREQ[0-3]

DREQ[5-7]

I

DMA Request. These DREQ lines are used to request DMA services from the

DMA controller or for a 16-bit ISA master to gain control of the ISA bus. The active

level (high or low) can be programmed via the DMA command register. The request

must remain active until the corresponding nDACK is asserted.

相关PDF资料 |

PDF描述 |

|---|---|

| SLF4000L7 | 2-INPUT NAND GATE, BCC7 |

| SLHNNGAL32ANT | SINGLE COLOR LED, GREEN, 5.2 mm |

| SLHNNWH511T0S0QRC3 | SINGLE COLOR LED, WHITE, 5.6 mm |

| SLHNNWH531T0S0QRC5 | SINGLE COLOR LED, COOL WHITE, 5.6 mm |

| SLHNNWH531T0S0QRC5 | T-3 SINGLE COLOR LED, COOL WHITE, 8 mm |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SLC8B1300 | 制造商:ITT 制造商全称:ITT Industries 功能描述:Snap/Clip-Lock Environmentally Sealed - Circular |

| SLC8B1310 | 制造商:ITT 制造商全称:ITT Industries 功能描述:Snap/Clip-Lock Environmentally Sealed - Circular |

| SLC8B500 | 制造商:ITT 制造商全称:ITT Industries 功能描述:Snap/Clip-Lock Environmentally Sealed - Circular |

| SLC8B510 | 制造商:ITT 制造商全称:ITT Industries 功能描述:Snap/Clip-Lock Environmentally Sealed - Circular |

| SLC8P1300 | 制造商:ITT 制造商全称:ITT Industries 功能描述:Snap/Clip-Lock Environmentally Sealed - Circular |

发布紧急采购,3分钟左右您将得到回复。