- 您现在的位置:买卖IC网 > PDF目录98082 > SLC88B17QFP (STANDARD MICROSYSTEMS CORP) ISA BUS CONTROLLER, PQFP160 PDF资料下载

参数资料

| 型号: | SLC88B17QFP |

| 厂商: | STANDARD MICROSYSTEMS CORP |

| 元件分类: | 总线控制器 |

| 英文描述: | ISA BUS CONTROLLER, PQFP160 |

| 封装: | QFP-160 |

| 文件页数: | 8/54页 |

| 文件大小: | 333K |

| 代理商: | SLC88B17QFP |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页

SMSC DS – SLC88B17

Page 16

Rev. 09/28/99

PCISTS

PCI Status Register

Offset Address:

06 - 07h

Default Value:

0200h

Access:

Read/Write

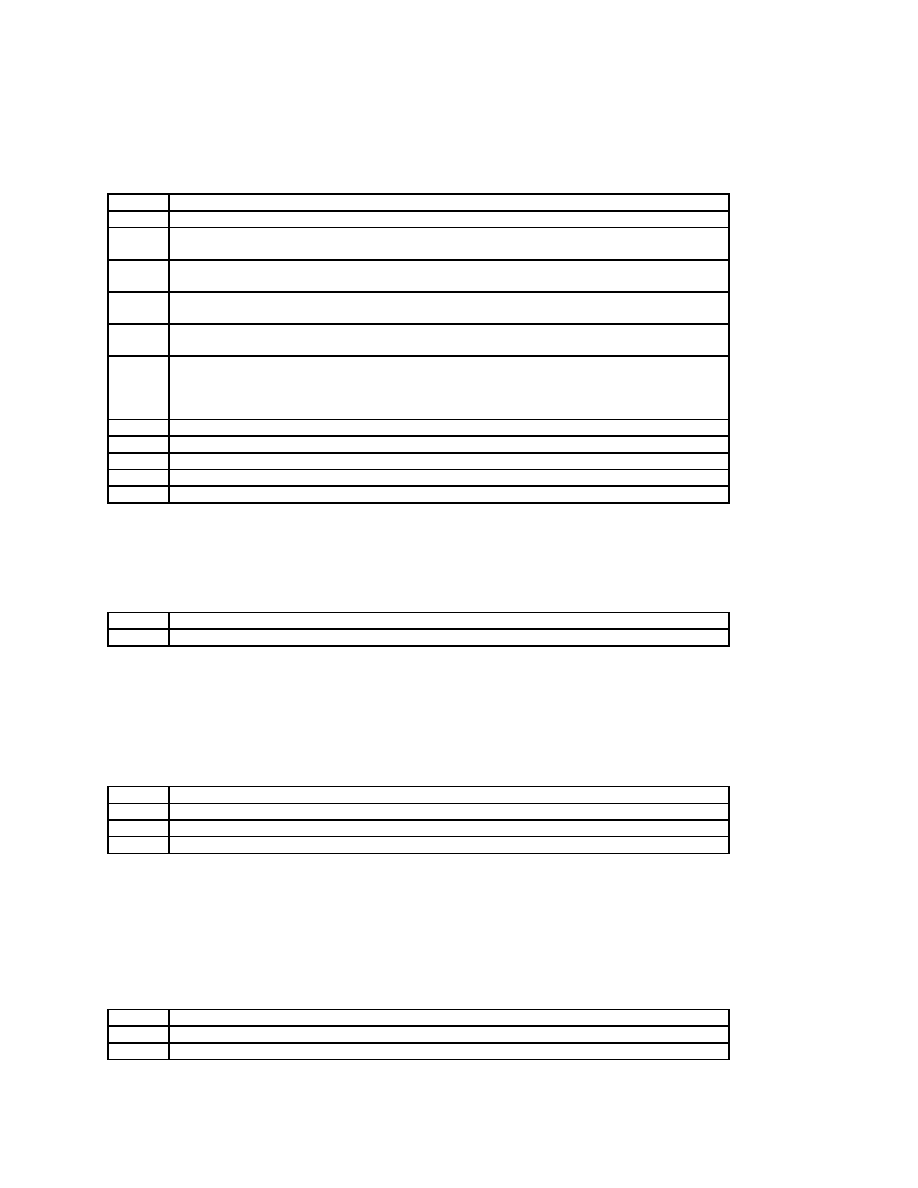

This register status information for PCI bus related events. Reads to this register behave normally. Bits in this register

can only be set by SLC88B17 events (through hardware)

BIT

FUNCTION

15

Detected Parity Error. Not implemented, hardwired to a 0.

14

Signaled nSERR Status. When the SLC88B17 asserts the nSERR signal, this bit is set to

1. Software can set this bit to a 0 by writing a 1 to it.

13

Master Abort Status. When the SLC88B17, as a master on the PCI bus, generates a

master abort, this bit is set to 1. Software can set this bit 0 by writing a 1 to it.

12

Received Target Abort Status. This bit is set when the SLC88B17 target aborts a PCI

transaction as a target. Software can set this bit 0 by writing a 1 to it.

11

Signaled Target Abort. This bit is set when the SLC88B17 signals a target abort for a

PCI transaction. Software can set this bit 0 by writing a 1 to it.

10-9

nDEVSEL Timing. Always 01 to select “medium” timing, which is two PCI clocks after the

assertion of nFRAME, when the SLC88B17 asserts nDEVSEL as a PCI target. The

medium timing is used for all positive decoding.

The SLC88B17 also does a medium

decode for PCI configuration accesses.

8

Parity Detected. Always 0, does not check parity.

7

Fast Back-to-Back. Always 0, does not support fast back-to-back transaction.

6

66 MHz/33MHz. Hardwired to 0. Maximum PCI bus frequency is 33MHz.

5

User Definable Features (UDF). Hardwired to 0. SLC88B17 does not support any UDFs.

4-0

Reserved.

RID

Revision Identification Register

Offset Address:

08h

Default Value:

00h

Access:

Read Only

BIT

FUNCTION

7-0

Hardwired to the revision number, which is set to 00 as the initial number.

CLASSCODE

Class Code Register

Offset Address:

09 - 0Bh

Default Value:

060100h

Access:

Read Only

This class code register is a read-only register used to identify SLC88B17. Writes to this register have no effect.

BIT

FUNCTION

23-16

Base Class Code. Always 06 indicating that the SLC88B17 is a bridge device.

15-8

Sub-Class Code. PCI-to-ISA subtractive decode bridge = 01h

7-0

Programming Interface. 00, no interface is defined.

HEDT

Header Type Register

Offset Address:

0Eh

Default Value:

00h

Access:

Read Only

This register is used to indicate that SLC88B17 configuration space adheres to PCI local bus specification. It also

indicates that SLC88B17 is not a multifunction device.

BIT

FUNCTION

7

Multifunction Indicator. 00h= not a multi-function device.

6-0

Layout Code. Value=0 (PCI layout type 00)

相关PDF资料 |

PDF描述 |

|---|---|

| SLF4000L7 | 2-INPUT NAND GATE, BCC7 |

| SLHNNGAL32ANT | SINGLE COLOR LED, GREEN, 5.2 mm |

| SLHNNWH511T0S0QRC3 | SINGLE COLOR LED, WHITE, 5.6 mm |

| SLHNNWH531T0S0QRC5 | SINGLE COLOR LED, COOL WHITE, 5.6 mm |

| SLHNNWH531T0S0QRC5 | T-3 SINGLE COLOR LED, COOL WHITE, 8 mm |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SLC8B1300 | 制造商:ITT 制造商全称:ITT Industries 功能描述:Snap/Clip-Lock Environmentally Sealed - Circular |

| SLC8B1310 | 制造商:ITT 制造商全称:ITT Industries 功能描述:Snap/Clip-Lock Environmentally Sealed - Circular |

| SLC8B500 | 制造商:ITT 制造商全称:ITT Industries 功能描述:Snap/Clip-Lock Environmentally Sealed - Circular |

| SLC8B510 | 制造商:ITT 制造商全称:ITT Industries 功能描述:Snap/Clip-Lock Environmentally Sealed - Circular |

| SLC8P1300 | 制造商:ITT 制造商全称:ITT Industries 功能描述:Snap/Clip-Lock Environmentally Sealed - Circular |

发布紧急采购,3分钟左右您将得到回复。