- 您现在的位置:买卖IC网 > PDF目录16115 > TS-MAC-SC-UT4 (Lattice Semiconductor Corporation)SITE LICENSE ETH MAC TRI SC/SCM PDF资料下载

参数资料

| 型号: | TS-MAC-SC-UT4 |

| 厂商: | Lattice Semiconductor Corporation |

| 文件页数: | 19/66页 |

| 文件大小: | 0K |

| 描述: | SITE LICENSE ETH MAC TRI SC/SCM |

| 标准包装: | 1 |

| 系列: | * |

| 其它名称: | TSMACSCUT4 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页

�� �

�

Lattice� Semiconductor�

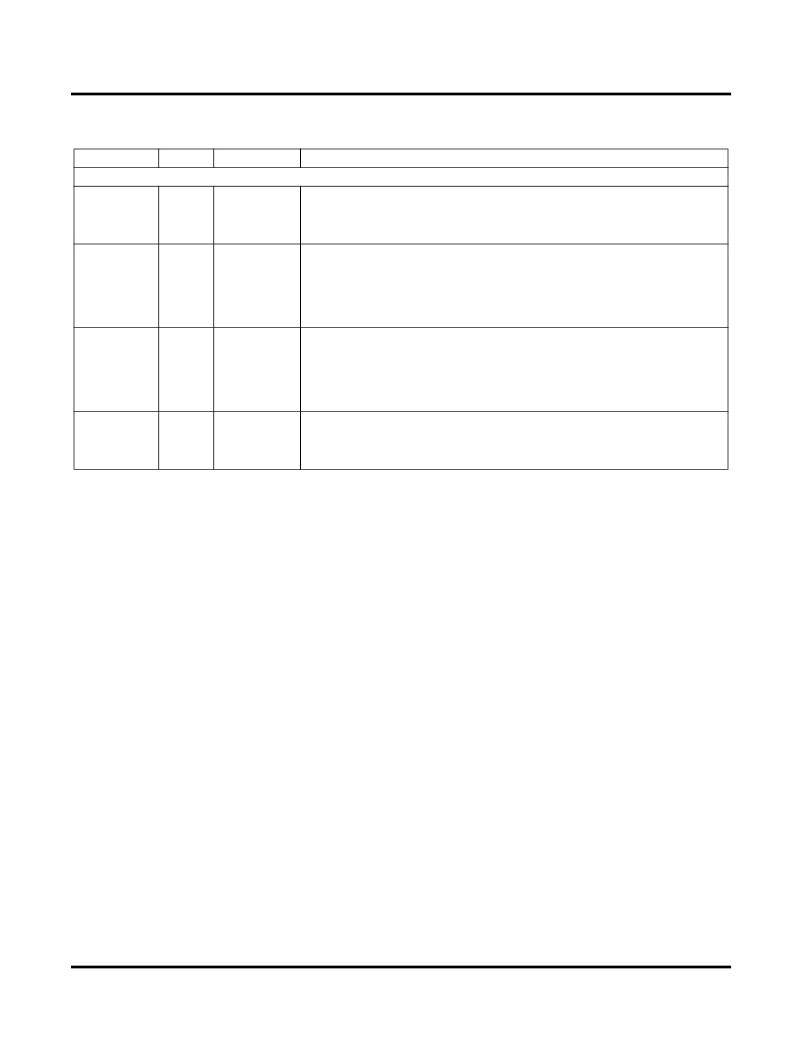

�Table� 2-2� lists� TSMAC� IP� core� system� input� and� output� signals.�

�Table� 2-2.� TSMAC� IP� Core� System� Input� and� Output� Signals�

�Functional� Description�

�Port� Name�

�Type�

�Active� State�

�Description�

�Clocks� and� Reset�

�System� Clock� .� In� the� 1G� mode,� the� Tx� MAC� is� clocked� by� this� signal.� All� the� input�

�sys_clk�

�Input�

�N/A�

�and� the� output� signals� of� the� Tx� MAC� are� synchronous� to� this� clock� in� the� 1G�

�mode.� The� frequency� is� always� at� 125� MHz.� Note� in� the� 1G� mode� the� core’s�

�txmac_clk� is� derived� from� this� clock.�

�Transmit� Clock� .� This� clock� is� used� in� the� 10/100� Mbps� mode� only.� The� Tx� MAC,�

�Tx� MAC� application� interface� and� the� MII� are� synchronous� to� this� signal.� This�

�tx_clk�

�Input�

�N/A�

�clock� has� a� frequency� of� 2.5/25� MHz� for� 10/100� Mbps� operation� respectively.� Note�

�in� the� 10/100� mode� tx_clk� is� divided� by� two� to� provide� the� clock� (txmac_clk)� to� the�

�transmit� MAC� section.� In� the� 10/100� mode� the� transmit� signals� at� the� GMII� inter-�

�face� are� always� synchronous� to� tx_clk.�

�Receive� Clock� .� This� clock� is� an� input� from� the� PHY� device.� In� the� 1G� mode,�

�rx_clk� frequency� is� 125� MHz� while� in� the� 10/100� mode,� the� corresponding� rx_clk�

�rx_clk�

�Input�

�N/A�

�frequency� is� 2.5/25� MHz� respectively.� In� the� 10/100� mode� rx_clk� is� divided� by� two�

�to� provide� the� clock� (rxmac_clk)� to� the� Receive� MAC� section.� In� the� 1G� mode� this�

�clock� is� provided� directly� to� the� Receive� MAC� section.� The� receive� signals� at� the�

�GMII� interface� are� always� synchronous� to� rx_clk.�

�Gigabit� Transmit� Clock� .� This� clock� is� used� in� the� 1G� mode� only.� The� transmit�

�gtx_clk�

�Output�

�N/A�

�signals� that� are� outputs� on� the� GMII� interface� are� synchronous� to� this� clock.� This�

�clock� has� a� frequency� of� 125� MHz.� This� clock� is� derived� from� the� sys_clk.� See�

�Figure� 2-6� .�

�Host� Interface�

�The� Host� Interface� module� is� a� fully� synchronous� module� that� runs� off� the� host� clock.� A� number� of� registers� are� ini-�

�tialized� via� the� Host� interface� to� ensure� that� the� TSMAC� IP� core� functions� as� intended.� The� write� operation� to� an�

�internal� register� is� initiated� when� the� hcs_n� and� hwrite_n� signals� are� asserted� and� hread_n� signal� is� deasserted.�

�The� address� of� the� targeted� register� is� placed� on� the� haddr� bus,� while� the� valid� data� is� placed� on� the� hdatain� bus.�

�The� contents� of� the� address� and� data� busses� should� remain� unchanged� until� the� TSMAC� IP� core� asserts� the�

�hready_n� signal.� The� signals� hcs_n,� hwrite_n� and� hread_n� must� remain� unchanged� until� hready_n� is� asserted.�

�A� register� read� is� initiated� by� asserting� the� hcs_n� and� hread_n� signals,� while� keeping� the� hwrite_n� signal� deas-�

�serted.� The� address� of� the� targeted� register� is� placed� on� the� haddr� bus.� The� TSMAC� IP� core� places� the� content� of�

�the� targeted� register� on� the� hdataout� bus� and� qualifies� it� with� the� assertion� of� hready_n� signal.� The� haddr� bus�

�should� not� change� until� the� hready_n� signal� is� asserted.�

�Figure� 2-17� shows� the� timing� diagram� associated� with� the� host� interface� write� and� read� operations.�

�Receive� MAC� (Rx� MAC)�

�The� main� function� of� the� Rx� MAC� is� to� accept� the� formatted� data� from� the� G/MII� interface� and� pass� it� to� the� host�

�application� through� an� external� FIFO.� In� this� process,� the� Rx� MAC� performs� the� following� functions:�

�?� Detect� the� start� of� frame�

�?� Compare� the� MAC� address�

�?� Re-calculate� CRC�

�?� Process� the� control� frame� and� pass� it� to� the� flow� control� module.�

�The� Rx� MAC� operation� is� determined� by� programming� the� MODE� and� TX_RX_CTL� registers.� These� register� defini-�

�tions� and� bit� descriptions� can� be� found� in� Table� 2-4� on� page� 25� .� Note� that� setting� the� Gbit_en� bit� in� the� MODE� reg-�

�ister� to� high� sets� the� TSMAC� to� operate� in� 1G� mode� whereas� setting� the� Gbit_en� bit� to� low� sets� the� TSMAC� to�

�operate� in� 10/100� Mode.�

�IPUG51_03.0,� December� 2010�

�19�

�Tri-Speed� Ethernet� MAC� User’s� Guide�

�相关PDF资料 |

PDF描述 |

|---|---|

| VI-J0T-EZ-F4 | CONVERTER MOD DC/DC 6.5V 25W |

| M3CGK-2620K | IDC CABLE - MKC26K/MC26F/MCS26K |

| TS-MAC-PM-UT4 | SITE LICENSE ETH MAC TRI ECP2M |

| VI-J0T-EZ-F2 | CONVERTER MOD DC/DC 6.5V 25W |

| TS-MAC-P2-UT4 | SITE LICENSE ETH MAC TRI ECP2 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TSMACX2U2 | 功能描述:以太网模块 TriSpd Ethernet MAC RoHS:否 制造商:Lantronix 产品:Device Servers 数据速率:300 bps to 921.6 kbps, 10 Mbps, 100 Mbps 接口类型:Ethernet, Serial 工作电源电压:5 V to 15 V 工作电源电流:133 mA to 400 mA 最大工作温度:+ 70 C |

| TS-MAC-X2-U3 | 功能描述:开发软件 Ethernet MAC TriSPD RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| TS-MAC-X2-U4 | 功能描述:开发软件 ETHERNET MAC TRI-SPEED RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| TS-MAC-X2-UT4 | 功能描述:开发软件 ETHERNET MAC TRI-SPEED RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| TSMACXMU2 | 功能描述:以太网模块 TriSpd Ethernet MAC RoHS:否 制造商:Lantronix 产品:Device Servers 数据速率:300 bps to 921.6 kbps, 10 Mbps, 100 Mbps 接口类型:Ethernet, Serial 工作电源电压:5 V to 15 V 工作电源电流:133 mA to 400 mA 最大工作温度:+ 70 C |

发布紧急采购,3分钟左右您将得到回复。