- 您现在的位置:买卖IC网 > PDF目录225572 > XC4VLX15-11FFG676I (XILINX INC) FPGA, 1536 CLBS, 1205 MHz, PBGA676 PDF资料下载

参数资料

| 型号: | XC4VLX15-11FFG676I |

| 厂商: | XILINX INC |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 1536 CLBS, 1205 MHz, PBGA676 |

| 封装: | LEAD FREE, FBGA-676 |

| 文件页数: | 47/58页 |

| 文件大小: | 1863K |

| 代理商: | XC4VLX15-11FFG676I |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页当前第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页

Virtex-4 FPGA Data Sheet: DC and Switching Characteristics

DS302 (v3.7) September 9, 2009

Product Specification

51

Production Stepping

The Virtex-4 FPGA stepping identification system denotes

the capability improvement of production released devices.

By definition, devices from one stepping are functional

supersets of previous devices. Bitstreams compiled for a

device with an earlier stepping are guaranteed to operate

correctly in subsequent device steppings.

New device steppings can be shipped in place of earlier

device steppings. Existing production designs are guaran-

teed on new device steppings. To take advantage of the

capabilities of a newer device stepping, customers are able

to order a new stepping version and compile a new bit-

stream.

Production devices are marked with a stepping version, with

the exception of some step 1 devices. Designs should be

compiled with a CONFIG STEPPING parameter set to a

specific stepping version. This parameter is set in the UCF

file:

CONFIG STEPPING = “#”; (where # is the stepping

version)

The default stepping level used by the ISE software is

reported in the PAR report.

Table 63 shows the JTAG ID code by step.

Table 61: Sample Window

Symbol

Description

Device

Speed Grade

Units

-12

-11

-10

TSAMP

Sampling Error at Receiver Pins(1)

All

450

500

550

ps

TSAMP_BUFIO

Sampling Error at Receiver Pins using BUFIO(2)

All

350

400

450

ps

Notes:

1.

This parameter indicates the total sampling error of Virtex-4 FPGA DDR input registers across voltage, temperature, and process. The

characterization methodology uses the DCM to capture the DDR input registers’ edges of operation. These measurements include:

- CLK0 DCM jitter

- DCM accuracy (phase offset)

- DCM phase shift resolution

These measurements do not include package or clock tree skew.

2.

This parameter indicates the total sampling error of Virtex-4 FPGA DDR input registers across voltage, temperature, and process. The

characterization methodology uses the BUFIO clock network and IDELAY to capture the DDR input registers’ edges of operation. These

measurements do not include package or clock tree skew.

Table 62: ChipSync Pin-to-Pin Setup/Hold and Clock-to-Out

Symbol

Description

Speed Grade

Units

-12

-11

-10

Data Input Setup and Hold Times Relative to a Forwarded Clock Input Pin Using BUFIO

TPSCS /TPHCS

Setup/Hold of I/O clock across multiple clock regions

–0.45

0.97

–0.45

1.08

–0.44

1.17

ns

Pin-to-Pin Clock-to-Out Using BUFIO

TICKOFCS

Clock-to-Out of I/O clock across multiple clock regions

4.10

4.54

5.02

ns

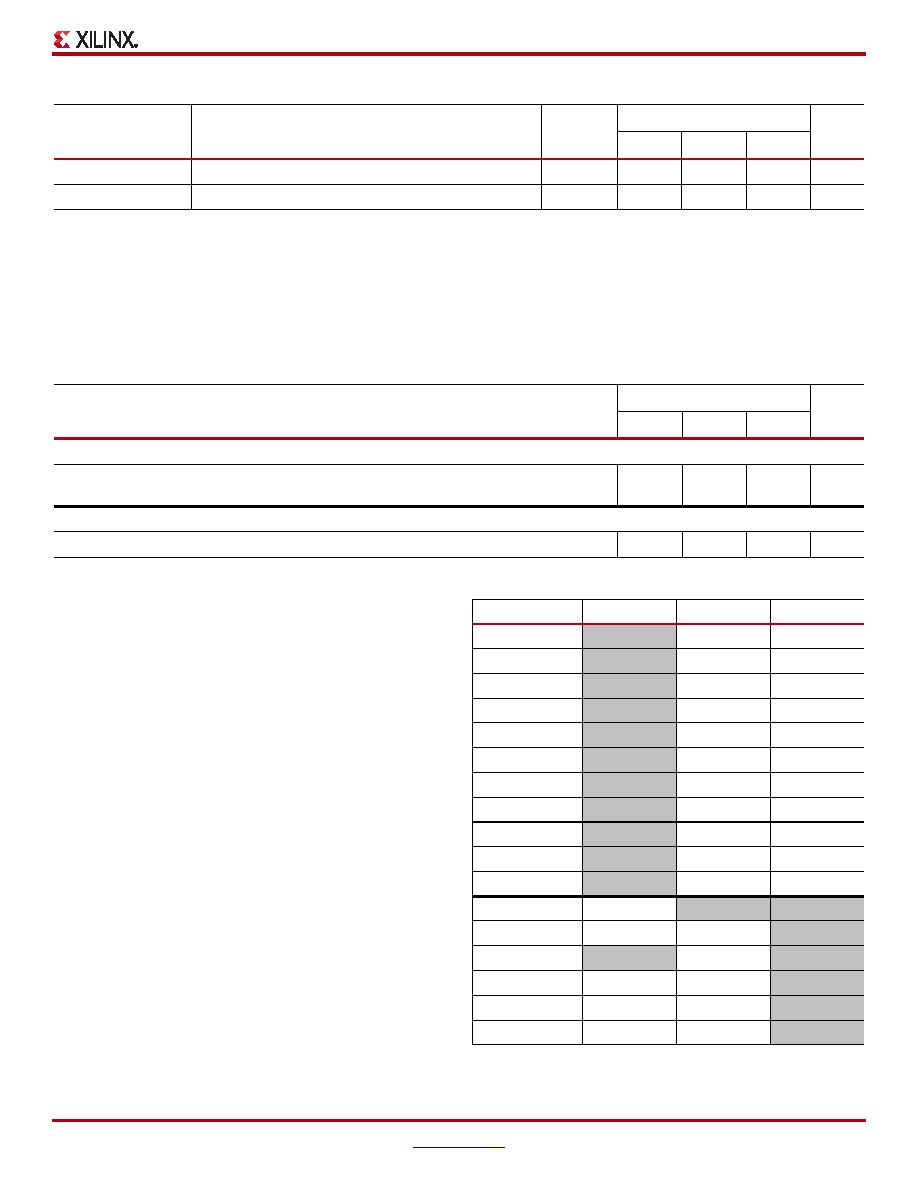

Table 63: JTAG ID Code by Step

Device

Step 0

Step 1

Step 2

XC4VLX15

35

XC4VLX25

9A

XC4VLX40

35

XC4VLX60

2 or 3

4 or 5

XC4VLX80

35

XC4VLX100

2 or 3

4 or 5

XC4VLX160

0 or 3

4 or 5

XC4VLX200

0 or 3

2 or 5

XC4VSX25

24

XC4VSX35

24

XC4VSX55

24

XC4VFX12

0 or 2

XC4VFX20

26

XC4VFX40

0

XC4VFX60

28

XC4VFX100

06

XC4VFX140

04

Notes:

1.

Shaded cells represent devices not produced at that stepping.

相关PDF资料 |

PDF描述 |

|---|---|

| XC4VLX15-12FFG676C | FPGA, 1536 CLBS, 1205 MHz, PBGA676 |

| XC4VFX100-10FF1152I | FPGA, 10544 CLBS, 1028 MHz, PBGA1152 |

| XC4VFX100-10FF1517I | FPGA, 10544 CLBS, 1028 MHz, PBGA1517 |

| XC4VFX100-11FF1152I | FPGA, 10544 CLBS, 1181 MHz, PBGA1152 |

| XC4VFX100-11FF1517I | FPGA, 10544 CLBS, 1181 MHz, PBGA1517 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC4VLX15-11SF363C | 制造商:Xilinx 功能描述:FPGA VIRTEX-4 13824 CELLS 90NM 1.2V 363FCBGA - Trays |

| XC4VLX15-11SF363I | 功能描述:IC FPGA VIRTEX-4LX 363FCBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Virtex®-4 LX 产品变化通告:Step Intro and Pkg Change 11/March/2008 标准包装:1 系列:Virtex®-5 SXT LAB/CLB数:4080 逻辑元件/单元数:52224 RAM 位总计:4866048 输入/输出数:480 门数:- 电源电压:0.95 V ~ 1.05 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:1136-BBGA,FCBGA 供应商设备封装:1136-FCBGA 配用:568-5088-ND - BOARD DEMO DAC1408D750122-1796-ND - EVALUATION PLATFORM VIRTEX-5 |

| XC4VLX15-11SFG363C | 功能描述:IC FPGA VIRTEX-4 LX 15K 363FCBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Virtex®-4 LX 产品变化通告:Step Intro and Pkg Change 11/March/2008 标准包装:1 系列:Virtex®-5 SXT LAB/CLB数:4080 逻辑元件/单元数:52224 RAM 位总计:4866048 输入/输出数:480 门数:- 电源电压:0.95 V ~ 1.05 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:1136-BBGA,FCBGA 供应商设备封装:1136-FCBGA 配用:568-5088-ND - BOARD DEMO DAC1408D750122-1796-ND - EVALUATION PLATFORM VIRTEX-5 |

| XC4VLX15-11SFG363I | 功能描述:IC FPGA VIRTEX-4 LX 15K 363FCBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Virtex®-4 LX 产品变化通告:Step Intro and Pkg Change 11/March/2008 标准包装:1 系列:Virtex®-5 SXT LAB/CLB数:4080 逻辑元件/单元数:52224 RAM 位总计:4866048 输入/输出数:480 门数:- 电源电压:0.95 V ~ 1.05 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:1136-BBGA,FCBGA 供应商设备封装:1136-FCBGA 配用:568-5088-ND - BOARD DEMO DAC1408D750122-1796-ND - EVALUATION PLATFORM VIRTEX-5 |

| XC4VLX15-12FF668C | 制造商:Xilinx 功能描述:FPGA VIRTEX-4 13824 CELLS 90NM 1.2V 668FCBGA - Trays |

发布紧急采购,3分钟左右您将得到回复。