- 您现在的位置:买卖IC网 > PDF目录225572 > XC4VLX15-11FFG676I (XILINX INC) FPGA, 1536 CLBS, 1205 MHz, PBGA676 PDF资料下载

参数资料

| 型号: | XC4VLX15-11FFG676I |

| 厂商: | XILINX INC |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 1536 CLBS, 1205 MHz, PBGA676 |

| 封装: | LEAD FREE, FBGA-676 |

| 文件页数: | 7/58页 |

| 文件大小: | 1863K |

| 代理商: | XC4VLX15-11FFG676I |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页

Virtex-4 FPGA Data Sheet: DC and Switching Characteristics

DS302 (v3.7) September 9, 2009

Product Specification

15

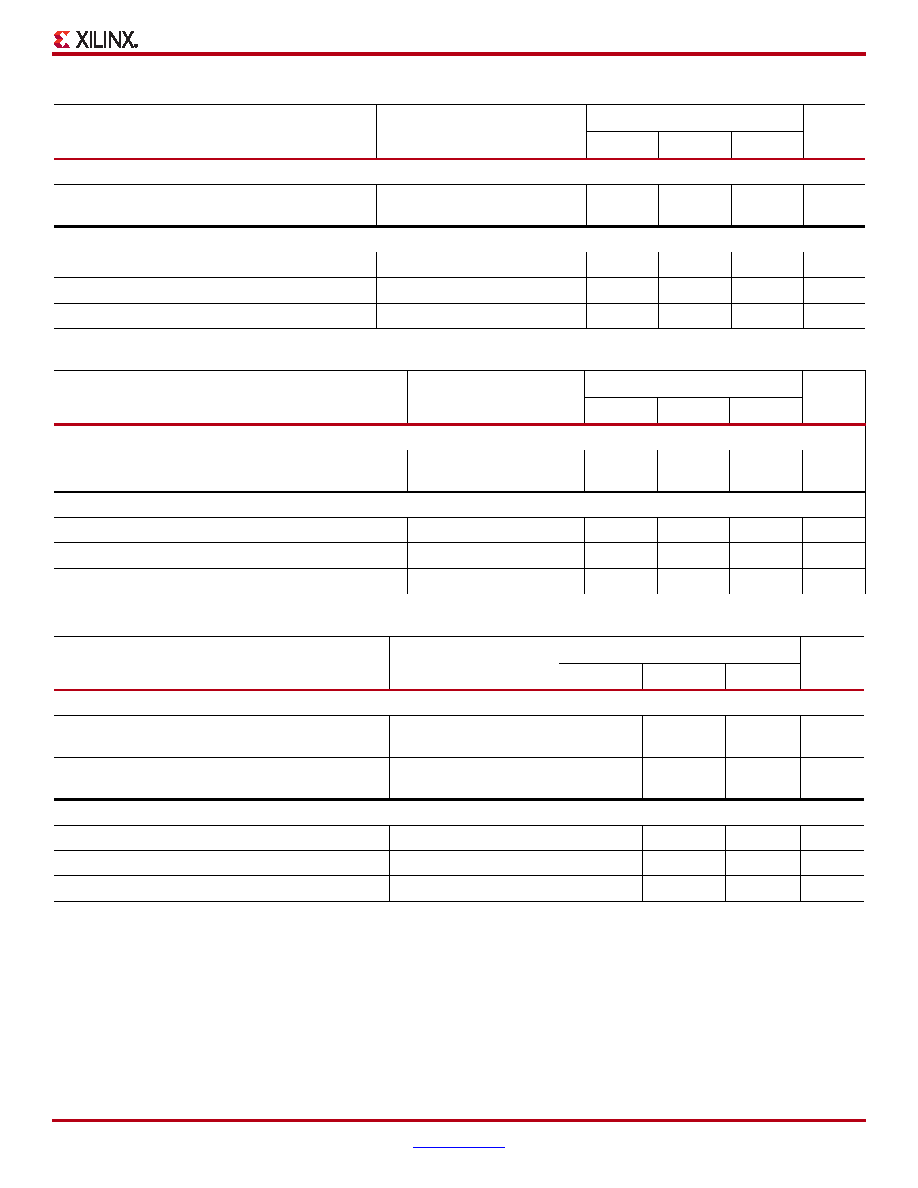

Table 19: PowerPC 405 Data-Side On-Chip Memory Switching Characteristics

Description

Symbol

Speed Grade

Units

-12

-11

-10

Setup and Hold Relative to Clock (BRAMDSOCMCLK)

Data-Side On-Chip Memory data bus inputs

TPPCDCK_DSOCMRDDB

TPPCCKD_DSOCMRDDB

0.60

0.20

0.65

0.20

0.74

0.23

ns, Min

Clock to Out

Data-Side On-Chip Memory control outputs

TPPCCKO_BRAMBWR

2.07

2.30

2.65

ns, Max

Data-Side On-Chip Memory address bus outputs

TPPCCKO_BRAMABUS

2.07

2.30

2.65

ns, Max

Data-Side On-Chip Memory data bus outputs

TPPCCKO_IBRAMWRDBUS01

1.61

1.79

2.06

ns, Max

Table 20: PowerPC 405 Instruction-Side On-Chip Memory Switching Characteristics

Description

Symbol

Speed Grade

Units

-12

-11

-10

Setup and Hold Relative to Clock (BRAMISOCMCLK)

Instruction-Side On-Chip Memory data bus inputs

TPPCDCK_ISOCMRDDB

TPPCCKD_ISOCMRDDB

0.74

0.20

0.82

0.20

0.94

0.23

ns, Min

Clock to Out

Instruction-Side On-Chip Memory control outputs

TPPCCKO_IBRAMEN

3.04

3.37

3.88

ns, Max

Instruction-Side On-Chip Memory address bus outputs

TPPCCKO_IBRAMRDABUS

1.67

1.85

2.13

ns, Max

Instruction-Side On-Chip Memory data bus outputs

TPPCCKO_IBRAMWRDBUS

1.67

1.86

2.14

ns, Max

Table 21: Processor Block DCR Bus Switching Characteristics

Description

Symbol

Speed Grade

Units

-12

-11

-10

Setup and Hold Relative to Clock (CPMDCRCLOCK)

Device Control Register Bus control inputs

TPPCDCK_EXDCRACK

TPPCCKD_EXDCRACK

0.12

0.15

0.13

0.17

0.15

0.19

ns, Min

Device Control Register Bus data inputs

TPPCDCK_EXDCRDBUSI

TPPCCKD_EXDCRDBUSI

0.57

0.16

0.57

0.16

1.02

0.27

ns, Min

Clock to Out

Device Control Register Bus control outputs

TPPCCKO_EXDCRRD

1.20

1.35

1.54

ns, Max

Device Control Register Bus address bus outputs

TPPCCKO_EXDCRABUS

1.28

1.45

1.66

ns, Max

Device Control Register Bus data bus outputs

TPPCCKO_EXDCRDBUSO

1.31

1.45

1.67

ns, Max

相关PDF资料 |

PDF描述 |

|---|---|

| XC4VLX15-12FFG676C | FPGA, 1536 CLBS, 1205 MHz, PBGA676 |

| XC4VFX100-10FF1152I | FPGA, 10544 CLBS, 1028 MHz, PBGA1152 |

| XC4VFX100-10FF1517I | FPGA, 10544 CLBS, 1028 MHz, PBGA1517 |

| XC4VFX100-11FF1152I | FPGA, 10544 CLBS, 1181 MHz, PBGA1152 |

| XC4VFX100-11FF1517I | FPGA, 10544 CLBS, 1181 MHz, PBGA1517 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC4VLX15-11SF363C | 制造商:Xilinx 功能描述:FPGA VIRTEX-4 13824 CELLS 90NM 1.2V 363FCBGA - Trays |

| XC4VLX15-11SF363I | 功能描述:IC FPGA VIRTEX-4LX 363FCBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Virtex®-4 LX 产品变化通告:Step Intro and Pkg Change 11/March/2008 标准包装:1 系列:Virtex®-5 SXT LAB/CLB数:4080 逻辑元件/单元数:52224 RAM 位总计:4866048 输入/输出数:480 门数:- 电源电压:0.95 V ~ 1.05 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:1136-BBGA,FCBGA 供应商设备封装:1136-FCBGA 配用:568-5088-ND - BOARD DEMO DAC1408D750122-1796-ND - EVALUATION PLATFORM VIRTEX-5 |

| XC4VLX15-11SFG363C | 功能描述:IC FPGA VIRTEX-4 LX 15K 363FCBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Virtex®-4 LX 产品变化通告:Step Intro and Pkg Change 11/March/2008 标准包装:1 系列:Virtex®-5 SXT LAB/CLB数:4080 逻辑元件/单元数:52224 RAM 位总计:4866048 输入/输出数:480 门数:- 电源电压:0.95 V ~ 1.05 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:1136-BBGA,FCBGA 供应商设备封装:1136-FCBGA 配用:568-5088-ND - BOARD DEMO DAC1408D750122-1796-ND - EVALUATION PLATFORM VIRTEX-5 |

| XC4VLX15-11SFG363I | 功能描述:IC FPGA VIRTEX-4 LX 15K 363FCBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Virtex®-4 LX 产品变化通告:Step Intro and Pkg Change 11/March/2008 标准包装:1 系列:Virtex®-5 SXT LAB/CLB数:4080 逻辑元件/单元数:52224 RAM 位总计:4866048 输入/输出数:480 门数:- 电源电压:0.95 V ~ 1.05 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:1136-BBGA,FCBGA 供应商设备封装:1136-FCBGA 配用:568-5088-ND - BOARD DEMO DAC1408D750122-1796-ND - EVALUATION PLATFORM VIRTEX-5 |

| XC4VLX15-12FF668C | 制造商:Xilinx 功能描述:FPGA VIRTEX-4 13824 CELLS 90NM 1.2V 668FCBGA - Trays |

发布紧急采购,3分钟左右您将得到回复。