参数资料

| 型号: | XRT75R12DIB-L |

| 厂商: | Exar Corporation |

| 文件页数: | 32/133页 |

| 文件大小: | 0K |

| 描述: | IC LIU E3/DS3/STS-1 12CH 420TBGA |

| 标准包装: | 40 |

| 类型: | 线路接口装置(LIU) |

| 驱动器/接收器数: | 12/12 |

| 规程: | DS3,E3,STS-1 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 420-LBGA 裸露焊盘 |

| 供应商设备封装: | 420-TBGA(35x35) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页当前第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页

XRT75R12D

123

REV. 1.0.3

TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER

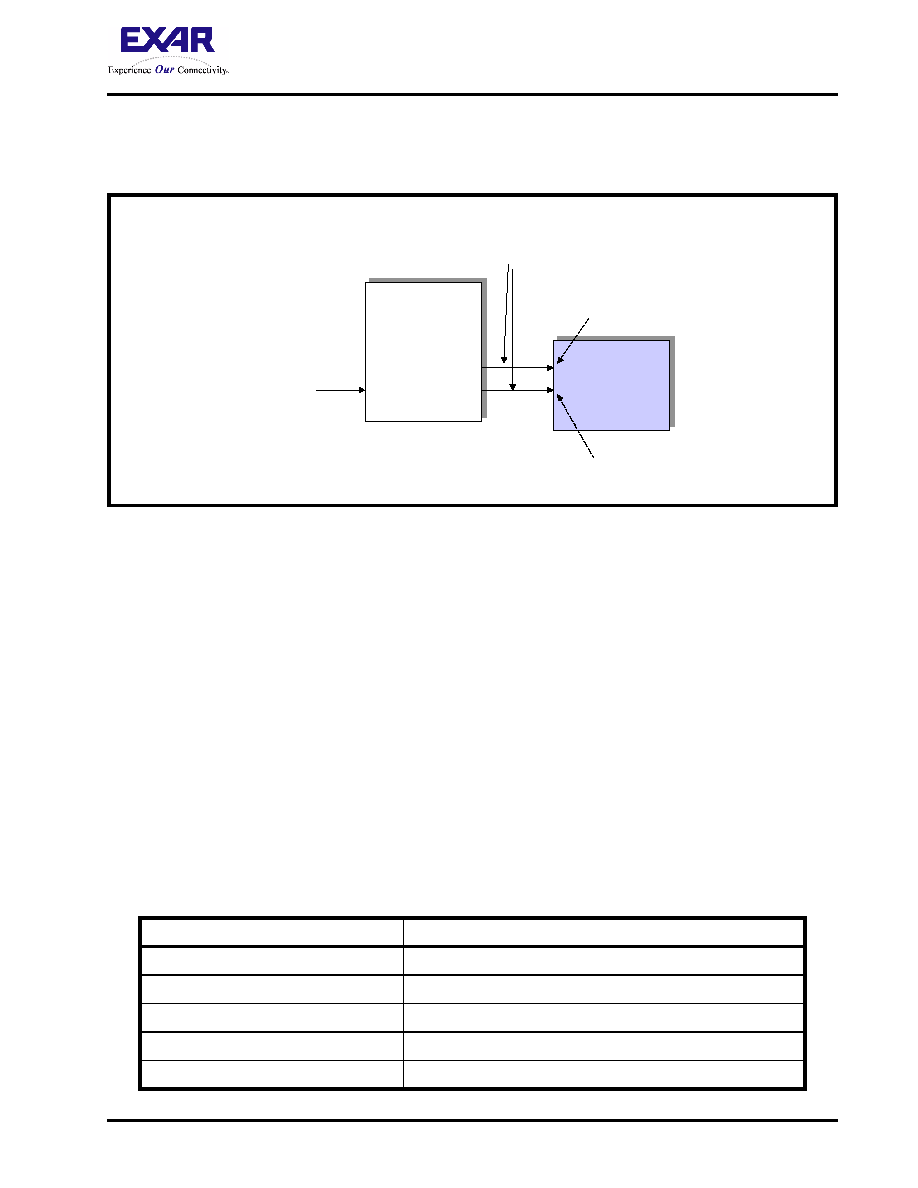

output a DS3 line signal (to the DS3 facility) that complies with the "Category I Intrinsic Jitter Requirements -

per Telcordia GR-253-CORE (for DS3 applications). This scheme is illustrated below in Figure 71.

8.8.3

How does the LIU permit the user to comply with the SONET APS Recovery Time

requirements of 50ms (per Telcordia GR-253-CORE)?

Telcordia GR-253-CORE, Section 5.3.3.3 mandates that the "APS Completion" (or Recovery) time be 50ms or

less. Many of our customers interpret this particular requirement as follows.

"From the instant that an APS is initiated on a high-speed SONET signal, all lower-speed SONET traffic (which

is being transported via this "high-speed" SONET signal) must be fully restored within 50ms. Similarly, if the

"high-speed" SONET signal is transporting some PDH signals (such as DS1 or DS3, etc.), then those entities

that are responsible for acquiring and maintaining DS1 or DS3 frame synchronization (with these DS1 or DS3

data-streams that have been de-mapped from SONET) must have re-acquired DS1 or DS3 frame

synchronization within 50ms" after APS has been initiated."

The LIU was designed such that the DS3 signals that it receives from a SONET Mapper device and processes

will comply with the Category I Intrinsic Jitter requirements per Telcordia GR-253-CORE.

Reference 1 documents some APS Recovery Time testing, which was performed to verify that the Jitter

Attenuator blocks (within the LIU) device that permit it to comply with the Category I Intrinsic Jitter

Requirements (for DS3 Applications) per Telcordia GR-253-CORE, do not cause it to fail to comply with the

"APS Completion Time" requirements per Section 5.3.3.3 of Telcordia GR-253-CORE. However, Table 50

presents a summary of some APS Recovery Time requirements that were documented within this test report.

FIGURE 71. SIMPLE ILLUSTRATION OF THE LIU BEING USED IN A SONET DE-SYNCHRONIZER" APPLICATION

TABLE 50: MEASURED APS RECOVERY TIME AS A FUNCTION OF DS3 PPM OFFSET

DS3 PPM OFFSET (PER W&G ANT-20SE)

MEASURED APS RECOVERY TIME (PER LOGIC ANALYZER)

-99 ppm

1.25ms

-40ppm

1.54ms

-30 ppm

1.34ms

-20 ppm

1.49ms

-10 ppm

1.30ms

DS3 to STS-N

Mapper/

Demapper

IC

DS3 to STS-N

Mapper/

Demapper

IC

LIU

STS-N Signal

TPDATA_n input pin

TCLK_n input

De-Mapped (Gapped)

DS3 Data and Clock

相关PDF资料 |

PDF描述 |

|---|---|

| XRT75R12IB-L | IC LIU E3/DS3/STS-1 12CH 420TBGA |

| XRT75VL00DIV | IC LIU E3/DS3/STS-1 1CH 52TQFP |

| XRT75VL00IV-F | IC LIU E3/DS3/STS-1 1CH 52TQFP |

| XRT79L71IB-F | IC LIU/FRAMER DS3/E3 1CH 208BGA |

| XRT81L27IV-F | IC LIU EI 7CH 3.3V 128TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XRT75R12ES | 功能描述:时钟合成器/抖动清除器 12CH T3/E3/STS1LIUJA 3.3V W/REDUNDANCY RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

| XRT75R12IB | 功能描述:外围驱动器与原件 - PCI 12CH E3/DS3/STS W/JITTER R3 TECH RoHS:否 制造商:PLX Technology 工作电源电压: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:FCBGA-1156 封装:Tray |

| XRT75R12IB-F | 功能描述:外围驱动器与原件 - PCI 12 Channel 3.3V-5V temp -45 to 85C RoHS:否 制造商:PLX Technology 工作电源电压: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:FCBGA-1156 封装:Tray |

| XRT75R12IB-L | 功能描述:LIN 收发器 Attenuator RoHS:否 制造商:NXP Semiconductors 工作电源电压: 电源电流: 最大工作温度: 封装 / 箱体:SO-8 |

| XRT75VL00 | 制造商:EXAR 制造商全称:EXAR 功能描述:E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR |

发布紧急采购,3分钟左右您将得到回复。