- 您现在的位置:买卖IC网 > PDF目录15166 > ZL6105ALAFTK (Intersil)IC REG CTRLR BUCK PWM VM 36-QFN PDF资料下载

参数资料

| 型号: | ZL6105ALAFTK |

| 厂商: | Intersil |

| 文件页数: | 22/35页 |

| 文件大小: | 0K |

| 描述: | IC REG CTRLR BUCK PWM VM 36-QFN |

| 标准包装: | 1,000 |

| PWM 型: | 电压模式 |

| 输出数: | 1 |

| 频率 - 最大: | 1.4MHz |

| 占空比: | 95% |

| 电源电压: | 3 V ~ 14 V |

| 降压: | 是 |

| 升压: | 无 |

| 回扫: | 无 |

| 反相: | 无 |

| 倍增器: | 无 |

| 除法器: | 无 |

| Cuk: | 无 |

| 隔离: | 无 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 36-VFQFN 裸露焊盘 |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页当前第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页

�� �

�

�

�ZL6105�

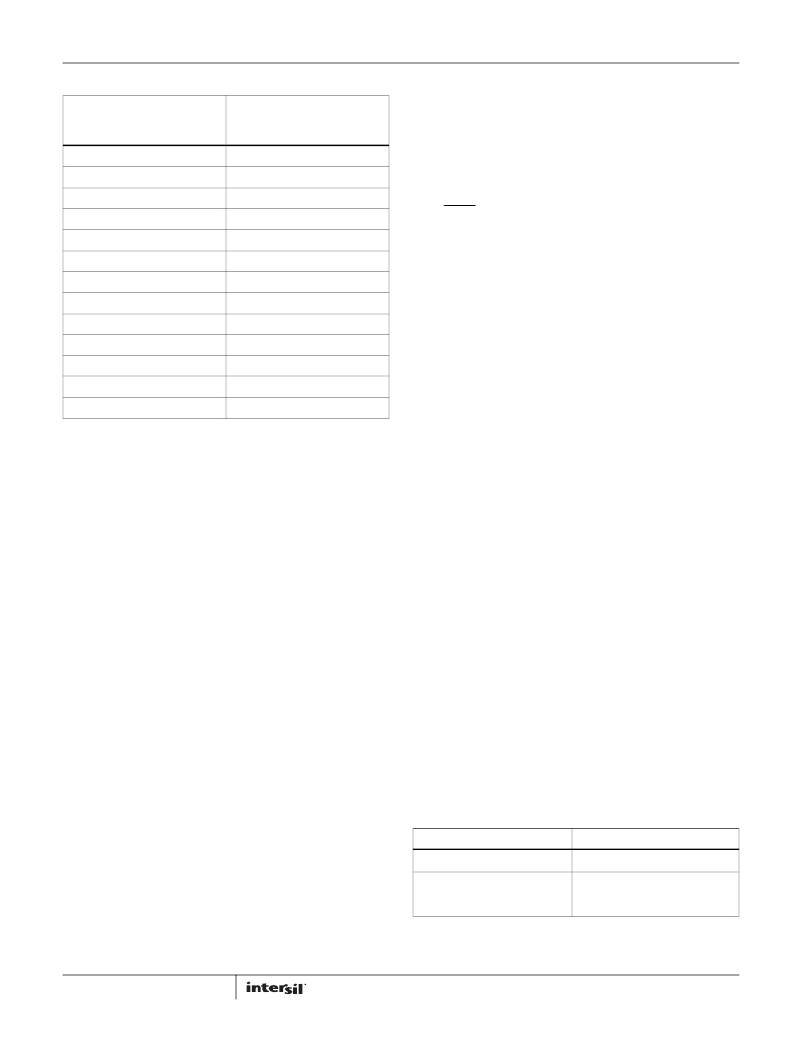

�TABLE� 17.� FC1� PIN-STRAP� SETTINGS�

�bottom� MOSFETs� are� simultaneously� on� for� periods� of� time�

�exceeding� a� few� nanoseconds.� Conversely,� long� periods� of� time� in�

�which� both� MOSFETs� are� off� reduce� overall� circuit� efficiency� by�

�FC1� PIN�

�LOW�

�OPEN�

�AUTO� COMP� GAIN�

�100%�

�50%�

�allowing� current� to� flow� in� their� parasitic� body� diodes.�

�It� is� therefore� advantageous� to� minimize� this� dead-time� to�

�provide� optimum� circuit� efficiency.� In� the� first� order� model� of� a�

�buck� converter,� the� duty� cycle� is� determined� by� Equation� 32:�

�HIGH�

�10k� ?�

�30%�

�10%�

�D� ≈�

�V� OUT�

�V� IN�

�(EQ.� 32)�

�11k� ?�

�12.1k� ?�

�13.3k� ?�

�14.7k� ?�

�16.2k� ?�

�17.8k� ?�

�19.6k� ?�

�21.5k� ?�

�23.7k� ?�

�20%�

�30%�

�40%�

�50%�

�60%�

�70%�

�80%�

�90%�

�100%�

�However,� non-idealities� exist� that� cause� the� real� duty� cycle� to�

�extend� beyond� the� ideal.� Dead-time� is� one� of� those� non-idealities�

�that� can� be� manipulated� to� improve� efficiency.� The� ZL6105� has�

�an� internal� algorithm� that� constantly� adjusts� dead-time�

�non-overlap� to� minimize� duty� cycle,� thus� maximizing� efficiency.�

�This� circuit� will� null� out� dead-time� differences� due� to� component�

�variation,� temperature,� and� loading� effects.�

�This� algorithm� is� independent� of� application� circuit� parameters� such�

�as� MOSFET� type,� gate� driver� delays,� rise� and� fall� times� and� circuit�

�layout.� In� addition,� it� does� not� require� drive� or� MOSFET� voltage� or�

�current� waveform� measurements.�

�Adaptive� Diode� Emulation�

�Non-linear� Response� (NLR)� Settings�

�The� ZL6105� incorporates� a� non-linear� response� (NLR)� loop� that�

�decreases� the� response� time� and� the� output� voltage� deviation� in�

�the� event� of� a� sudden� output� load� current� step.� The� NLR� loop�

�incorporates� a� secondary� error� signal� processing� path� that�

�bypasses� the� primary� error� loop� when� the� output� begins� to�

�transition� outside� of� the� standard� regulation� limits.� This� scheme�

�results� in� a� higher� equivalent� loop� bandwidth� than� what� is�

�possible� using� a� traditional� linear� loop.�

�When� a� load� current� step� function� imposed� on� the� output� causes�

�the� output� voltage� to� drop� below� the� lower� regulation� limit,� the�

�NLR� circuitry� will� force� a� positive� correction� signal� that� will� turn�

�on� the� upper� MOSFET� and� quickly� force� the� output� to� increase.�

�Conversely,� a� negative� load� step� (i.e.� removing� a� large� load�

�current)� will� cause� the� NLR� circuitry� to� force� a� negative� correction�

�signal� that� will� turn� on� the� lower� MOSFET� and� quickly� force� the�

�output� to� decrease.�

�NLR� can� be� configured� using� resistor� pin-straps� as� follows:�

�?� CFG0� disables� NLR� or� enables� NLR� inner� thresholds� to� 1.5%,�

�2%� or� 3%� (see� Table� 29).�

�?� CFG1� sets� NLR� inner� thresholds� timeout� and� blanking� to� 1� and�

�4� or� 2� and� 8� (see� Table� 26).�

�Please� refer� to� Application� Note� AN2032� for� more� details�

�regarding� NLR� settings.�

�Most� power� converters� use� synchronous� rectification� to� optimize�

�efficiency� over� a� wide� range� of� input� and� output� conditions.�

�However,� at� light� loads� the� synchronous� MOSFET� will� typically�

�sink� current� and� introduce� additional� energy� losses� associated�

�with� higher� peak� inductor� currents,� resulting� in� reduced�

�efficiency.� Adaptive� diode� emulation� mode� turns� off� the� low-side�

�FET� gate� drive� at� low� load� currents� to� prevent� the� inductor� current�

�from� going� negative,� reducing� the� energy� losses� and� increasing�

�overall� efficiency.�

�Note:� the� overall� bandwidth� of� the� device� may� be� reduced� when�

�in� diode� emulation� mode.� It� is� recommended� that� diode�

�emulation� is� disabled� prior� to� applying� significant� load� steps.�

�Power� Management� Functional�

�Description�

�Input� Undervoltage� Lockout�

�The� input� undervoltage� lockout� (UVLO)� prevents� the� ZL6105� from�

�operating� when� the� input� falls� below� a� preset� threshold,�

�indicating� the� input� supply� is� out� of� its� specified� range.� The� UVLO�

�threshold� (V� UVLO� )� can� be� set� between� 2.85V� and� 16V� using� the�

�UVLO� pin.� The� simplest� implementation� is� to� connect� the� UVLO�

�pin� as� shown� in� Table� 18.� If� the� UVLO� pin� is� left� unconnected,� the�

�UVLO� threshold� will� default� to� 4.5V.�

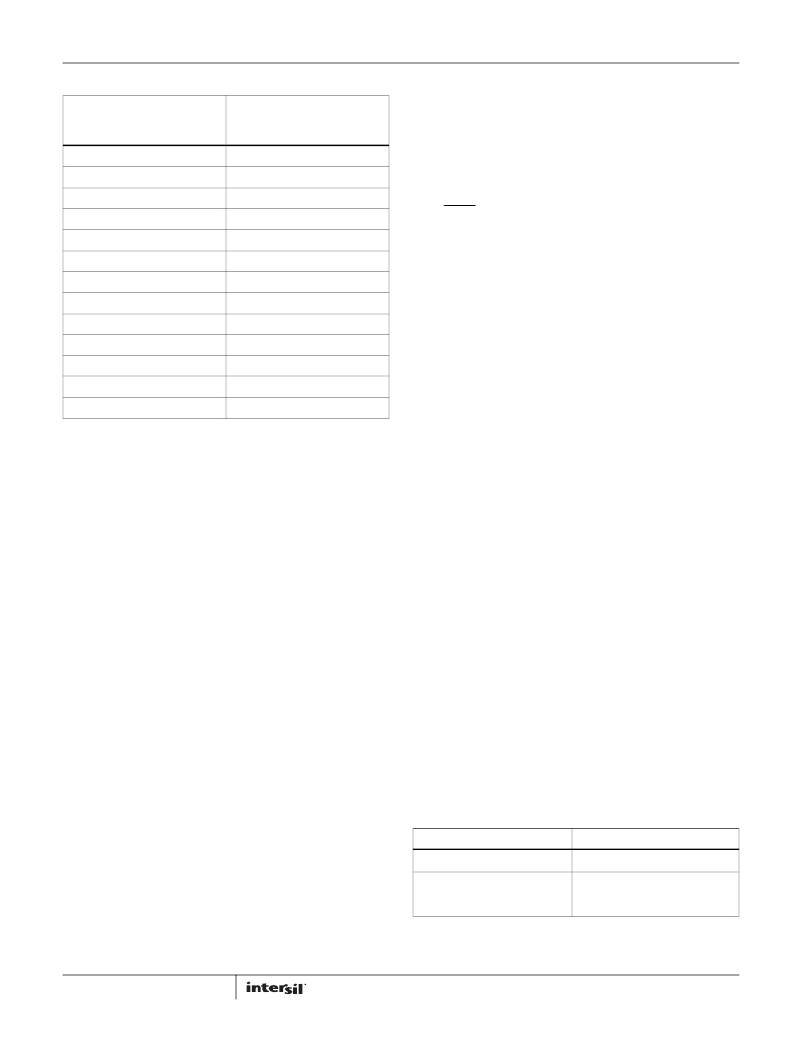

�TABLE� 18.� UVLO� THRESHOLD� PIN-STRAP� SETTINGS�

�Efficiency� Optimized� Driver� Dead-time�

�Control�

�The� ZL6105� utilizes� a� closed� loop� algorithm� to� optimize� the�

�dead-time� applied� between� the� gate� drive� signals� for� the� top� and�

�bottom� FETs.� In� a� synchronous� buck� converter,� the� MOSFET� drive�

�circuitry� must� be� designed� such� that� the� top� and� bottom�

�MOSFETs� are� never� in� the� conducting� state� at� the� same� time.�

�Potentially� damaging� currents� flow� in� the� circuit� if� both� top� and�

�22�

�UVLO� PIN�

�LOW�

�OPEN�

�HIGH�

�UVLO� THRESHOLD� (V)�

�3�

�4.5�

�10.8�

�FN6906.5�

�December� 19,� 2013�

�相关PDF资料 |

PDF描述 |

|---|---|

| RBM18DREI | CONN EDGECARD 36POS .156 EYELET |

| B43086F2476M | 47UF 250V 16X20 SINGLE END |

| ISL6307CRZ-T | IC REG CTRLR BUCK PWM VM 48-QFN |

| ISL6401CB-T | IC REG CTRLR PWM CM 14-SOIC |

| GCM18DREF | CONN EDGECARD 36POS .156 EYELET |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ZL6105ALAFTKR5546 | 功能描述:DC/DC 开关控制器 RoHS:否 制造商:Texas Instruments 输入电压:6 V to 100 V 开关频率: 输出电压:1.215 V to 80 V 输出电流:3.5 A 输出端数量:1 最大工作温度:+ 125 C 安装风格: 封装 / 箱体:CPAK |

| ZL6105ALAFTKR5549 | 制造商:Intersil Corporation 功能描述:ADAPTIVE DIGITAL DC-DC CONTROLLER W/ DRIVERS & I-SHARING FE0 - Tape and Reel |

| ZL6105ALAFTKR5553 | 制造商:Intersil Corporation 功能描述:ADAPTIVE DIGITAL DC-DC CONTROLLER W/ DRIVERS & I-SHARING MOD - Tape and Reel |

| ZL6105ALAFTKR5554 | 制造商:Intersil Corporation 功能描述:ADAPTIVE DIGITAL DC-DC CONTROLLER W/ DRIVERS & I-SHARING MOD - Tape and Reel |

| ZL6105ALAFTR5546 | 功能描述:IC REG CTRLR BUCK PWM VM 36-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。