- 您现在的位置:买卖IC网 > PDF目录11767 > AD6620ASZ-REEL (Analog Devices Inc)IC DGTL RCVR DUAL 67MSPS 80-PQFP PDF资料下载

参数资料

| 型号: | AD6620ASZ-REEL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 11/44页 |

| 文件大小: | 0K |

| 描述: | IC DGTL RCVR DUAL 67MSPS 80-PQFP |

| 标准包装: | 500 |

| 接口: | 并行/串行 |

| 电源电压: | 3 V ~ 3.6 V |

| 封装/外壳: | 80-BQFP |

| 供应商设备封装: | 80-PQFP(14x14) |

| 包装: | 带卷 (TR) |

| 安装类型: | 表面贴装 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

AD6620

–19–

REV. A

SCLK

AD6620

DSP

+3.3V

SBM

SCLK

SDI

DT

SDO

DR

SDFS

RFS

SDFE

10k

SDIV

2

4

AD

WL

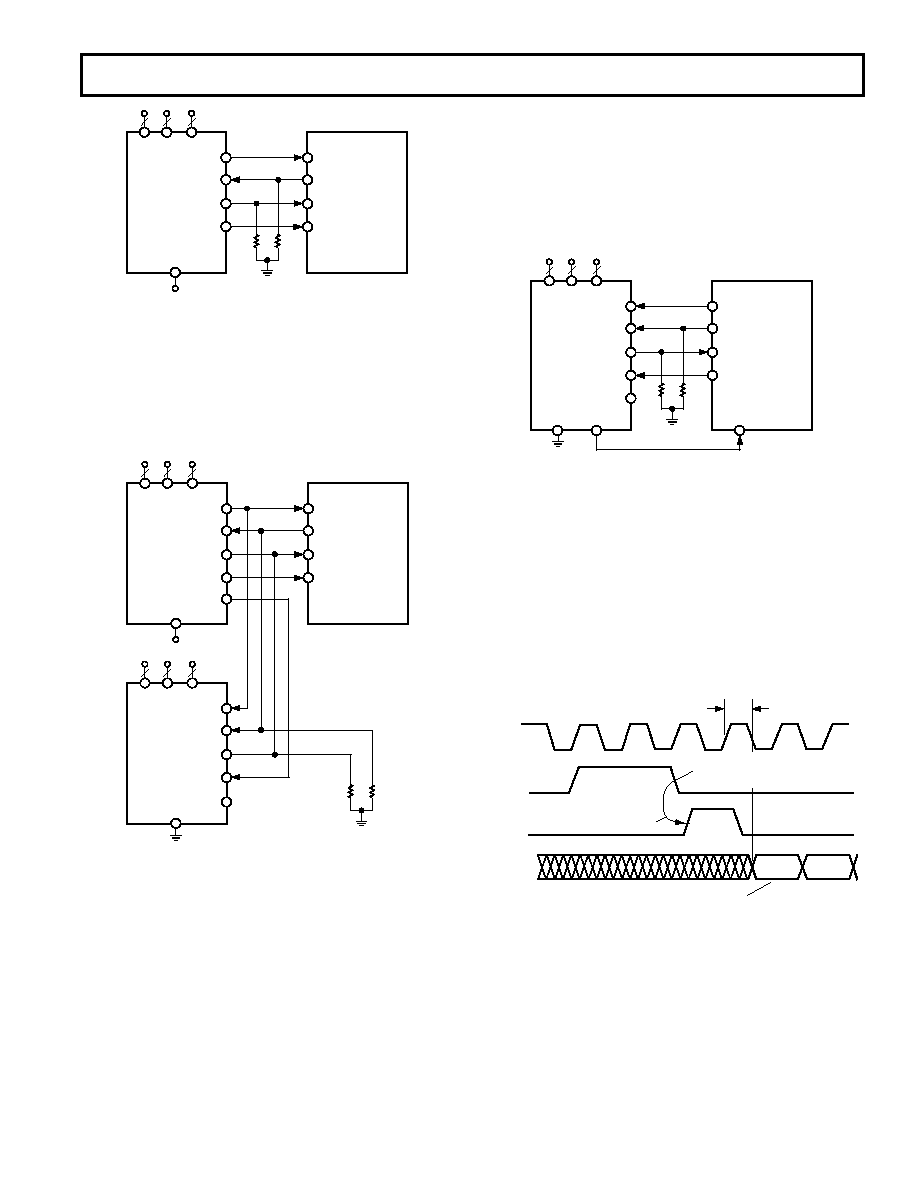

Figure 30. Typical Serial Data Output Interface to DSP

(Serial Master Mode, SBM = 1)

Figure 31 shows two AD6620s illustrating the cascade capability

for the chip. The first is connected as a serial master and the

second is configured in serial cascade mode. The SDFE signal

of the master is connected to the SDFS of the slave. This allows

the master AD6620 data to be obtained first by the DSP, fol-

lowed by the cascaded AD6620 data.

SCLK

AD6620

DSP

+3.3V

SBM

SCLK

SDI

DT

SDO

DR

SDFS

RFS

SDFE

10k

SDIV

2

4

AD

WL

10k

SCLK

AD6620

CASCADE

SBM

SDI

SDO

SDFS

SDFE

SDIV

2

4

AD

WL

Figure 31. Typical Serial Data Output Interface to DSP

(Serial Cascade Mode, SBM = 0)

The AD6620 also supports a serial slave mode, where the serial

clock and interface is provided by a DSP or ASIC that is set to

operate in the master mode. Note that the AD6620 cannot be

booted through the serial port. The microport must be used to

initialize the device, then serial operation is supported.

In the serial slave mode, DVOUT is valid and indicates the pres-

ence of a new word in the output buffers of the shift register.

This pin may thus be used by the DSP to generate an interrupt

to service the serial port. The DSP then generates an SFDS

pulse to drive the AD6620. The first serial clock rising edge

after SDFS makes the first bit available at SDO. The falling

edge of serial clock can be used to sample the data. The total

number of bits are then read from the AD6620 (determined by

the serial port word length). If the DSP has the ability to count

bits, the DSP will know when the complete frame is read. If not,

the DSP can monitor the SDFE pin to determine that the com-

plete frame is read. The serial clock provided by the DSP can be

asynchronous with the AD6620 clock and input data.

SCLK

AD6620

DSP

SBM

SCLK

SDI

DT

SDO

DR

SDFS

RFS

SDFE

10k

SDIV

2

4

AD

WL

DVOUT

IRQ

Figure 32. Typical Serial Data Output Interface to DSP

(Serial Slave Mode, SBM = 0)

In either the serial master or slave mode, there are two con-

straints that must be observed. The first is that the clock must

be fast enough to read the serial frame prior to the next frame

becoming available. Since the AD6620 output is synchronous

with its input sample rate, the output update rate can be deter-

mined by the user-programmed decimation rate. The timing

diagram in Figure 33 details how serial slave mode is imple-

mented. The second constraint is that the time between serial

frames may be either zero SCLK periods (the end of one frame

adjoins the beginning of the next) or two or more SCLK peri-

ods. One SCLK period between frames is not allowed.

tDSO

DVOUT

SCLK

SDFS

SDO

DSP USES FALLING EDGE OF

DVOUT TO GENERATE SDFS

FIRST DATA IS AVAILABLE THE FIRST

RISING SCLK AFTER SDFS GOES HIGH

IMSB

IMSB – 1

DVOUT PULSEWIDTH IS 2 CLKIN

SINGLE CHANNEL AND 4 CLKIN

DUAL CHANNEL

Figure 33. Timing for Serial Slave Mode (SBM = 0)

FREQUENCY TRANSLATOR

The first signal processing stage is a frequency translator con-

sisting of two multipliers and a 32-bit complex numerically

controlled oscillator (NCO). The NCO serves as a quadrature

local oscillator capable of producing any analytic frequency

between –fSAMP/2 and +fSAMP/2 with a resolution of fSAMP/2

32. In

the Single Channel Real input mode, fSAMP is equal to fCLK multi-

plied by the fraction of CLK cycles that A/B is high. In the

Diversity Channel Real and Single Channel Complex input

相关PDF资料 |

PDF描述 |

|---|---|

| 6274291-2 | CONN JACK VERT PCB 75 OHM BNC |

| AD7669JNZ | IC I/O PORT 8BIT ANLG 28DIP |

| D38999/24FF11PA | CONN RCPT 11POS JAM NUT W/PINS |

| D38999/20JE26HN | CONN RCPT 26POS WALL MNT W/PINS |

| AD7569KNZ | IC I/O PORT 8BIT ANALOG 24DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD6620PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:65 MSPS Digital Receive Signal Processor |

| AD6620S | 制造商:AD 制造商全称:Analog Devices 功能描述:65 MSPS Digital Receive Signal Processor |

| AD6620S/PCB | 制造商:Analog Devices 功能描述:DUAL CHANNEL DECIMATING RECEIV 制造商:Analog Devices 功能描述:SGNL PROCESSOR 169CSPBGA - Bulk |

| AD6622 | 制造商:AD 制造商全称:Analog Devices 功能描述:Four-Channel, 75 MSPS Digital Transmit Signal Processor TSP |

| AD6622AS | 制造商:Analog Devices 功能描述:Transmit Signal Processor 128-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:4 CHANNEL 65 MSPS DIGITAL UPCONVERTER - Bulk |

发布紧急采购,3分钟左右您将得到回复。