- 您现在的位置:买卖IC网 > PDF目录11767 > AD6620ASZ-REEL (Analog Devices Inc)IC DGTL RCVR DUAL 67MSPS 80-PQFP PDF资料下载

参数资料

| 型号: | AD6620ASZ-REEL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 12/44页 |

| 文件大小: | 0K |

| 描述: | IC DGTL RCVR DUAL 67MSPS 80-PQFP |

| 标准包装: | 500 |

| 接口: | 并行/串行 |

| 电源电压: | 3 V ~ 3.6 V |

| 封装/外壳: | 80-BQFP |

| 供应商设备封装: | 80-PQFP(14x14) |

| 包装: | 带卷 (TR) |

| 安装类型: | 表面贴装 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页当前第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

AD6620

–2–

REV. A

I-RAM

256

18

C-RAM

256

20

Q-RAM

256

18

MRCF

RCF

MCICS

CIC5

SCALING

INTERLEAVE

DE-

INTERLEAVE

MULTI-

PLEXER

MCICS

CIC2

SCALING

MULTI-

PLEXER

EXP

SCALING

FREQUENCY

TRANSLATOR

3

18

I

Q

16

INPUT

DATA

3

EXP[2:0]

16

IN[15:0]

COMPLEX

NCO

fSAMP5

EXPLNV,

EXPOFF

TIMING

SYNC

I/O

CLK

A/B

RESET

SYNC RCF

SYNC CIC

SYNC NCO

PHASE

OFFSET

fSAMP2

fSAMP

MULTIPLEXER

SCALING, SOUT

SERIAL

PARALLEL

16

23

DVOUT

I/QOUT

A/BOUT

PARALLEL

OUTPUTS

AND

SERIAL I/O

16

OUT[15:0]

SCLK

SDI

SDO

SDFS

SDFE

SBM

WL[1:0]

AD

SDIV[3:0]

RCF COEFFICIENTS

NUMBER OF TAPS

DECIMATE FACTOR

ADDRESS OFFSET

CIC2, CIC5

DECIMATE FACTORS

SCALE FACTORS

NCO FREQUENCY

PHASE OFFSET

DITHER

SYNC MASK

INPUT MODE

REAL, DUAL, COMPLEX

FIXED OR WITH EXPONENT

SYNC M/S

OUTPUT

SCALE

FACTOR

JTAG

TRST

TCK

TMS

TDI

TDO

MICROPROCESSOR INTERFACE

DS

D[7:0] A[2:0]

R/W

DTACK

CS

MODE PAR/SER

CONTROL REGISTERS

MICROPORT AND

SERIAL ACCESS

(

W/R)

(RDY)

(

R/D)

OUTPUT

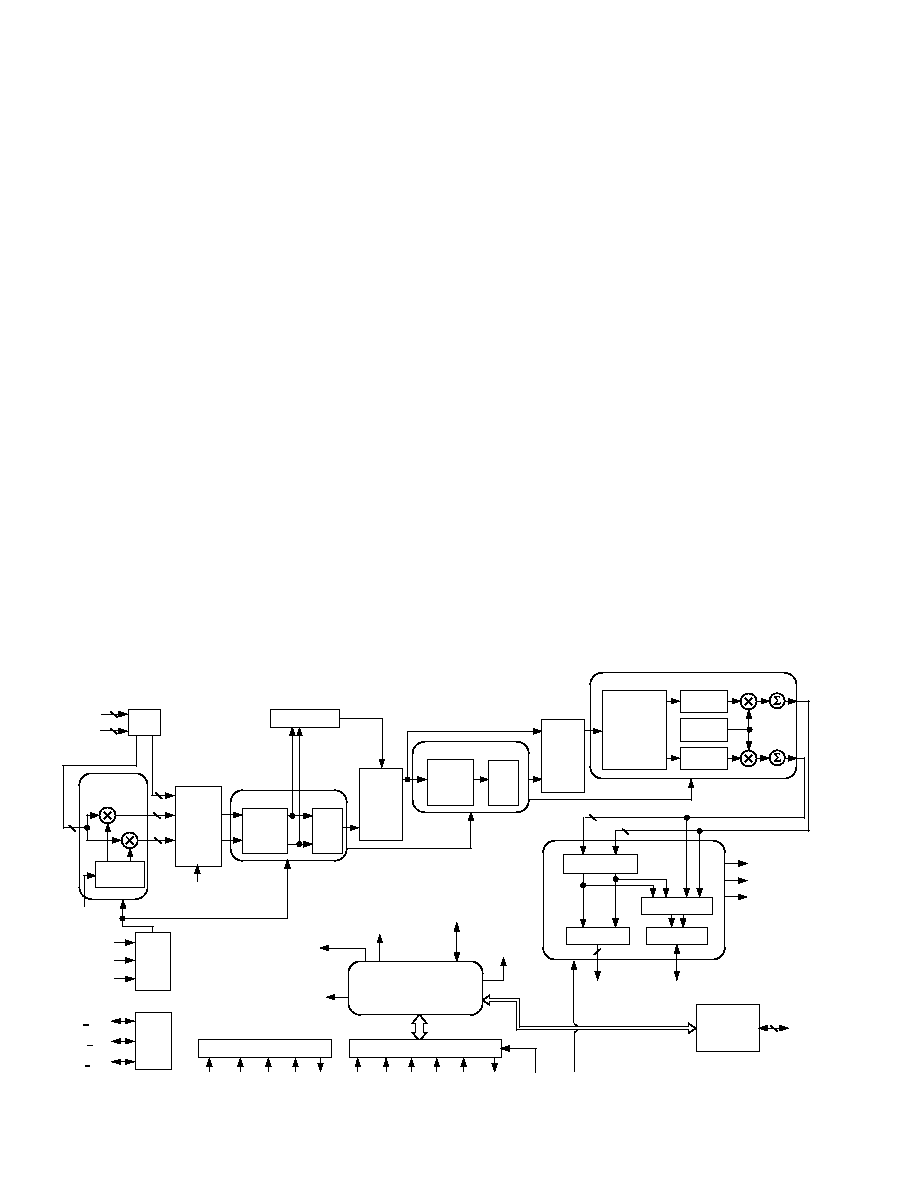

Figure 1. Block Diagram

TABLE OF CONTENTS

GENERAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . 1

ARCHITECTURE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

SPECIFICATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

TIMING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

ABSOLUTE MAXIMUM RATINGS . . . . . . . . . . . . . . . . 11

EXPLANATION OF TEST LEVELS . . . . . . . . . . . . . . . . 11

ORDERING GUIDE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

PIN FUNCTION DESCRIPTIONS . . . . . . . . . . . . . . . . . 12

PIN CONFIGURATIONS . . . . . . . . . . . . . . . . . . . . . . . . . 13

INPUT DATA PORT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

OUTPUT DATA PORT . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

FREQUENCY TRANSLATOR . . . . . . . . . . . . . . . . . . . . . 19

SECOND ORDER CASCADED INTEGRATOR

COMB FILTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

FIFTH ORDER CASCADED INTEGRATOR

COMB FILTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

RAM COEFFICIENT FILTER . . . . . . . . . . . . . . . . . . . . . 25

CONTROL REGISTERS AND ON-CHIP RAM . . . . . . . 27

PROGRAMMING THE AD6620 . . . . . . . . . . . . . . . . . . . 30

ACCESS PROTOCOLS . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

MICROPORT CONTROL . . . . . . . . . . . . . . . . . . . . . . . . 32

SERIAL PORT CONTROL . . . . . . . . . . . . . . . . . . . . . . . . 35

JTAG BOUNDARY SCAN . . . . . . . . . . . . . . . . . . . . . . . . 37

APPLICATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

OUTLINE DIMENSIONS . . . . . . . . . . . . . . . . . . . . . . . . . 44

ARCHITECTURE

As shown in Figure 1, the AD6620 has four main signal pro-

cessing stages: a Frequency Translator, two Cascaded Integrator

Comb FIR Filters (CIC2, CIC5), and a RAM Coefficient FIR

Filter (RCF). Multiple modes are supported for clocking data

into and out of the chip. Programming and control is accom-

plished via serial and microprocessor interfaces.

Input data to the chip may be real or complex. If the input data

is real, it may be clocked in as a single channel or interleaved

with a second channel. The two-channel input mode, called

Diversity Channel Real, is typically used in diversity receiver

applications. Input data is clocked in 16-bit parallel words,

IN[15:0]. This word may be combined with exponent input bits

EXP[2:0] when the AD6620 is being driven by floating-point or

gain-ranging analog-to-digital converters such as the AD6600.

Frequency translation is accomplished with a 32-bit complex

Numerically Controlled Oscillator (NCO). Real data entering

this stage is separated into in-phase (I) and quadrature (Q)

components. This stage translates the input signal from a digital

intermediate frequency (IF) to baseband. Phase and amplitude

dither may be enabled on-chip to improve spurious performance

of the NCO. A phase offset word is available to create a known

phase relationship between multiple AD6620s.

Following frequency translation is a fixed coefficient, high speed

decimating filter that reduces the sample rate by a program-

mable ratio between 2 and 16. This is a second order, cascaded

integrator comb FIR filter shown as CIC2 in Figure 1. (Note:

Decimation of 1 in CIC2 requires 2

× or greater clock into

AD6620). The data rate into this stage equals the input data

rate, fSAMP. The data rate out of CIC2, fSAMP2, is determined by

the decimation factor, MCIC2.

相关PDF资料 |

PDF描述 |

|---|---|

| 6274291-2 | CONN JACK VERT PCB 75 OHM BNC |

| AD7669JNZ | IC I/O PORT 8BIT ANLG 28DIP |

| D38999/24FF11PA | CONN RCPT 11POS JAM NUT W/PINS |

| D38999/20JE26HN | CONN RCPT 26POS WALL MNT W/PINS |

| AD7569KNZ | IC I/O PORT 8BIT ANALOG 24DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD6620PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:65 MSPS Digital Receive Signal Processor |

| AD6620S | 制造商:AD 制造商全称:Analog Devices 功能描述:65 MSPS Digital Receive Signal Processor |

| AD6620S/PCB | 制造商:Analog Devices 功能描述:DUAL CHANNEL DECIMATING RECEIV 制造商:Analog Devices 功能描述:SGNL PROCESSOR 169CSPBGA - Bulk |

| AD6622 | 制造商:AD 制造商全称:Analog Devices 功能描述:Four-Channel, 75 MSPS Digital Transmit Signal Processor TSP |

| AD6622AS | 制造商:Analog Devices 功能描述:Transmit Signal Processor 128-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:4 CHANNEL 65 MSPS DIGITAL UPCONVERTER - Bulk |

发布紧急采购,3分钟左右您将得到回复。