- 您现在的位置:买卖IC网 > PDF目录11767 > AD6620ASZ-REEL (Analog Devices Inc)IC DGTL RCVR DUAL 67MSPS 80-PQFP PDF资料下载

参数资料

| 型号: | AD6620ASZ-REEL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 16/44页 |

| 文件大小: | 0K |

| 描述: | IC DGTL RCVR DUAL 67MSPS 80-PQFP |

| 标准包装: | 500 |

| 接口: | 并行/串行 |

| 电源电压: | 3 V ~ 3.6 V |

| 封装/外壳: | 80-BQFP |

| 供应商设备封装: | 80-PQFP(14x14) |

| 包装: | 带卷 (TR) |

| 安装类型: | 表面贴装 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

AD6620

–23–

REV. A

The frequency response of the filter is given by the following

equations. The gain and pass band droop of CIC5 should be

calculated by these equations. Both parameters may be compen-

sated for in the RCF stage.

Hz

z

S

M

CIC

()

–

=×

+

1

2

1

5

51

5

Hf

Mf

f

S

CIC

SAMP

CIC

()

sin

=×

×

+

1

2

5 5

5

2

5

π

The scale factor, SCIC5 is a programmable unsigned integer

between 0 and 20. It serves to control the attenuation of the

data into the CIC5 stage in 6 dB increments. For the best dynamic

range, SCIC5 should be set to the smallest value possible (lowest

attenuation) without creating an overflow condition. This can

be safely accomplished using the equation below, where OLCIC2

is the largest fraction of full scale possible at the input to this

filter stage. This value is output from the CIC2 stage then pipe-

lined into the CIC5. SCIC5 is ignored when this filter is bypassed

by setting MCIC5 = 1.

S

ceil

M

OL

M

OL

CIC

S

CIC

52

5

2

5

2

5

2

5

=×

()

= () ×

+

log (

) –

when CIC5 is bypassed;

OL

CIC

52

=

The output rate of this stage is given by the equation below.

f

M

SAMP

CIC

5

2

5

≤

–0.5

–120

–100

–80

–60

–40

–20

0

dBFS

f/fSAMP

–0.4 –0.3

–0.2

–0.1

0.1

0.2

0.3

0.4

0.5

0

–0.5

–120

–100

–80

–60

–40

–20

0

dBFS

f/fSAMP2

–0.4 –0.3

–0.2

–0.1

0.1

0.2

0.3

0.4

0.5

0

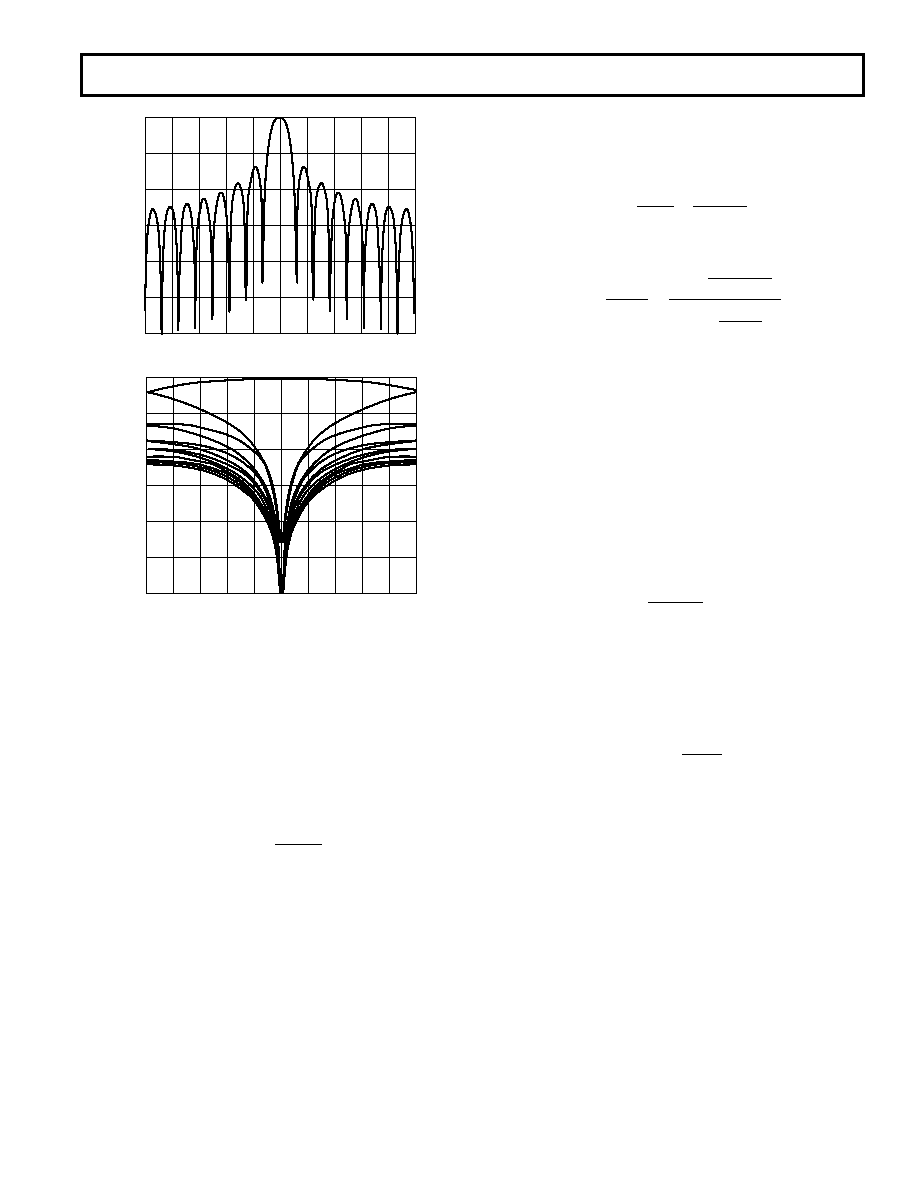

Figure 37. CIC2 Alias Rejection, MCIC2 = 16

5TH ORDER CASCADED INTEGRATOR COMB FILTER

The third signal processing stage, CIC5, implements a sharper

fixed-coefficient, decimating filter than CIC2. The input rate to

this filter is fSAMP2. The maximum input rate is given by the

equation below. NCH equals two for Diversity Channel Real

input mode; otherwise NCH equals one. In order to satisfy this

equation, MCIC2 can be increased, NCH can be reduced, or fCLK

can be increased (reference fractional rate input timing described

in the Input Timing section).

f

N

SAMP

CLK

CH

2

≤

×

The decimation ratio, MCIC5, may be programmed from 1 to 32

(all integer values). When MCIC5 = 1, this stage is bypassed and

the CIC5 scale factor is ignored.

相关PDF资料 |

PDF描述 |

|---|---|

| 6274291-2 | CONN JACK VERT PCB 75 OHM BNC |

| AD7669JNZ | IC I/O PORT 8BIT ANLG 28DIP |

| D38999/24FF11PA | CONN RCPT 11POS JAM NUT W/PINS |

| D38999/20JE26HN | CONN RCPT 26POS WALL MNT W/PINS |

| AD7569KNZ | IC I/O PORT 8BIT ANALOG 24DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD6620PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:65 MSPS Digital Receive Signal Processor |

| AD6620S | 制造商:AD 制造商全称:Analog Devices 功能描述:65 MSPS Digital Receive Signal Processor |

| AD6620S/PCB | 制造商:Analog Devices 功能描述:DUAL CHANNEL DECIMATING RECEIV 制造商:Analog Devices 功能描述:SGNL PROCESSOR 169CSPBGA - Bulk |

| AD6622 | 制造商:AD 制造商全称:Analog Devices 功能描述:Four-Channel, 75 MSPS Digital Transmit Signal Processor TSP |

| AD6622AS | 制造商:Analog Devices 功能描述:Transmit Signal Processor 128-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:4 CHANNEL 65 MSPS DIGITAL UPCONVERTER - Bulk |

发布紧急采购,3分钟左右您将得到回复。