- 您现在的位置:买卖IC网 > PDF目录11767 > AD6620ASZ-REEL (Analog Devices Inc)IC DGTL RCVR DUAL 67MSPS 80-PQFP PDF资料下载

参数资料

| 型号: | AD6620ASZ-REEL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 29/44页 |

| 文件大小: | 0K |

| 描述: | IC DGTL RCVR DUAL 67MSPS 80-PQFP |

| 标准包装: | 500 |

| 接口: | 并行/串行 |

| 电源电压: | 3 V ~ 3.6 V |

| 封装/外壳: | 80-BQFP |

| 供应商设备封装: | 80-PQFP(14x14) |

| 包装: | 带卷 (TR) |

| 安装类型: | 表面贴装 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页当前第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

AD6620

–35–

REV. A

The data is contained in the low byte of the 16 significant bits.

This data will be placed into the external interface register

pointed to by A[2 . . 0] for a write and will be ignored for a read.

Serial Port Writes

If the WRITE bit is high and the READ bit is low then a write

access is performed to the external interface register pointed to

by A[2 . . 0]. A write to an internal register takes place by first

writing the AMR and LAR. The data registers DR4–DR1 are

then written as needed. A final write to DR0 then moves the

data to the internal register.

Serial Port Reads

If the READ bit is high, then a read to the register indicated is

performed and the data will appear in the RDATA word appended

to the serial frame. The internal data read is loaded into the

serial data word in FIFO fashion. The first byte read is loaded

into the first eight bits, the second read during the frame is

loaded into the second byte, etc. Since the serial data is shifted

MSB first, the first byte will actually be loaded into the most

significant byte of the serial data word.

During a frame (the period between SDFS rising edges) up to

four reads may occur. When a read is requested through the

serial port, a data word is appended to the end of the serial string.

Even if AD is not asserted (see below for AD description) a word is

added to the end of the IQ data stream. Therefore, if the chip is

in single channel mode, the I and Q data are sent followed by a

read word. If the chip is in diversity channel mode, the IQ pairs

are followed by a read word. Thus the serial port responds with

either three or five serial words in a frame, respectively. If AD is

asserted, the read word is sent each frame regardless of a request. If

no requests are made, the appended word is all zeros.

The number of reads accomplished in a frame is limited by the

serial word length. If the serial word length is 16 bits, only two

reads can be performed during a frame. If the serial word length

is 24 bits, three reads can occur in a frame. If the serial word

length is 32 bits, then up to four reads can occur in a frame.

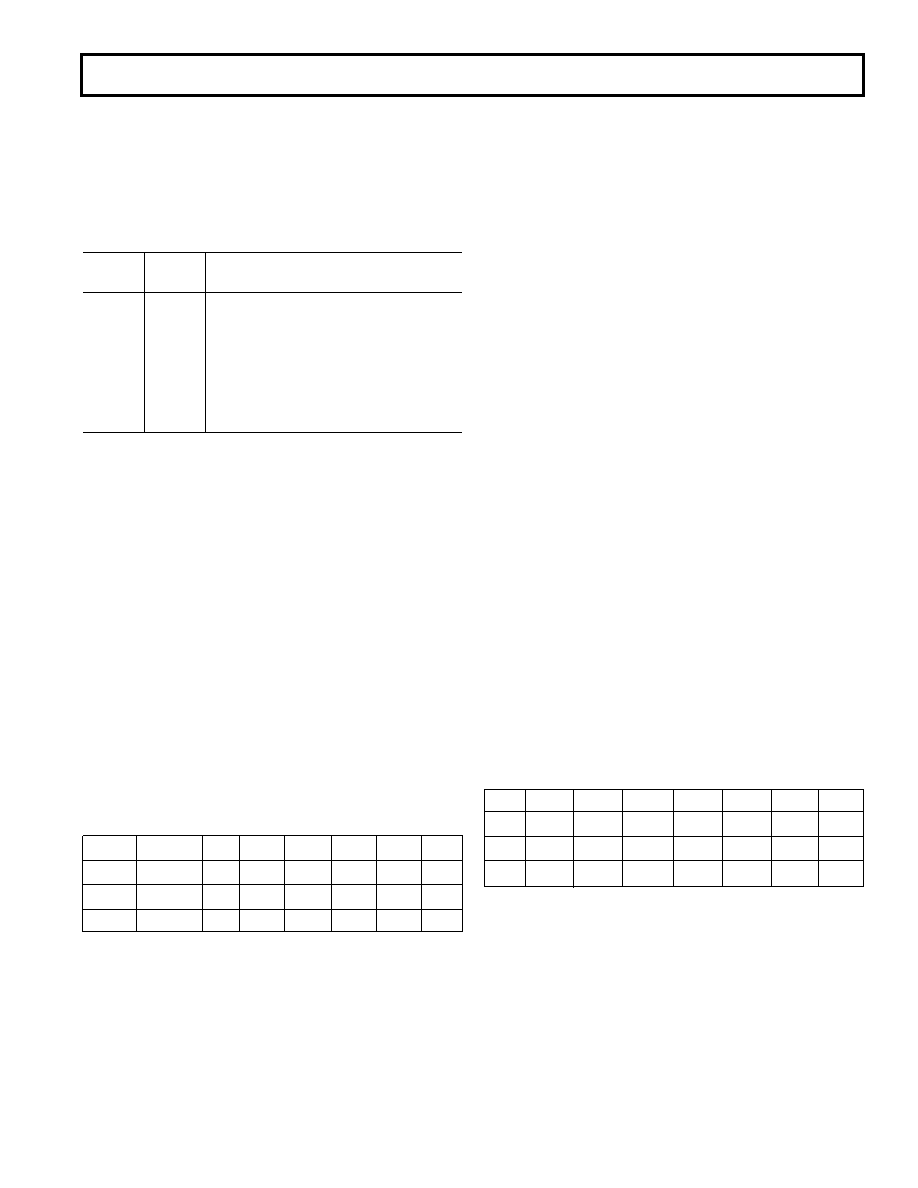

The RDATA word format is shown below. Rows three and four

will not be present when 16-bit words are used, and row four

will not be present when 24-bit words are used.

Table XV. RDATA Word Definition

DA7

DA6

DA5

DA4

DA3

DA2

DA1

DA0

DB7

DB6

DB5

DB4

DB3

DB2

DB1

DB0

DC7

DC6

DC5

DC4

DC3

DC2

DC1

DC0

DD7

DD6

DD5

DD4

DD3

DD1

DD0

The number of words in the serial frame depends on the operat-

ing mode of the chip (one or two I/Q pairs) and whether or not

a read access occurs. It also depends on the Append Data pin,

AD. When this signal is asserted, then the RDATA word is

appended to the Serial Frame regardless of whether or not a

read was performed in the frame. This allows time-slotted sys-

tems where multiple AD6620s or other devices share a serial

port of a DSP without hardware handshakes. When AD is

high and there has not been a read during the active frame,

the RDATA word is driven low and SDFE is held off for another

serial word length.

At all times, the serial interface must have time to shift all bits.

The section below Serial Port Guidelines should be consulted to

determine if sufficient time exists.

SERIAL PORT CONTROL

In addition to providing access to the complex output data stream

of the AD6620, the Serial Port can also be used for Dynamic

Control of the device. The dynamic registers of the AD6620

that are typically programmed while the chip is processing are

listed in the table below. In order to use the serial port control,

the chip must first be booted using the microprocessor interface.

Table XIII. Dynamic Registers

Bit

Address

Width

Name

300

8

MODE CONTROL REGISTER

302

32

NCO SYNC CONTROL REGISTER

303

32

NCO_FREQ

304

16

NCO PHASE_OFFSET

305

8

INPUT/CIC2 SCALE REGISTER

307

5

CIC5 SCALE REGISTER

309

4

OUTPUT/RCF CONTROL REGISTER

30B

8

RCF ADDRESS OFFSET REGISTER

The internal address and data structure are shared between

the microprocessor port and the serial port. When accessing

the internal RAM or registers, the serial port is given priority

over a microprocessor request. If a Mode 0 access occurs on

the microport while the serial port is accessing the internal address

space, the RDY line will go low and stay low until the serial

access has been completed. If a Mode 1 access occurs on the

microport during a serial access, the

DTACK signal will not go

low until the serial access has been completed. The microport is

used for booting the AD6620 and either the microport or the

serial port can be used to dynamically change the system param-

eters. Both ports may be used in the same design provided that

the handshaking rules described above are observed.

For each word shifted out of the serial port there is a word

shifted in. Each input word can provide one internal access. Each

access can be a read or a write. All reads and writes are per-

formed via the same 8-bit registers used by the microprocessor

port. Each bit in the SDI words has a predefined meaning and

are used to decode which of these registers are being accessed

and whether the access is a read or a write. The bits are defined

according to the table below.

Table XIV. SDI Input Word Definition

READ

WRITE

xxxA2

A1

A0

D7

D6

D5

D4

D3

D2

D1

D0

x

xxxxxx

x

xxxxxx

Only the first 16 bits of the SDI word contain significant data

regardless of the serial word length. The first two bits shifted in

are the READ and WRITE indicator signals. These bits control

the access type as described below and should not be asserted

simultaneously. If the Serial Port is not used for control then the

SDI pin should be tied low to disable register reads and writes.

The three address bits are the three least significant bits of the

upper byte in the 16-bit word. These three bits A[2:0] define

which of the seven external registers are accessed by the serial

port according to Table XI.

相关PDF资料 |

PDF描述 |

|---|---|

| 6274291-2 | CONN JACK VERT PCB 75 OHM BNC |

| AD7669JNZ | IC I/O PORT 8BIT ANLG 28DIP |

| D38999/24FF11PA | CONN RCPT 11POS JAM NUT W/PINS |

| D38999/20JE26HN | CONN RCPT 26POS WALL MNT W/PINS |

| AD7569KNZ | IC I/O PORT 8BIT ANALOG 24DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD6620PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:65 MSPS Digital Receive Signal Processor |

| AD6620S | 制造商:AD 制造商全称:Analog Devices 功能描述:65 MSPS Digital Receive Signal Processor |

| AD6620S/PCB | 制造商:Analog Devices 功能描述:DUAL CHANNEL DECIMATING RECEIV 制造商:Analog Devices 功能描述:SGNL PROCESSOR 169CSPBGA - Bulk |

| AD6622 | 制造商:AD 制造商全称:Analog Devices 功能描述:Four-Channel, 75 MSPS Digital Transmit Signal Processor TSP |

| AD6622AS | 制造商:Analog Devices 功能描述:Transmit Signal Processor 128-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:4 CHANNEL 65 MSPS DIGITAL UPCONVERTER - Bulk |

发布紧急采购,3分钟左右您将得到回复。