- 您现在的位置:买卖IC网 > PDF目录1986 > AD9510BCPZ-REEL7 (Analog Devices Inc)IC CLOCK DIST 8OUT PLL 64LFCSP PDF资料下载

参数资料

| 型号: | AD9510BCPZ-REEL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 10/56页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK DIST 8OUT PLL 64LFCSP |

| 标准包装: | 750 |

| 类型: | 扇出缓冲器(分配),除法器 |

| PLL: | 是 |

| 输入: | 时钟 |

| 输出: | CMOS,LVDS,LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:8 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 1.2GHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 带卷 (TR) |

| 配用: | AD9510-VCO/PCBZ-ND - BOARD EVALUATION FOR AD9510 AD9510/PCBZ-ND - BOARD EVALUATION FOR AD9510 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页当前第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页

AD9510

Data Sheet

Rev. B | Page 18 of 56

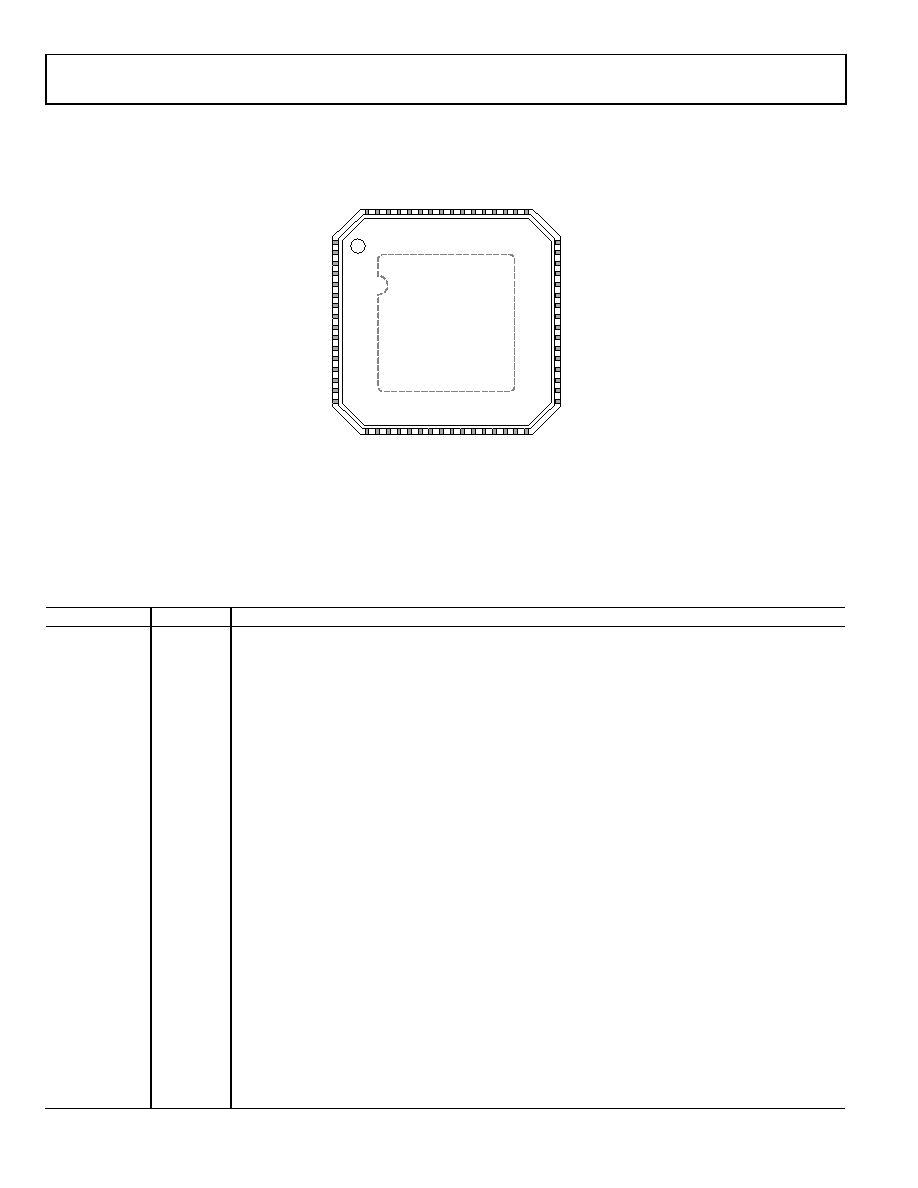

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 6.

Table 14. Pin Function Descriptions

Pin No.

Mnemonic

Description

1

REFIN

PLL Reference Input.

2

REFINB

Complementary PLL Reference Input.

3, 7, 8, 12, 22,

27, 32, 49, 50,

55, 62

GND

Ground.

4, 9, 13, 23, 26,

30, 31, 33, 36,

37, 40, 41, 44,

45, 48, 51, 52,

56, 59, 60, 64

VS

Power Supply (3.3 V) VS.

5

VCP

Charge Pump Power Supply VCPS. It must be greater than or equal to VS. VCPS can be set as high as 5.5 V for

VCOs requiring extended tuning range.

6

CP

Charge Pump Output.

10

CLK2

Clock Input Used to Connect External VCO/VCXO to Feedback Divider, N. CLK2 also drives the distribution

section of the chip and can be used as a generic clock input when PLL is not used.

11

CLK2B

Complementary Clock Input Used in Conjunction with CLK2.

14

CLK1

Clock Input that Drives Distribution Section of the Chip.

15

CLK1B

Complementary Clock Input Used in Conjunction with CLK1.

16

FUNCTION

Multipurpose Input Can Be Programmed as a Reset (RESETB), Sync (SYNCB), or Power-Down (PDB) Pin. This

pin is internally pulled down by a 30 kΩ resistor. If this pin is left NC, the part is in reset by default. To avoid

this, connect this pin to VS with a 1 kΩ resistor.

17

STATUS

Output Used to Monitor PLL Status and Sync Status.

18

SCLK

Serial Data Clock.

19

SDIO

Serial Data I/O.

20

SDO

Serial Data Output.

21

CSB

Serial Port Chip Select.

24

OUT7B

Complementary LVDS/Inverted CMOS Output.

25

OUT7

LVDS/CMOS Output.

05046-

003

NOTES

1. THE EXPOSED PADDLE ON THIS PACKAGE IS AN ELECTRICAL CONNECTION AS

WELL AS A THERMAL ENHANCEMENT. FOR THE DEVICE TO FUNCTION PROPERLY,

THE PADDLE MUST BE ATTACHED TO GROUND, GND.

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

S

T

AT

US

S

CL

K

S

DI

O

S

DO

CS

B

G

ND

VS

O

UT

7B

OU

T7

VS

G

ND

O

UT

3B

OU

T3

VS

G

ND

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

VS

C

PR

SET

G

ND

R

SET

VS

OU

T0

O

UT

0B

VS

G

ND

OU

T1

O

UT

1B

VS

G

ND

G

ND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

REFIN

REFINB

GND

VS

VCP

CP

GND

VS

CLK2

CLK2B

GND

VS

CLK1

CLK1B

FUNCTION

VS

OUT4

OUT4B

VS

OUT5

OUT5B

VS

OUT6

OUT6B

VS

OUT2

OUT2B

VS

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

AD9510

TOP VIEW

(Not to Scale)

相关PDF资料 |

PDF描述 |

|---|---|

| AD9511BCPZ-REEL7 | IC CLOCK DIST 5OUT PLL 48LFCSP |

| AD9512UCPZ-EP-R7 | IC CLOCK DIST 5OUT PLL 48LFCSP |

| AD9512UCPZ-EP | IC CLOCK DIST 5OUT PLL 48LFCSP |

| AD9513BCPZ-REEL7 | IC CLOCK DIST 3OUT PLL 32LFCSP |

| AD9514BCPZ-REEL7 | IC CLOCK DIST 3OUT PLL 32LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9510-VCO/PCB | 制造商:Analog Devices 功能描述:EVAL BD FOR 1.2 GHZ CLOCK DISTRIBUTION IC, PLL CORE, DIVIDER - Bulk 制造商:Analog Devices 功能描述:IC ((NS)) |

| AD9510-VCO/PCBZ | 功能描述:BOARD EVALUATION FOR AD9510 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PSoC® 主要目的:电源管理,热管理 嵌入式:- 已用 IC / 零件:- 主要属性:- 次要属性:- 已供物品:板,CD,电源 |

| AD9511 | 制造商:AD 制造商全称:Analog Devices 功能描述:1.2 GHz Clock Distribution IC, PLL Core, Dividers, Delay Adjust, Five Outputs |

| AD9511/PCB | 制造商:Analog Devices 功能描述:1.2 GHZ CLOCK DISTRIBUTION IC, PLL CORE,DIVIDERS, DELAY ADJUST, FIVE OUTPUTS 制造商:Analog Devices 功能描述:EVAL BD FOR AD9511 1.2 GHZ CLOCK DISTRIBUTION IC, PLL CORE,D - Bulk |

| AD9511BCPZ | 功能描述:IC CLOCK DIST 5OUT PLL 48LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:Precision Edge® 类型:时钟/频率合成器 PLL:无 输入:CML,PECL 输出:CML 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/是 频率 - 最大:10.7GHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-VFQFN 裸露焊盘,16-MLF? 供应商设备封装:16-MLF?(3x3) 包装:带卷 (TR) 其它名称:SY58052UMGTRSY58052UMGTR-ND |

发布紧急采购,3分钟左右您将得到回复。