- 您现在的位置:买卖IC网 > PDF目录1986 > AD9510BCPZ-REEL7 (Analog Devices Inc)IC CLOCK DIST 8OUT PLL 64LFCSP PDF资料下载

参数资料

| 型号: | AD9510BCPZ-REEL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 24/56页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK DIST 8OUT PLL 64LFCSP |

| 标准包装: | 750 |

| 类型: | 扇出缓冲器(分配),除法器 |

| PLL: | 是 |

| 输入: | 时钟 |

| 输出: | CMOS,LVDS,LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:8 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 1.2GHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 带卷 (TR) |

| 配用: | AD9510-VCO/PCBZ-ND - BOARD EVALUATION FOR AD9510 AD9510/PCBZ-ND - BOARD EVALUATION FOR AD9510 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页

AD9510

Data Sheet

Rev. B | Page 30 of 56

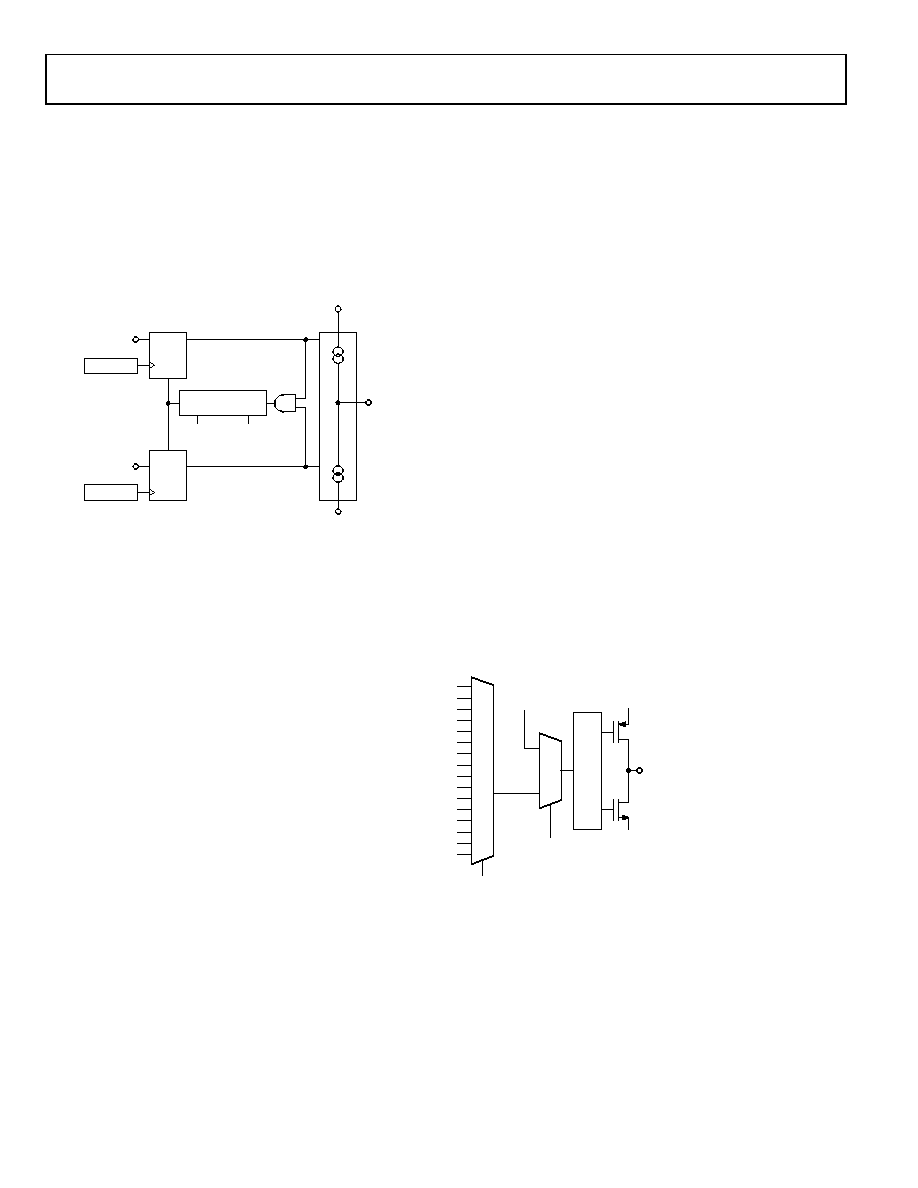

Phase Frequency Detector (PFD) and Charge Pump

The PFD takes inputs from the R counter and the N counter

(N = BP + A) and produces an output proportional to the

phase and frequency difference between them. Figure 36 is a

simplified schematic. The PFD includes a programmable delay

element that controls the width of the antibacklash pulse. This

pulse ensures that there is no dead zone in the PFD transfer

function and minimizes phase noise and reference spurs. Two

bits in Register 0x0D[1:0] control the width of the pulse.

Figure 36. PFD Simplified Schematic and Timing (In Lock)

Antibacklash Pulse

The PLL features a programmable antibacklash pulse width that

is set by the value in Register 0x0D[1:0]. The default antiback-

lash pulse width is 1.3 ns (Register 0x0D[1:0] = 00b) and

normally does not need to be changed. The antibacklash pulse

eliminates the dead zone around the phase-locked condition

and thereby reduces the potential for certain spurs that can be

impressed on the VCO signal.

STATUS Pin

The output multiplexer on the AD9510 allows access to various sig-

nals and internal points on the chip at the STATUS pin. Figure 37

shows a block diagram of the STATUS pin section. The function

of the STATUS pin is controlled by Register 0x0[5:2].

PLL Digital Lock Detect

The STATUS pin can display two types of PLL lock detect:

digital (DLD) and analog (ALD). Whenever digital lock detect

is desired, the STATUS pin provides a CMOS level signal, which

can be active high or active low.

The digital lock detect has one of two time windows, as selected

by Register 0x0D[5]. The default (Register 0x0D[5] = 0b) requires

the signal edges on the inputs to the PFD to be coincident within

9.5 ns to set the DLD true, which then must separate by at least

15 ns to give DLD = false.

The other setting (Register 0x0D[5] = 1) makes these coinci-

dence times 3.5 ns for DLD = true and 7 ns for DLD = false.

The DLD can be disabled by writing 1 to Register 0x0D[6].

If the signal at REFIN goes away while DLD is true, the DLD

does not necessarily indicate loss of lock. See the Loss of

Reference section for more information.

Figure 37. STATUS Pin Circuit CLK1 Clock Input

05046-014

D1

Q1

U1

CLR1

R DIVIDER

HI

UP

D2

Q2

U2

CLR2

N DIVIDER

HI

DOWN

CP

CHARGE

PUMP

VP

GND

U3

PROGRAMMABLE

DELAY

ANTIBACKLASH

PULSE WIDTH

05046-

015

OFF (LOW) (DEFAULT)

DIGITAL LOCK DETECT (ACTIVE HIGH)

N DIVIDER OUTPUT

DIGITAL LOCK DETECT (ACTIVE LOW)

R DIVIDER OUTPUT

ANALOG LOCK DETECT (N-CHANNEL OPEN DRAIN)

A COUNTER OUTPUT

PRESCALER OUTPUT (NCLK)

PFD UP PULSE

PFD DOWN PULSE

LOSS OF REFERENCE (ACTIVE HIGH)

TRISTATE

ANALOG LOCK DETECT (P-CHANNEL OPEN DRAIN)

LOSS OF REFERENCE OR LOCK DETECT (ACTIVE HIGH)

LOSS OF REFERENCE OR LOCK DETECT (ACTIVE LOW)

LOSS OF REFERENCE (ACTIVE LOW)

PLL MUX CONTROL

0x08[5:2]

SYNC DETECT ENABLE

0x58[0]

SYNC

DETECT

C

ON

TR

OL

FOR

A

N

A

LOG

L

O

CK

DE

T

E

CT

M

O

DE

VS

GND

STATUS

PIN

相关PDF资料 |

PDF描述 |

|---|---|

| AD9511BCPZ-REEL7 | IC CLOCK DIST 5OUT PLL 48LFCSP |

| AD9512UCPZ-EP-R7 | IC CLOCK DIST 5OUT PLL 48LFCSP |

| AD9512UCPZ-EP | IC CLOCK DIST 5OUT PLL 48LFCSP |

| AD9513BCPZ-REEL7 | IC CLOCK DIST 3OUT PLL 32LFCSP |

| AD9514BCPZ-REEL7 | IC CLOCK DIST 3OUT PLL 32LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9510-VCO/PCB | 制造商:Analog Devices 功能描述:EVAL BD FOR 1.2 GHZ CLOCK DISTRIBUTION IC, PLL CORE, DIVIDER - Bulk 制造商:Analog Devices 功能描述:IC ((NS)) |

| AD9510-VCO/PCBZ | 功能描述:BOARD EVALUATION FOR AD9510 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PSoC® 主要目的:电源管理,热管理 嵌入式:- 已用 IC / 零件:- 主要属性:- 次要属性:- 已供物品:板,CD,电源 |

| AD9511 | 制造商:AD 制造商全称:Analog Devices 功能描述:1.2 GHz Clock Distribution IC, PLL Core, Dividers, Delay Adjust, Five Outputs |

| AD9511/PCB | 制造商:Analog Devices 功能描述:1.2 GHZ CLOCK DISTRIBUTION IC, PLL CORE,DIVIDERS, DELAY ADJUST, FIVE OUTPUTS 制造商:Analog Devices 功能描述:EVAL BD FOR AD9511 1.2 GHZ CLOCK DISTRIBUTION IC, PLL CORE,D - Bulk |

| AD9511BCPZ | 功能描述:IC CLOCK DIST 5OUT PLL 48LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:Precision Edge® 类型:时钟/频率合成器 PLL:无 输入:CML,PECL 输出:CML 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/是 频率 - 最大:10.7GHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-VFQFN 裸露焊盘,16-MLF? 供应商设备封装:16-MLF?(3x3) 包装:带卷 (TR) 其它名称:SY58052UMGTRSY58052UMGTR-ND |

发布紧急采购,3分钟左右您将得到回复。