- 您现在的位置:买卖IC网 > PDF目录1986 > AD9510BCPZ-REEL7 (Analog Devices Inc)IC CLOCK DIST 8OUT PLL 64LFCSP PDF资料下载

参数资料

| 型号: | AD9510BCPZ-REEL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 31/56页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK DIST 8OUT PLL 64LFCSP |

| 标准包装: | 750 |

| 类型: | 扇出缓冲器(分配),除法器 |

| PLL: | 是 |

| 输入: | 时钟 |

| 输出: | CMOS,LVDS,LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:8 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 1.2GHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 带卷 (TR) |

| 配用: | AD9510-VCO/PCBZ-ND - BOARD EVALUATION FOR AD9510 AD9510/PCBZ-ND - BOARD EVALUATION FOR AD9510 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页当前第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页

Data Sheet

AD9510

Rev. B | Page 37 of 56

Phase offsets can be related to degrees by calculating the phase

step for a particular divide ratio:

Phase Step = 360°/(Divide Ratio) = 360°/DIV

Using some of the same examples,

DIV = 4

Phase Step = 360°/4 = 90°

Unique Phase Offsets in Degrees Are Phase = 0°, 90°,

180°, 270°

DIV = 7

Phase Step = 360°/7 = 51.43°

Unique Phase Offsets in Degrees Are Phase = 0°, 51.43°,

102.86°, 154.29°, 205.71°, 257.15°, 308.57°

DELAY BLOCK

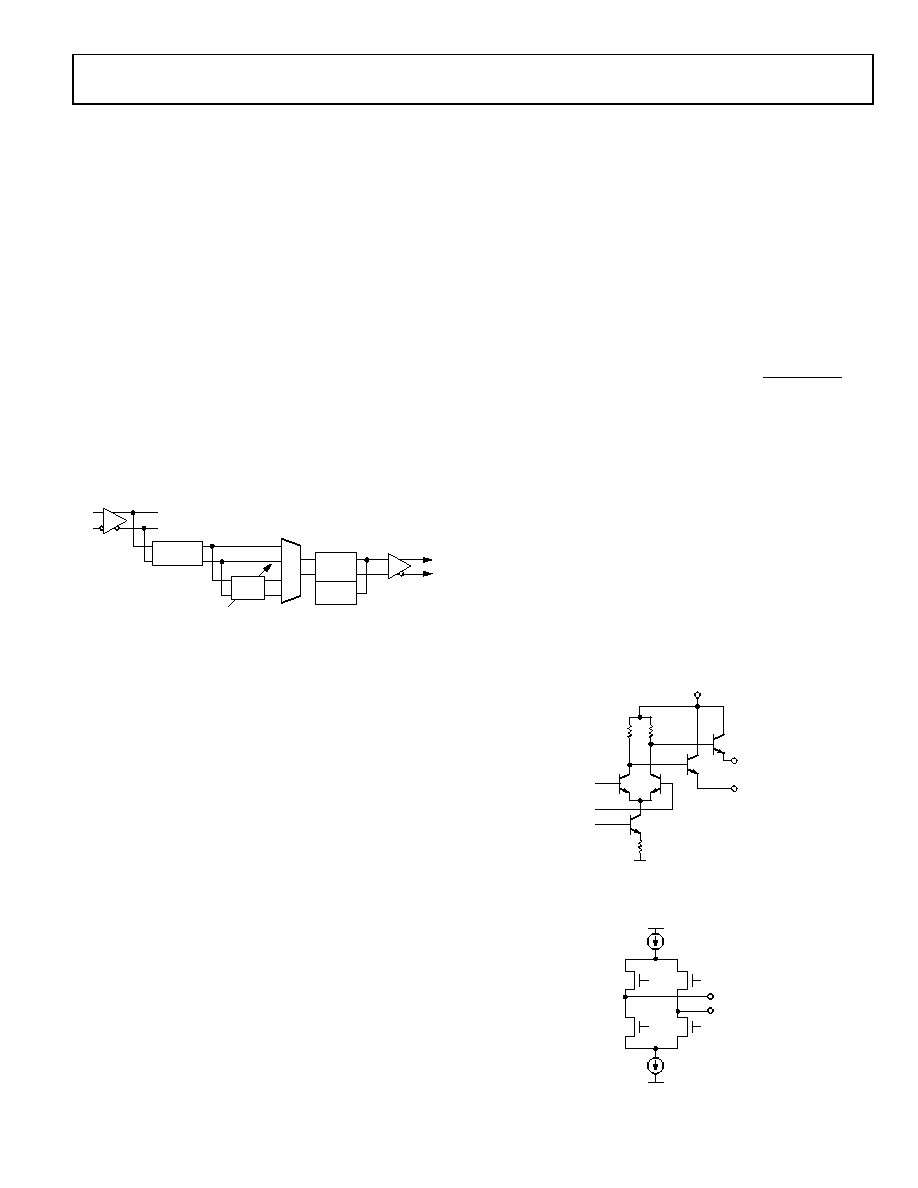

OUT5 and OUT6 (LVDS/CMOS) include an analog delay element

that can be programmed (from Register 0x34 to Register 0x3A)

to give variable time delays (Δt) in the clock signal passing

through that output.

Figure 40. Analog Delay (OUT5 and OUT6)

The amount of delay that can be used is determined by the

frequency of the clock being delayed. The amount of delay can

approach one-half cycle of the clock period. For example, for a

10 MHz clock, the delay can extend to the full 8 ns maximum of

which the delay element is capable. However, for a 100 MHz

clock (with 50% duty cycle), the maximum delay is less than

5 ns (or half of the period).

OUT5 and OUT6 allow a full-scale delay in the range 1 ns to

8 ns. The full-scale delay is selected by choosing a combination

of ramp current and the number of capacitors by writing the

appropriate values into Register 0x35 and Register 0x39. There

are 25 fine delay settings (Register 0x36 and Register 0x3A =

00000b to 11000b) for each full scale, set by Register 0x36 and

Register 0x3A.

This path adds some jitter greater than that specified for the

nondelay outputs. Therefore, use the delay function primarily

for clocking digital chips, such as FPGA, ASIC, DUC, and

DDC, rather than for data converters. The jitter is higher for

long full scales (~8 ns). This is because the delay block uses a

ramp and trip points to create the variable delay. A longer ramp

means more noise can be introduced.

Calculating the Delay

The following values and equations are used to calculate the

delay of the delay block.

Value of Ramp Current Control Bits (Register 0x35 or

Register 0x39 [2:0]) = IRAMP_BITS

IRAMP (A) = 200 × (IRAMP_BITS + 1)

No. of Caps = No. of 0s + 1 in Ramp Control Capacitor

(Register 0x35 or Register 0x39 [5:3]), that is, 101 = 1 + 1 =

2; 110 = 2; 100 = 2 + 1 = 3; 001 = 2 + 1 = 3; 111 = 0 + 1 = 1)

DELAY_RANGE (ns) = 200 × ((No. of Caps + 3)/(IRAMP)) ×

1.3286

( )

(

)

6

1

10

1600

0.34

ns

4

×

+

×

+

=

RAMP

I

Caps

of

No.

I

Offset

DELAY_FULL_SCALE (ns) = DELAY_RANGE × (24/31) +

Offset

FINE_ADJ = Value of Delay Fine Adjust (Register 0x36 or

Register 0x3A[5:1]), that is, 11000 = 24

Delay (ns) = Offset + DELAY_RANGE × FINE_ADJ × (1/31)

OUTPUTS

The AD9510 offers three different output level choices:

LVPECL, LVDS, and CMOS. OUT0 to OUT3 are LVPECL only.

OUT4 to OUT7 can be selected as either LVDS or CMOS. Each

output can be enabled or turned off as needed to save power.

The simplified equivalent circuit of the LVPECL outputs is

shown in Figure 41.

Figure 41. LVPECL Output Simplified Equivalent Circuit

Figure 42. LVDS Output Simplified Equivalent Circuit

05046-

036

ΔT

FINE DELAY ADJUST

(25 STEPS)

FULL-SCALE: 1ns TO 8ns

OUT5

OUT6 ONLY

CLOCK INPUT

÷N

SELECT

M

UX

LVDS

CMOS

OUTPUT

DRIVER

05046-037

3.3V

OUT

OUTB

GND

05046-038

3.5mA

OUT

OUTB

相关PDF资料 |

PDF描述 |

|---|---|

| AD9511BCPZ-REEL7 | IC CLOCK DIST 5OUT PLL 48LFCSP |

| AD9512UCPZ-EP-R7 | IC CLOCK DIST 5OUT PLL 48LFCSP |

| AD9512UCPZ-EP | IC CLOCK DIST 5OUT PLL 48LFCSP |

| AD9513BCPZ-REEL7 | IC CLOCK DIST 3OUT PLL 32LFCSP |

| AD9514BCPZ-REEL7 | IC CLOCK DIST 3OUT PLL 32LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9510-VCO/PCB | 制造商:Analog Devices 功能描述:EVAL BD FOR 1.2 GHZ CLOCK DISTRIBUTION IC, PLL CORE, DIVIDER - Bulk 制造商:Analog Devices 功能描述:IC ((NS)) |

| AD9510-VCO/PCBZ | 功能描述:BOARD EVALUATION FOR AD9510 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PSoC® 主要目的:电源管理,热管理 嵌入式:- 已用 IC / 零件:- 主要属性:- 次要属性:- 已供物品:板,CD,电源 |

| AD9511 | 制造商:AD 制造商全称:Analog Devices 功能描述:1.2 GHz Clock Distribution IC, PLL Core, Dividers, Delay Adjust, Five Outputs |

| AD9511/PCB | 制造商:Analog Devices 功能描述:1.2 GHZ CLOCK DISTRIBUTION IC, PLL CORE,DIVIDERS, DELAY ADJUST, FIVE OUTPUTS 制造商:Analog Devices 功能描述:EVAL BD FOR AD9511 1.2 GHZ CLOCK DISTRIBUTION IC, PLL CORE,D - Bulk |

| AD9511BCPZ | 功能描述:IC CLOCK DIST 5OUT PLL 48LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:Precision Edge® 类型:时钟/频率合成器 PLL:无 输入:CML,PECL 输出:CML 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/是 频率 - 最大:10.7GHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-VFQFN 裸露焊盘,16-MLF? 供应商设备封装:16-MLF?(3x3) 包装:带卷 (TR) 其它名称:SY58052UMGTRSY58052UMGTR-ND |

发布紧急采购,3分钟左右您将得到回复。