- 您现在的位置:买卖IC网 > PDF目录1986 > AD9510BCPZ-REEL7 (Analog Devices Inc)IC CLOCK DIST 8OUT PLL 64LFCSP PDF资料下载

参数资料

| 型号: | AD9510BCPZ-REEL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 34/56页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK DIST 8OUT PLL 64LFCSP |

| 标准包装: | 750 |

| 类型: | 扇出缓冲器(分配),除法器 |

| PLL: | 是 |

| 输入: | 时钟 |

| 输出: | CMOS,LVDS,LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:8 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 1.2GHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 带卷 (TR) |

| 配用: | AD9510-VCO/PCBZ-ND - BOARD EVALUATION FOR AD9510 AD9510/PCBZ-ND - BOARD EVALUATION FOR AD9510 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页当前第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页

AD9510

Data Sheet

Rev. B | Page 4 of 56

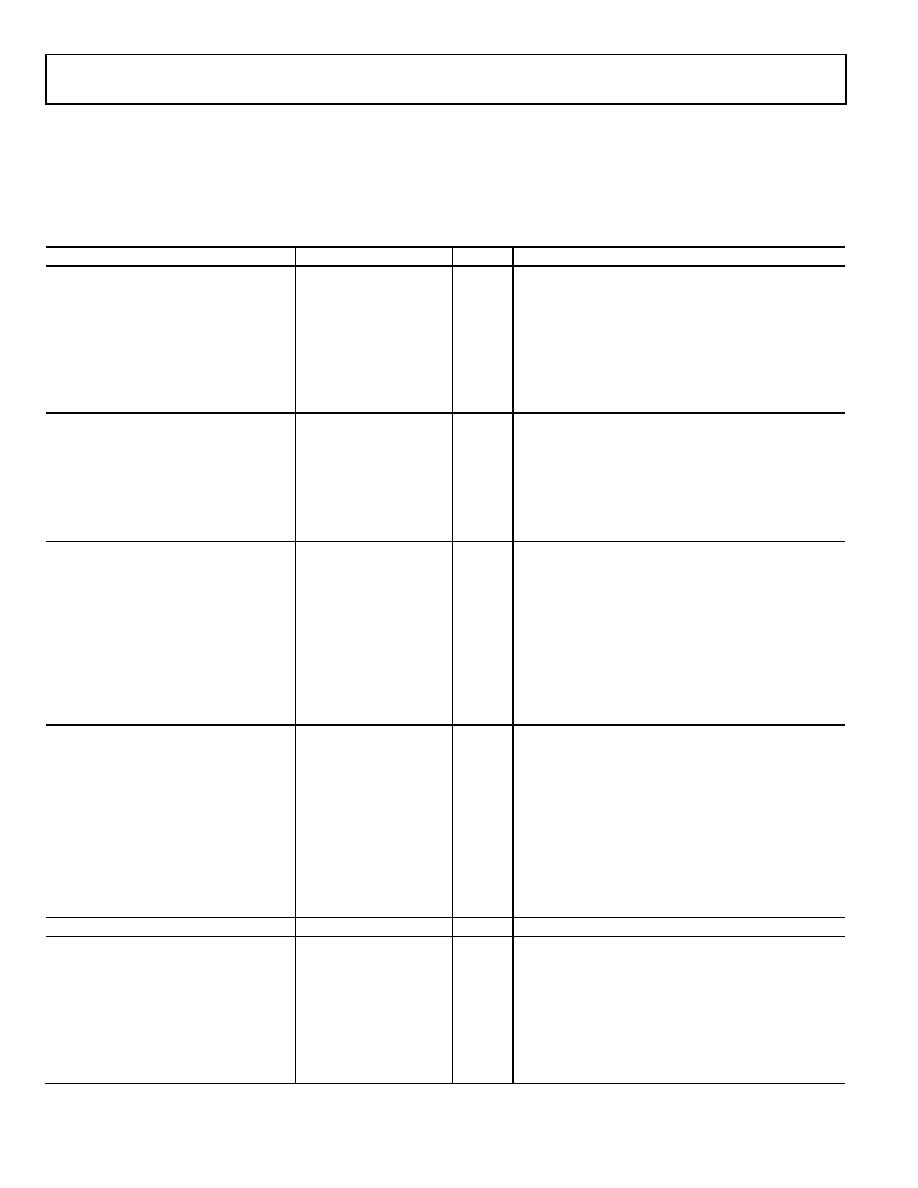

SPECIFICATIONS

Typical (typ) is given for VS = 3.3 V ± 5%, VS ≤ VCPS ≤ 5.5 V, TA = 25°C, RSET = 4.12 k, CPRSET = 5.1 k, unless otherwise noted.

Minimum (min) and maximum (max) values are given over full VS and TA (40°C to +85°C) variation.

PLL CHARACTERISTICS

Table 1.

Parameter

Min

Typ

Max

Unit

Test Conditions/Comments

REFERENCE INPUTS (REFIN)

Input Frequency

0

250

MHz

Input Sensitivity

150

mV p-p

Self-Bias Voltage, REFIN

1.45

1.60

1.75

V

Self-bias voltage of REFIN1

Self-Bias Voltage, REFINB

1.40

1.50

1.60

V

Self-bias voltage of REFINB1

Input Resistance, REFIN

4.0

4.9

5.8

kΩ

Self-biased1

Input Resistance, REFINB

4.5

5.4

6.3

kΩ

Self-biased1

Input Capacitance

2

pF

PHASE FREQUENCY DETECTOR (PFD)

PFD Input Frequency

100

MHz

Antibacklash pulse width, Register 0x0D[1:0] = 00b

PFD Input Frequency

100

MHz

Antibacklash pulse width, Register 0x0D[1:0] = 01b

PFD Input Frequency

45

MHz

Antibacklash pulse width, Register 0x0D[1:0] = 10b

Antibacklash Pulse Width

1.3

ns

Register 0x0D[1:0] = 00b (this is the default setting)

Antibacklash Pulse Width

2.9

ns

Register 0x0D[1:0] = 01b

Antibacklash Pulse Width

6.0

ns

Register 0x0D[1:0] = 10b

CHARGE PUMP (CP)

ICP Sink/Source

Programmable

High Value

4.8

mA

With CPRSET = 5.1 kΩ

Low Value

0.60

mA

Absolute Accuracy

2.5

%

VCP = VCPS/2

CPRSET Range

2.7/10

kΩ

ICP Three-State Leakage

1

nA

Sink-and-Source Current Matching

2

%

0.5 < VCP < VCPS 0.5 V

ICP vs. VCP

1.5

%

0.5 < VCP < VCPS 0.5 V

ICP vs. Temperature

2

%

VCP = VCPS/2 V

RF CHARACTERISTICS (CLK2)2

Input Frequency

1.6

GHz

Frequencies > 1200 MHz (LVPECL) or 800 MHz (LVDS)

require a minimum divide-by-2 (see the Distribution

Input Sensitivity

150

mV p-p

Input Common-Mode Voltage, VCM

1.5

1.6

1.7

V

Self-biased, enables ac coupling

Input Common-Mode Range, VCMR

1.3

1.8

V

With 200 mV p-p signal applied

Input Sensitivity, Single-Ended

150

mV p-p

CLK2 ac-coupled, CLK2B capacitively bypassed to RF

ground

Input Resistance

4.0

4.8

5.6

kΩ

Self-biased

Input Capacitance

2

pF

CLK2 VS. REFIN DELAY

500

ps

Difference at PFD

PRESCALER (PART OF N DIVIDER)

See the VCO/VCXO Feedback Divider—N (P, A, B) section

Prescaler Input Frequency

P = 2 DM (2/3)

600

MHz

P = 4 DM (4/5)

1000

MHz

P = 8 DM (8/9)

1600

MHz

P = 16 DM (16/17)

1600

MHz

P = 32 DM (32/33)

1600

MHz

CLK2 Input Frequency for PLL

300

MHz

A, B counter input frequency

相关PDF资料 |

PDF描述 |

|---|---|

| AD9511BCPZ-REEL7 | IC CLOCK DIST 5OUT PLL 48LFCSP |

| AD9512UCPZ-EP-R7 | IC CLOCK DIST 5OUT PLL 48LFCSP |

| AD9512UCPZ-EP | IC CLOCK DIST 5OUT PLL 48LFCSP |

| AD9513BCPZ-REEL7 | IC CLOCK DIST 3OUT PLL 32LFCSP |

| AD9514BCPZ-REEL7 | IC CLOCK DIST 3OUT PLL 32LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9510-VCO/PCB | 制造商:Analog Devices 功能描述:EVAL BD FOR 1.2 GHZ CLOCK DISTRIBUTION IC, PLL CORE, DIVIDER - Bulk 制造商:Analog Devices 功能描述:IC ((NS)) |

| AD9510-VCO/PCBZ | 功能描述:BOARD EVALUATION FOR AD9510 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PSoC® 主要目的:电源管理,热管理 嵌入式:- 已用 IC / 零件:- 主要属性:- 次要属性:- 已供物品:板,CD,电源 |

| AD9511 | 制造商:AD 制造商全称:Analog Devices 功能描述:1.2 GHz Clock Distribution IC, PLL Core, Dividers, Delay Adjust, Five Outputs |

| AD9511/PCB | 制造商:Analog Devices 功能描述:1.2 GHZ CLOCK DISTRIBUTION IC, PLL CORE,DIVIDERS, DELAY ADJUST, FIVE OUTPUTS 制造商:Analog Devices 功能描述:EVAL BD FOR AD9511 1.2 GHZ CLOCK DISTRIBUTION IC, PLL CORE,D - Bulk |

| AD9511BCPZ | 功能描述:IC CLOCK DIST 5OUT PLL 48LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:Precision Edge® 类型:时钟/频率合成器 PLL:无 输入:CML,PECL 输出:CML 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/是 频率 - 最大:10.7GHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-VFQFN 裸露焊盘,16-MLF? 供应商设备封装:16-MLF?(3x3) 包装:带卷 (TR) 其它名称:SY58052UMGTRSY58052UMGTR-ND |

发布紧急采购,3分钟左右您将得到回复。