- 您现在的位置:买卖IC网 > PDF目录1986 > AD9511BCPZ-REEL7 (Analog Devices Inc)IC CLOCK DIST 5OUT PLL 48LFCSP PDF资料下载

参数资料

| 型号: | AD9511BCPZ-REEL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 45/60页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK DIST 5OUT PLL 48LFCSP |

| 标准包装: | 750 |

| 类型: | 扇出缓冲器(分配),除法器 |

| PLL: | 是 |

| 输入: | 时钟 |

| 输出: | CMOS,LVDS,LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:5 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 1.2GHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 48-LFCSP-VQ(7x7) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页当前第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页

AD9511

Rev. A | Page 5 of 60

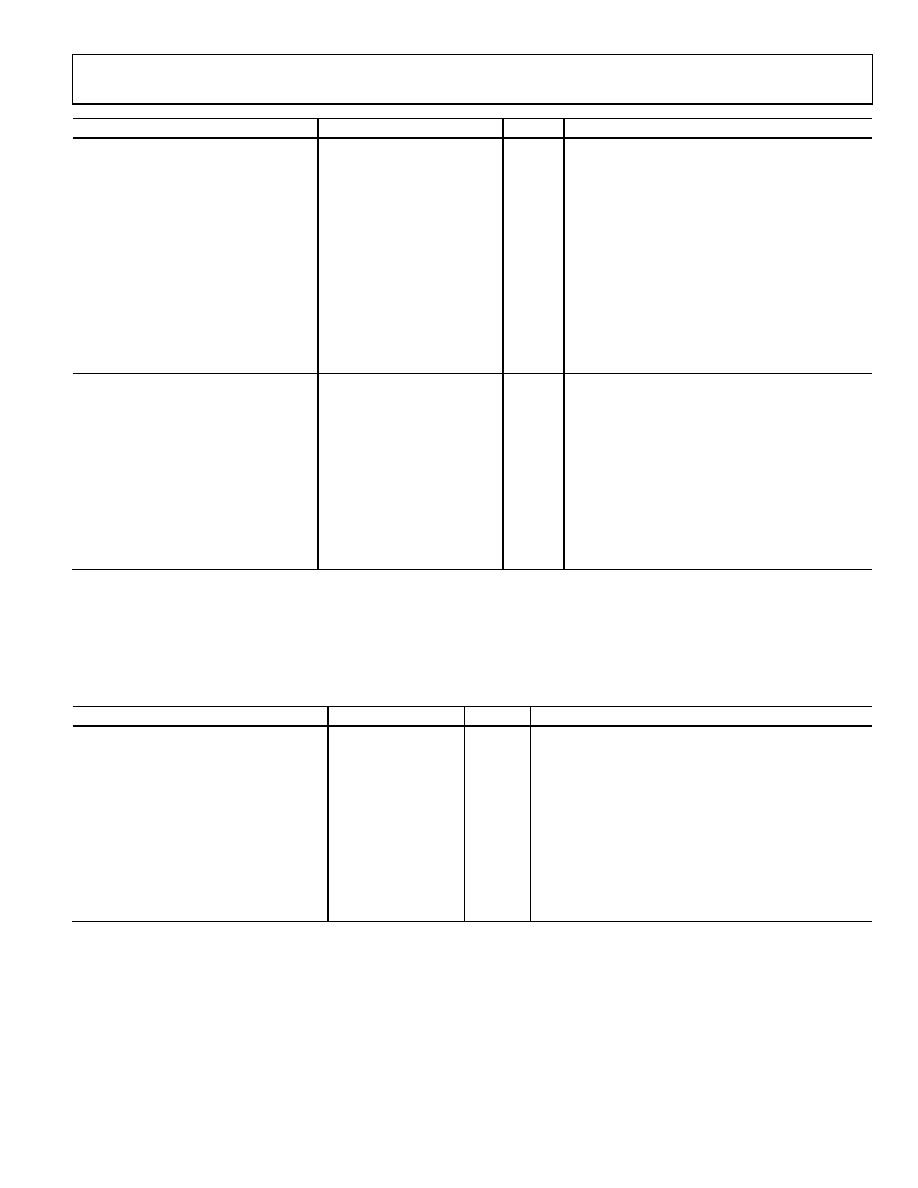

Parameter

Min

Typ

Max

Unit

Test Conditions/Comments

NOISE CHARACTERISTICS

In-Band Noise of the Charge Pump/

Phase Frequency Detector (In-Band

Means Within the LBW of the PLL)

The synthesizer phase noise floor is

estimated by measuring the in-band

phase noise at the output of the VCO and

subtracting 20logN (where N is the

N divider value).

@ 50 kHz PFD Frequency

172

dBc/Hz

@ 2 MHz PFD Frequency

156

dBc/Hz

@ 10 MHz PFD Frequency

149

dBc/Hz

@ 50 MHz PFD Frequency

142

dBc/Hz

PLL Figure of Merit

218 +

10 × log (fPFD)

dBc/Hz

Approximation of the PFD/CP phase noise

floor (in the flat region) inside the PLL loop

bandwidth. When running closed loop this

phase noise is gained up by 20 × log(N)3.

PLL DIGITAL LOCK DETECT WINDOW4

Signal available at STATUS pin

when selected by 08h<5:2>.

Required to Lock

(Coincidence of Edges)

Selected by Register ODh.

Low Range (ABP 1.3 ns, 2.9 ns Only)

3.5

ns

<5> = 1b.

High Range (ABP 1.3 ns, 2.9 ns)

7.5

ns

<5> = 0b.

High Range (ABP 6 ns)

3.5

ns

<5> = 0b.

To Unlock After Lock (Hysteresis)4

Selected by Register 0Dh.

Low Range (ABP 1.3 ns, 2.9 ns Only)

7

ns

<5> = 1b.

High Range (ABP 1.3 ns, 2.9 ns)

15

ns

<5> = 0b.

High Range (ABP 6 ns)

11

ns

<5> = 0b.

1 REFIN and REFINB self-bias points are offset slightly to avoid chatter on an open input condition.

2 CLK2 is electrically identical to CLK1; the distribution only input can be used as differential or single-ended input (see the Clock Inputs section).

3 Example: 218 + 10 × log(fPFD) + 20 × log(N) should give the values for the in-band noise at the VCO output.

4 For reliable operation of the digital lock detect, the period of the PFD frequency must be greater than the unlock-after-lock time.

CLOCK INPUTS

Table 2.

Parameter

Min

Typ

Max

Unit

Test Conditions/Comments

CLOCK INPUTS (CLK1, CLK2)1

Input Frequency

0

1.6

GHz

Input Sensitivity

1502

mV p-p

Jitter performance can be improved with higher slew

rates (greater swing).

Input Level

23

V p-p

Larger swings turn on the protection diodes and can

degrade jitter performance.

Input Common-Mode Voltage, VCM

1.5

1.6

1.7

V

Self-biased; enables ac coupling.

Input Common-Mode Range, VCMR

1.3

1.8

V

With 200 mV p-p signal applied; dc-coupled.

Input Sensitivity, Single-Ended

150

mV p-p

CLK2 ac-coupled; CLK2B ac bypassed to RF ground.

Input Resistance

4.0

4.8

5.6

kΩ

Self-biased.

Input Capacitance

2

pF

1 CLK1 and CLK2 are electrically identical; each can be used as either differential or single-ended input.

2 With a 50 Ω termination, this is 12.5 dBm.

3 With a 50 Ω termination, this is +10 dBm.

相关PDF资料 |

PDF描述 |

|---|---|

| AD9512UCPZ-EP-R7 | IC CLOCK DIST 5OUT PLL 48LFCSP |

| AD9512UCPZ-EP | IC CLOCK DIST 5OUT PLL 48LFCSP |

| AD9513BCPZ-REEL7 | IC CLOCK DIST 3OUT PLL 32LFCSP |

| AD9514BCPZ-REEL7 | IC CLOCK DIST 3OUT PLL 32LFCSP |

| AD9515BCPZ-REEL7 | IC CLOCK DIST 2OUT PLL 32LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9511-VCO/PCB | 制造商:Analog Devices 功能描述:EVAL BD FOR AD9511 1.2 GHZ CLOCK DISTRIBUTION IC, PLL CORE,D - Bulk |

| AD9512 | 制造商:AD 制造商全称:Analog Devices 功能描述:800 MHz Clock Distribution IC,1.5 GHz Inputs, Dividers, Delay Adjust, Five Outputs |

| AD9512/PCB | 制造商:Analog Devices 功能描述:Evaluation Kit For 1.2 GHZ Clock Distribution IC, 1.6 GHZ Inputs, Dividers, Delay Adjust, Five Outputs 制造商:Analog Devices 功能描述:EVAL KIT FOR 1.2 GHZ CLOCK DISTRIBUTION IC, 1.6 GHZ INPUTS, - Bulk |

| AD9512/PCBZ | 功能描述:BOARD EVAL FOR AD9512 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PSoC® 主要目的:电源管理,热管理 嵌入式:- 已用 IC / 零件:- 主要属性:- 次要属性:- 已供物品:板,CD,电源 |

| AD9512BCPZ | 功能描述:IC CLOCK DIST 5OUT PLL 48LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。