- 您现在的位置:买卖IC网 > PDF目录1194 > ADP1043AFB100EVALZ (Analog Devices Inc)BOARD EVALUATION ADP1043A 100W PDF资料下载

参数资料

| 型号: | ADP1043AFB100EVALZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 68/72页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION ADP1043A 100W |

| 标准包装: | 1 |

| 主要目的: | 电源管理,电源监控器/跟踪器/序列发生器 |

| 已用 IC / 零件: | ADP1043A |

| 主要属性: | * |

| 次要属性: | * |

| 已供物品: | 板 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页当前第68页第69页第70页第71页第72页

�� �

�

�

�ADP1043A�

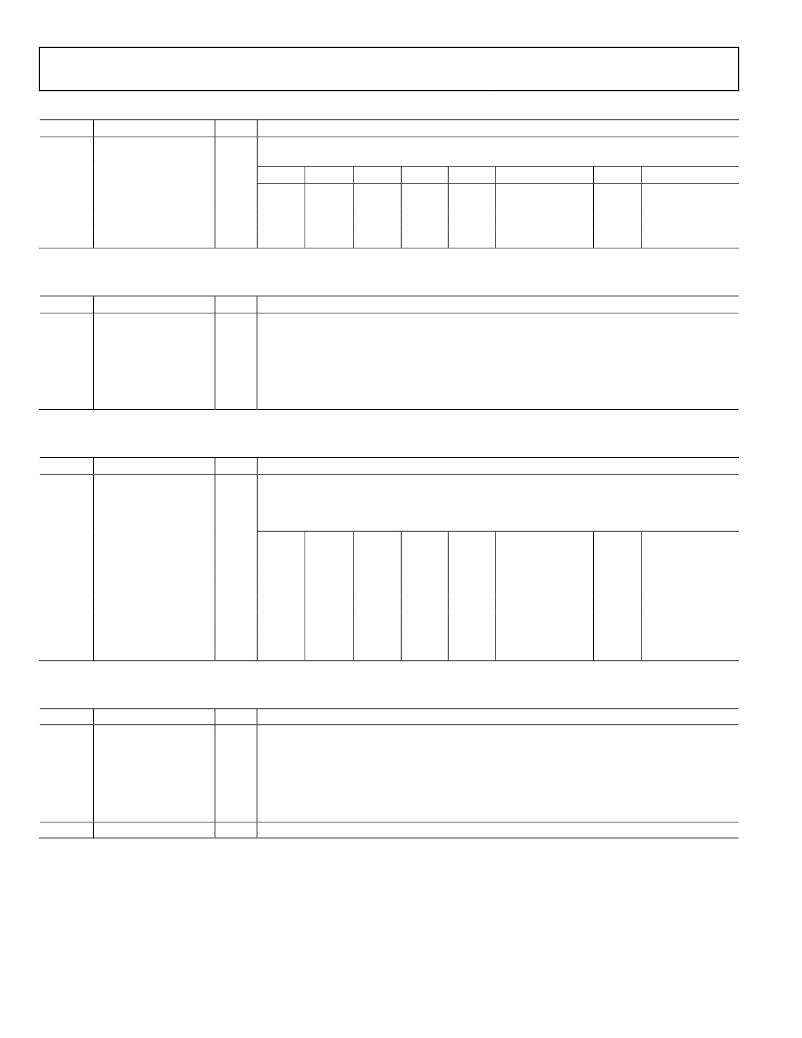

�Table 116. Register 0x45—OUTB Rising� Edge� Dead� Time� in� Resonant� Mode�

�Bits�

�[7:0]�

�Name�

�Δt� 3� (rising� edge� dead�

�time� of� OUTB)�

�R/W�

�R/W�

�Description�

�This� register� sets� Δt� 3� ,� which� is� the� delay� time� of� the� rising� edge� of� OUTB� from� the� start� of� the�

�switching� cycle,� t� A� .� Each� LSB� corresponds� to� 5� ns� of� resolution.�

�Bit� 7�

�0�

�0�

�…�

�1�

�Bit� 6�

�0�

�0�

�…�

�1�

�Bit� 5�

�0�

�0�

�…�

�1�

�Bit� 4�

�0�

�0�

�…�

�1�

�Bit� 3�

�0�

�0�

�…�

�1�

�Bit� 2�

�0�

�0�

�…�

�1�

�Bit� 1�

�0�

�0�

�…�

�1�

�Bit� 0�

�0�

�1�

�…�

�1�

�Δt� 3� (ns)�

�0�

�5�

�…�

�1275�

�Table� 117.� Register� 0x46—Highest� Switching� Frequency� Limit� Setting� (Minimum� Switching� Cycle� in� Resonant� Mode)�

�Bits�

�[7:0]�

�Name�

�Highest� frequency�

�R/W�

�R/W�

�Description�

�This� register� contains� the� eight� MSBs� of� the� 12-bit� value� of� the� highest� switching� frequency� (mini-�

�mum� switching� cycle)� limit.� This� value� is� always� used� with� the� top� four� bits� of� Register� 0x48,�

�which� contain� the� four� LSBs� of� the� highest� switching� frequency� limit.� Each� LSB� of� the� 12-bit�

�value� corresponds� to� 5� ns� of� resolution� for� the� switching� cycle.� For� example,� if� Register� 0x46�

�is� set� to� 0x10� (16� decimal)� and� Bits[7:4]� of� Register� 0x48� are� set� to� 0x9� (9� decimal),� the� minimum�

�switching� cycle� is� (16� ×� 16� +� 9)� ×� 5� ns� =� 1.325� μs,� and� the� highest� switching� frequency� limit� is�

�1/1.325� μs� =� 755� kHz.�

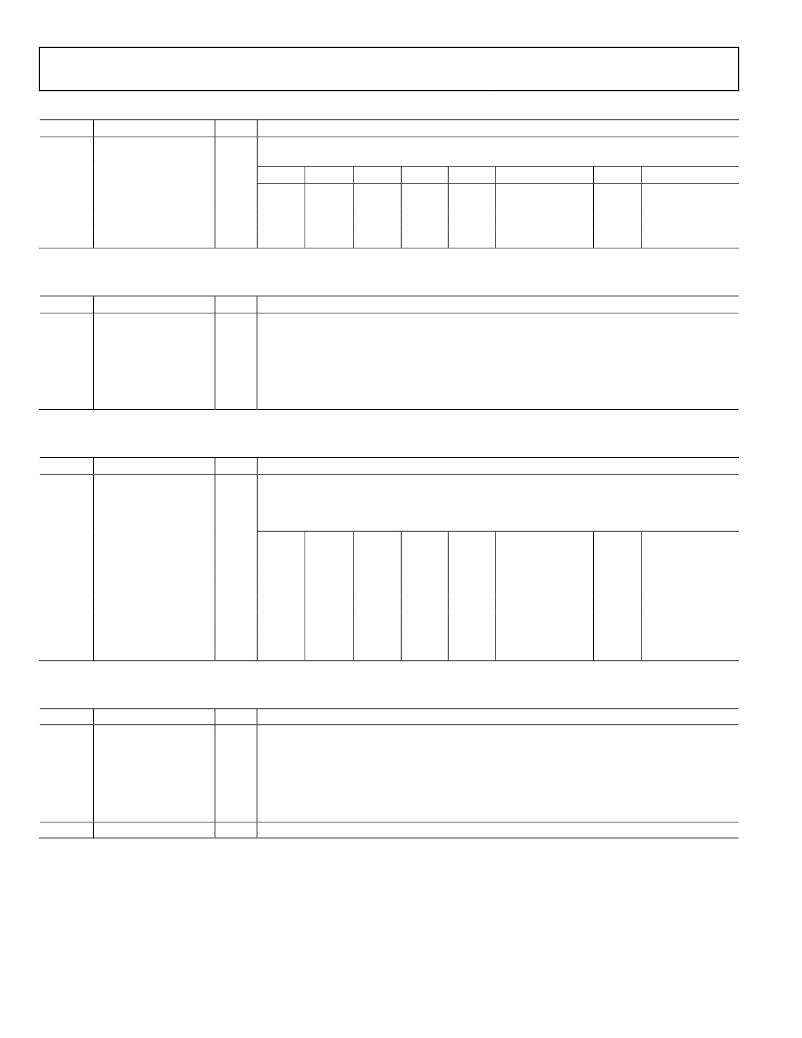

�Table 118. Register 0x47—OUTB Fallin� g� Edge� Dead� Time� in� Resonant� Mode�

�Bits�

�[7:0]�

�Name�

�Δt� 4� (falling� edge� dead�

�time� of� OUTB)�

�R/W�

�R/W�

�Description�

�This� register� sets� Δt� 4� ,� which� is� the� difference� between� the� falling� edge� of� OUTB� and� the� mid-�

�point� of� the� switching� cycle,� t� B� .� Each� LSB� corresponds� to� 5� ns� of� resolution.� When� the� register�

�value� is� from� 0x00� to� 0x7F,� the� falling� edge� of� OUTB� is� trailing� t� B� .� When� the� value� is� from� 0x80�

�to� 0xFF,� the� falling� edge� of� OUTB� is� leading� t� B� .�

�Bit� 7�

�0�

�0�

�…�

�0�

�1�

�…�

�1�

�Bit� 6�

�0�

�0�

�…�

�1�

�0�

�…�

�1�

�Bit� 5�

�0�

�0�

�…�

�1�

�0�

�…�

�1�

�Bit� 4�

�0�

�0�

�…�

�1�

�0�

�…�

�1�

�Bit� 3�

�0�

�0�

�…�

�1�

�0�

�…�

�1�

�Bit� 2�

�0�

�0�

�…�

�1�

�0�

�…�

�1�

�Bit� 1�

�0�

�0�

�…�

�1�

�0�

�…�

�1�

�Bit� 0�

�0�

�1�

�…�

�1�

�0�

�…�

�1�

�Δt� 4�

�0� ns�

�5� ns� trailing�

�…�

�635� ns� trailing�

�640� ns� leading�

�…�

�5� ns� leading�

�Table� 119.� Register� 0x48—Highest� Switching� Frequency� Limit� Setting� (Minimum� Switching� Cycle� in� Resonant� Mode)�

�Bits�

�[7:4]�

�Name�

�Highest� frequency�

�R/W�

�R/W�

�Description�

�This� register� contains� the� four� LSBs� of� the� 12-bit� value� of� the� highest� switching� frequency� (mini-�

�mum� switching� cycle)� limit.� This� value� is� always� used� with� the� eight� bits� of� Register� 0x46,� which�

�contain� the� eight� MSBs� of� the� highest� switching� frequency� limit.� Each� LSB� of� the� 12-bit� value�

�corresponds� to� 5� ns� of� resolution� for� the� switching� cycle.� For� example,� if� Register� 0x46� is� set�

�to� 0x10� (16� decimal)� and� Bits[7:4]� of� Register� 0x48� are� set� to� 0x9� (9� decimal),� the� minimum�

�switching� cycle� is� (16� ×� 16� +� 9)� ×� 5� ns� =� 1.325� μs,� and� the� highest� switching� frequency� limit� is�

�1/1.325� μs� =� 755� kHz.�

�[3:0]�

�Reserved�

�R/W�

�Reserved.�

�Rev.� 0� |� Page� 68� of� 72�

�相关PDF资料 |

PDF描述 |

|---|---|

| ADP1046-100-EVALZ | BOARD EVAL FOR ADP1046-100 |

| ADP1048-600-EVALZ | BOARD EVAL ADP1048-600 |

| ADP190CB-EVALZ | BOARD EVAL ADP190 |

| ADP191CB-EVALZ | EVAL BOARD FOR ADP191 |

| ADP194CB-EVALZ | BOARD EVAL FOR ADP194ACBZ |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADP1043AIF300EVALZ | 制造商:Analog Devices 功能描述:ADP1043A 300W EVALUATION BOARD - Boxed Product (Development Kits) |

| ADP1043A-USB-Z | 功能描述:EVAL BOARD DIG POWER SUPPLY RoHS:是 类别:编程器,开发系统 >> 配件 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program RoHS指令信息:IButton RoHS Compliance Plan 标准包装:1 系列:- 附件类型:USB 至 1-Wire? RJ11 适配器 适用于相关产品:1-Wire? 设备 产品目录页面:1429 (CN2011-ZH PDF) |

| ADP1043-EVALZ | 制造商:Analog Devices 功能描述:EVALUATION BOARDS - Bulk |

| ADP1043FB100-EVALZ | 制造商:Analog Devices 功能描述:ADP1043 100W EVALUATION BOARD |

| ADP1045ACPZ-RL | 制造商:Analog Devices 功能描述: |

发布紧急采购,3分钟左右您将得到回复。