- 您现在的位置:买卖IC网 > PDF目录170654 > DAC5688IRGCTG4 (TEXAS INSTRUMENTS INC) PARALLEL, WORD INPUT LOADING, 0.0104 us SETTLING TIME, 16-BIT DAC, PQCC64 PDF资料下载

参数资料

| 型号: | DAC5688IRGCTG4 |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | DAC |

| 英文描述: | PARALLEL, WORD INPUT LOADING, 0.0104 us SETTLING TIME, 16-BIT DAC, PQCC64 |

| 封装: | 9 X 9 MM, GREEN, PLASTIC, VQFN-64 |

| 文件页数: | 19/56页 |

| 文件大小: | 1321K |

| 代理商: | DAC5688IRGCTG4 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页

SDENB

SCLK

InstructionCycle

Data TransferCycle(s)

SDIO

r/w N1

N0 A4

A3 A2

A1

A 0 D7 D6

D5 D4

D3 D2 D1

D0

SDENB

SCLK

SDIO

t s(SDENB)

t s(SDIO)

t

h ( SDIO)

t SCLK

t

SCLKH

t

SCLKL

SLLS880C – DECEMBER 2007 – REVISED AUGUST 2010

www.ti.com

Table 2. Instruction Byte of the Serial Interface

Bit

7

6

5

4

3

2

1

0

Description

R/W

N1

N0

A4

A3

A2

A1

A0

R/W

Identifies the following data transfer cycle as a read or write operation. A high indicates a read operation from DAC5688 and

a low indicates a write operation to DAC5688.

[N1 : N0]

Identifies the number of data bytes to be transferred per Table 3. Data is transferred MSB first.

Table 3. Number of Transferred Bytes Within One

Communication Frame

N1

N0

Description

0

Transfer 1 Byte

0

1

Transfer 2 Bytes

1

0

Transfer 3 Bytes

1

Transfer 4 Bytes

[A4 : A0]

Identifies the address of the register to be accessed during the read or write operation. For multi-byte transfers, this address

is the starting address. Note that the address is written to the DAC5688 MSB first and counts down for each byte

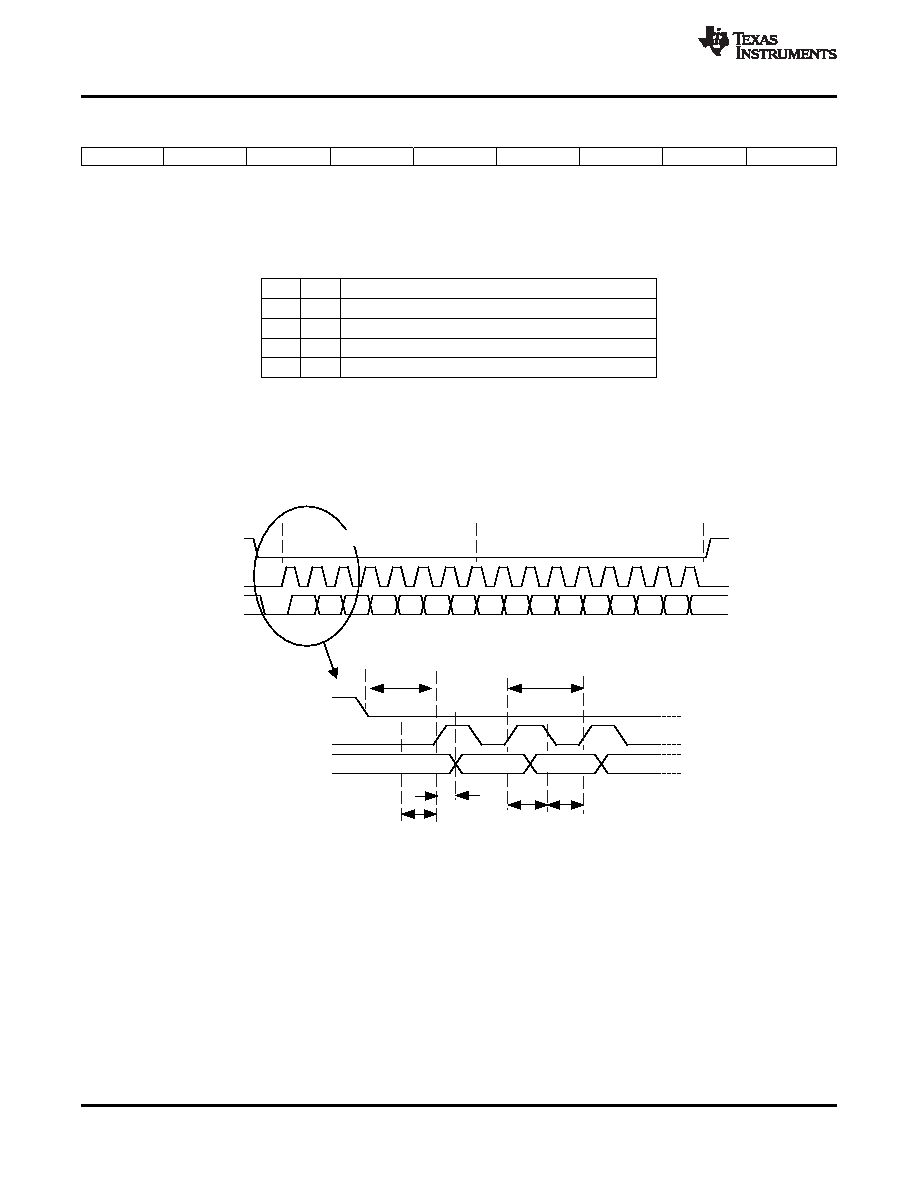

Figure 20 shows the serial interface timing diagram for a DAC5688 write operation. SCLK is the serial interface

clock input to DAC5688. Serial data enable SDENB is an active low input to DAC5688. SDIO is serial data in.

Input data to DAC5688 is clocked on the rising edges of SCLK.

Figure 20. Serial Interface Write Timing Diagram

Figure 21 shows the serial interface timing diagram for a DAC5688 read operation. SCLK is the serial interface

clock input to DAC5688. Serial data enable SDENB is an active low input to DAC5688. SDIO is serial data in

during the instruction cycle. In 3 pin configuration, SDIO is data out from DAC5688 during the data transfer

cycle(s), while SDO is in a high-impedance state. In 4 pin configuration, SDO is data out from DAC5688 during

the data transfer cycle(s). The SDIO/SDO data is output on the falling edge of SCLK. At the end of the data

transfer, SDO will output low on the final falling edge of SCLK until the rising edge of SDENB when it will 3-state.

26

Copyright 2007–2010, Texas Instruments Incorporated

Product Folder Link(s): DAC5688

相关PDF资料 |

PDF描述 |

|---|---|

| DAC702LH | PARALLEL, WORD INPUT LOADING, 4 us SETTLING TIME, 16-BIT DAC, CDIP24 |

| DAC7545KUG4 | PARALLEL, WORD INPUT LOADING, 2 us SETTLING TIME, 12-BIT DAC, PDSO20 |

| DAC7545JP | PARALLEL, WORD INPUT LOADING, 2 us SETTLING TIME, 12-BIT DAC, PDIP20 |

| DAC7545KP | PARALLEL, WORD INPUT LOADING, 2 us SETTLING TIME, 12-BIT DAC, PDIP20 |

| DAC7554IDGSR | SERIAL INPUT LOADING, 5 us SETTLING TIME, 12-BIT DAC, PDSO10 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DAC5689 | 制造商:TI 制造商全称:Texas Instruments 功能描述:16-BIT 800 MSPS 2x-8x INTERPOLATING DUAL-CHANNEL DIGITAL-TO-ANALOG CONVERTER (DAC) |

| DAC5689EVM | 功能描述:数据转换 IC 开发工具 DAC5689 Eval Mod RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V |

| DAC5689IRGCR | 功能描述:数模转换器- DAC 16B,800MSPS 2x-8x Int Dual-Channel DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

| DAC5689IRGCT | 功能描述:数模转换器- DAC 16B,800MSPS 2x-8x Int Dual-Channel DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

| DAC56P | 制造商:TI 制造商全称:Texas Instruments 功能描述:Monolithic 16-Bit Resolution DIGITAL-TO-ANALOG CONVERTER |

发布紧急采购,3分钟左右您将得到回复。