- 您现在的位置:买卖IC网 > PDF目录69032 > MCM16Y1BACFT16 (MOTOROLA INC) 16-BIT, MROM, MICROCONTROLLER, PQFP160 PDF资料下载

参数资料

| 型号: | MCM16Y1BACFT16 |

| 厂商: | MOTOROLA INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 16-BIT, MROM, MICROCONTROLLER, PQFP160 |

| 封装: | QFP-160 |

| 文件页数: | 79/138页 |

| 文件大小: | 784K |

| 代理商: | MCM16Y1BACFT16 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页当前第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页

MC68HC16Y1

MOTOROLA

MC68HC16Y1TS/D

45

The SYNCR Y field determines the count modulus for a modulo 64 down counter, causing it to divide

by a value of Y

+ 1. When either W or Y value changes, there is a VCO relock delay.

Clock frequency is determined by SYNCR bit settings as follows:

FSYSTEM = FREFERENCE [4(Y + 1)(2

2W + X)]

In order for the device to perform correctly, the clock frequency selected by the W, X, and Y bits must

be within the limits specified for the MCU. Maximum specified clock frequency with a 32.768 kHz refer-

ence is 16.78 kHz.

VCO frequency is determined by:

FVCO = FSYSTEM (2 – X), for 32.768 kHz devices.

The reset state of SYNCR ($3F00) produces a modulus-64 count.

3.4.3 Clock Control

The clock control circuits determine system clock frequency and clock operation under special circum-

stances, such as loss of synthesizer reference or low-power mode. Clock source is determined by the

logic state of the MODCLK pin during reset.

When the on-chip clock synthesizer is used, system clock frequency is controlled by the bits in the upper

byte of SYNCR. Bits in the lower byte show status of or control operation of internal and external clocks.

Because the CPU16 always operates in supervisor mode, SYNCR can be read or written at any time.

W — Frequency Control (VCO)

This bit controls a prescaler tap in the synthesizer feedback loop. Setting the bit increases the VCO

speed by a factor of four. VCO relock delay is required.

X — Frequency Control Bit (Prescale)

This bit controls a divide by two prescaler that is not in the synthesizer feedback loop. Setting it doubles

clock speed without changing VCO speed. There is no VCO relock delay.

Y[5:0] — Frequency Control (Counter)

The Y field controls the modulus down counter in the synthesizer feedback loop, causing it to divide by

a value of Y

+ 1. Values range from 0 to 63. VCO relock delay is required.

EDIV — E Clock Divide Rate

0 = ECLK frequency is system clock divided by 8.

1 = ECLK frequency is system clock divided by 16.

ECLK is an external M6800 bus clock available on pin ADDR23. See 3.9 Chip Selects for more infor-

mation.

SLIMP — Limp Mode Flag

0 = External crystal is VCO reference.

1 = Loss of crystal reference.

When the on-chip synthesizer is used, loss of reference frequency will cause SLIMP to be set. The VCO

continues to run using the base control voltage. Maximum limp frequency is maximum specified system

clock frequency. X-bit state affects limp frequency.

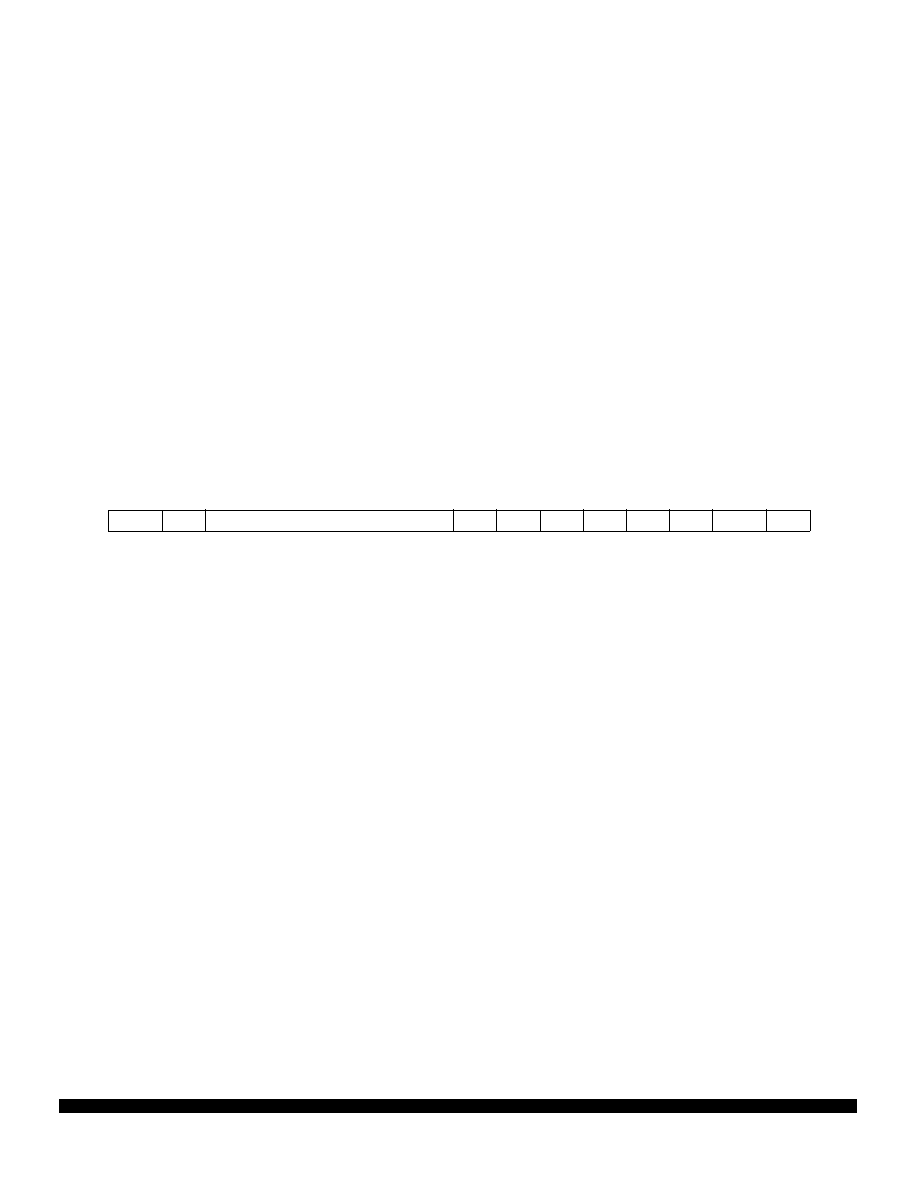

SYNCR — Clock Synthesizer Control Register

$YFFA04

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

W

X

Y

EDIV

0

SLIMP

SLOCK RSTEN

STSCIM

STEXT

RESET:

0

1

0

U

0

相关PDF资料 |

PDF描述 |

|---|---|

| MCM16Y1BGCFT16 | 16-BIT, MROM, MICROCONTROLLER, PQFP160 |

| M68HC16Y1CFC | 16-BIT, MROM, MICROCONTROLLER, PQFP16 |

| MCV14AI/SL | 8-BIT, FLASH, 20 MHz, RISC MICROCONTROLLER, PDSO14 |

| MCV14ATI/SL | 8-BIT, FLASH, 20 MHz, RISC MICROCONTROLLER, PDSO14 |

| MCV14AI/P | 8-BIT, FLASH, 20 MHz, RISC MICROCONTROLLER, PDIP14 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MCM16Z2BCFC16 | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Symbols and Operators, CPU16 Register Mnemonics |

| MCM16Z2BCFC16B1 | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Symbols and Operators, CPU16 Register Mnemonics |

| MCM16Z2BCFC20 | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Symbols and Operators, CPU16 Register Mnemonics |

| MCM16Z2BCFC20B1 | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:M68HC16Z Series users manual |

| MCM16Z2BCFC25 | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:M68HC16Z Series users manual |

发布紧急采购,3分钟左右您将得到回复。