- 您现在的位置:买卖IC网 > PDF目录224505 > MT46V32M16TG-75ELIT 32M X 16 DDR DRAM, 0.75 ns, PDSO66 PDF资料下载

参数资料

| 型号: | MT46V32M16TG-75ELIT |

| 元件分类: | DRAM |

| 英文描述: | 32M X 16 DDR DRAM, 0.75 ns, PDSO66 |

| 封装: | 0.400 INCH, PLASTIC, TSOP-66 |

| 文件页数: | 66/82页 |

| 文件大小: | 2855K |

| 代理商: | MT46V32M16TG-75ELIT |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页当前第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页

512Mb: x4, x8, x16

DDR SDRAM

09005aef80a1d9e7

Micron Technology, Inc., reserves the right to change products or specifications without notice.

512MBDDRx4x8x16_2.fm - Rev. H 7/04 EN

69

2000 Micron Technology, Inc. All rights reserved.

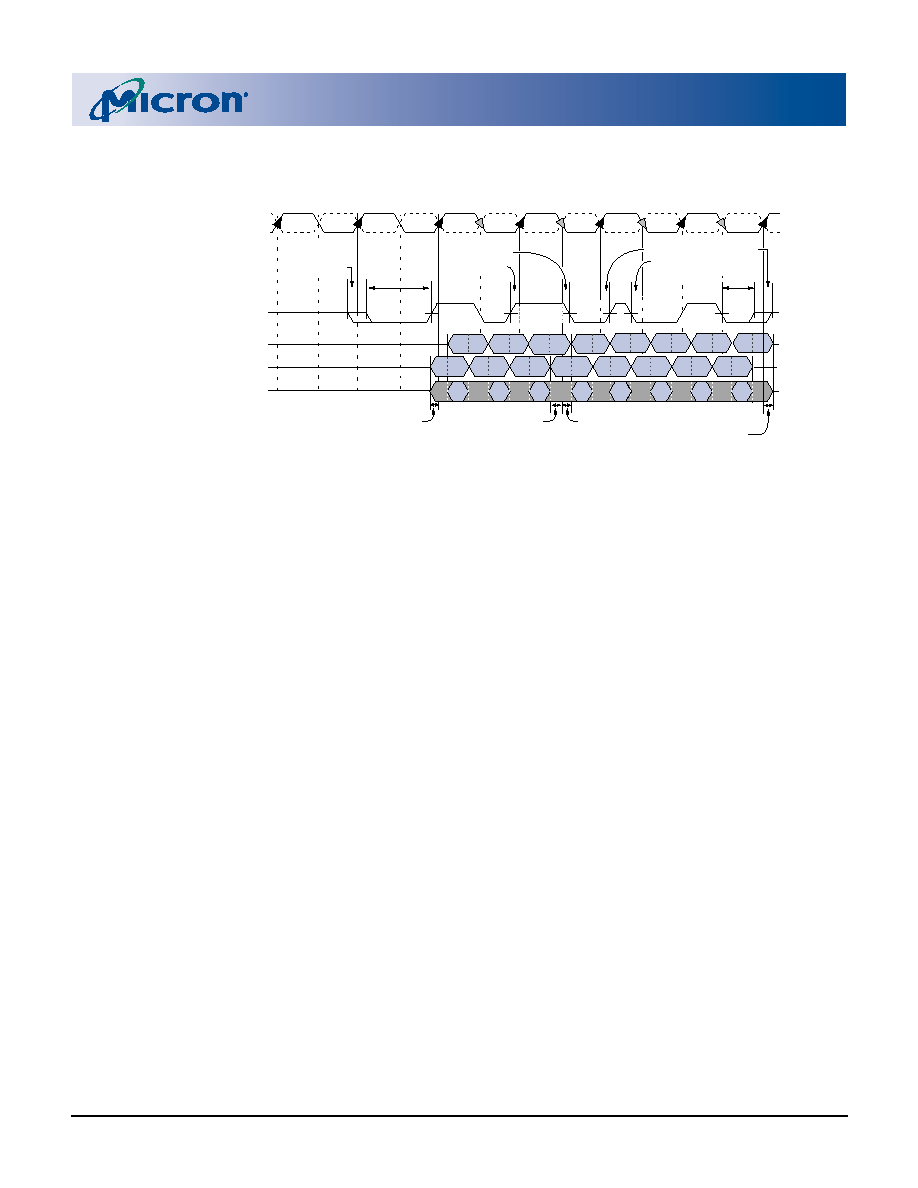

Figure 42: Data Output Timing – tAC and tDQSCK

NOTE:

1. tDQSCK is the DQS output window relative to CK and is the “long term” component of DQS skew.

2. DQ transitioning after DQS transition define tDQSQ window.

3. All DQ must transition by tDQSQ after DQS transitions, regardless of tAC.

4. tAC is the DQ output window relative to CK, and is the “long term” component of DQ skew.

5. tLZ (MIN) and tAC (MIN) are the first valid signal transition.

6. tHZ (MAX),and tAC (MAX) are the latest valid signal transition.

7. READ command with CL = 2 issued at T0.

CK

CK#

DQS, or LDQS/UDQS2

T07

T1

T2

T3

T4

T5

T2n

T3n

T4n

T5n

T6

tRPST

tLZ (MIN)

tDQSCK1 (MAX)

tDQSCK1 (MIN)

tDQSCK1 (MAX)

tDQSCK1 (MIN)

tHZ(MAX)

tRPRE

DQ (Last data valid)

DQ (First data valid)

All DQ values, collectively3

tAC4 (MIN)

tAC4 (MAX)

tLZ (MIN)

tHZ (MAX)

T2

T2n

T3n

T4n

T5n

T2n

T3n

T4n

T5n

T3

T4

T5

T2

T3

T4

T5

T3

相关PDF资料 |

PDF描述 |

|---|---|

| MT46V32M16BN-5BLIT | 32M X 16 DDR DRAM, 0.7 ns, PBGA60 |

| MT46V32M81AZ4-6T:G | 32M X 4 DDR DRAM, 0.75 ns, PDSO66 |

| MT47H128M8HV-187ELIT:E | 128M X 8 DDR DRAM, 0.35 ns, PBGA60 |

| MT47H128M8HQ-187ELAT:E | 128M X 8 DDR DRAM, 0.35 ns, PBGA60 |

| MT48LC2M32B1TG-7 | 2M X 32 SYNCHRONOUS DRAM, 5.5 ns, PDSO86 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MT46V32M16TG-75L | 制造商:MICRON 制造商全称:Micron Technology 功能描述:DOUBLE DATA RATE DDR SDRAM |

| MT46V32M16TG-75Z | 制造商:MICRON 制造商全称:Micron Technology 功能描述:DOUBLE DATA RATE DDR SDRAM |

| MT46V32M16TG-75ZL | 制造商:MICRON 制造商全称:Micron Technology 功能描述:DOUBLE DATA RATE DDR SDRAM |

发布紧急采购,3分钟左右您将得到回复。