- 您现在的位置:买卖IC网 > PDF目录229297 > MT46V32M8FG-6TIT:G 32M X 8 DDR DRAM, 0.7 ns, PBGA60 PDF资料下载

参数资料

| 型号: | MT46V32M8FG-6TIT:G |

| 元件分类: | DRAM |

| 英文描述: | 32M X 8 DDR DRAM, 0.7 ns, PBGA60 |

| 封装: | (8 X 14) MM, PLASTIC, FBGA-60 |

| 文件页数: | 76/93页 |

| 文件大小: | 3632K |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页当前第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页

PDF: 09005aef80768abb/Source: 09005aef82a95a3a

Micron Technology, Inc., reserves the right to change products or specifications without notice.

DDR_x4x8x16_Core2.fm - 256Mb DDR: Rev. O, Core DDR: Rev. B 1/09 EN

76

2003 Micron Technology, Inc. All rights reserved.

256Mb: x4, x8, x16 DDR SDRAM

Operations

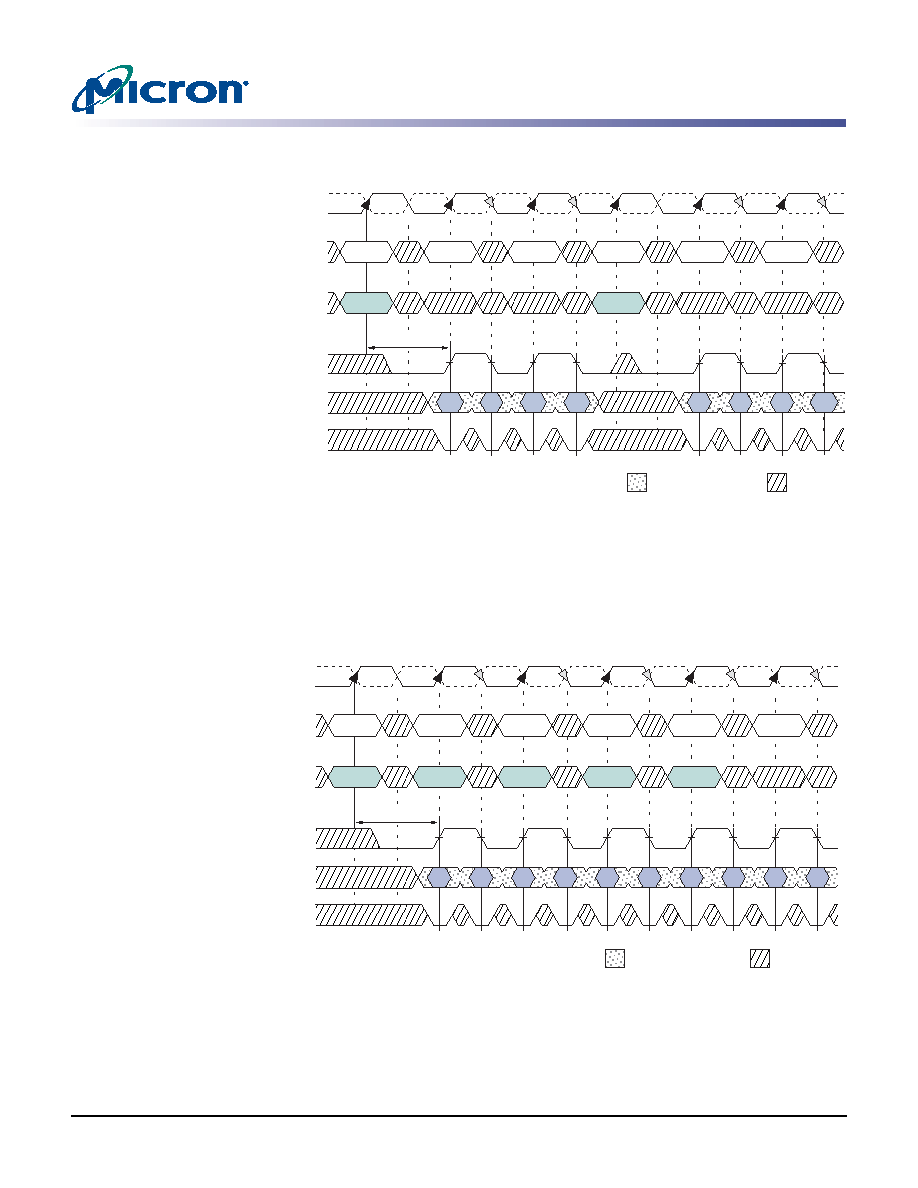

Figure 40:

Nonconsecutive WRITE-to-WRITE

Notes:

1. DI b (or n) = data-in from column b (or column n).

2. Three subsequent elements of data-in are applied in the programmed order following DI b.

3. Three subsequent elements of data-in are applied in the programmed order following DI n.

4. An uninterrupted burst of 4 is shown.

5. Each WRITE command may be to any bank.

Figure 41:

Random WRITE Cycles

Notes:

1. DI b (or x or n or a or g) = data-in from column b (or column x, or column n, or column a, or

column g).

2. b', x', n', a' or g' indicate the next data-in following DO b, DO x, DO n, DO a, or DO g,

respectively.

3. Programmed BL = 2, BL = 4, or BL = 8 in cases shown.

4. Each WRITE command may be to any bank.

CK

Command

WRITE

NOP

Address

Bank,

Col b

WRITE

Bank,

Col n

T0

T1

T2

T3

T2n

T4

T5

T4n

T1n

T5n

DQ

DQS

DM

DI

n

DI

b

tDQSS (NOM)

tDQSS

Don’t Care

Transitioning Data

CK#

tDQSS (NOM)

CK

CK#

Command

WRITE

NOP

Address

Bank,

Col b

Bank,

Col x

Bank,

Col n

Bank,

Col g

WRITE

Bank,

Col a

T0

T1

T2

T3

T2n

T4

T5

T4n

T1n

T3n

T5n

DQ

DQS

DM

DI

b

DI

b'

DI

x

DI

x'

DI

n

DI

n'

DI

a

DI

a'

DI

g

DI

g'

Don’t Care

Transitioning Data

相关PDF资料 |

PDF描述 |

|---|---|

| MT46V32M8BG-6AT:G | 32M X 8 DDR DRAM, 0.7 ns, PBGA60 |

| M29F800FB55N3E2 | 512K X 16 FLASH 5V PROM, 55 ns, PDSO48 |

| MC12L1NZGF | ROTARY SWITCH-12POSITIONS, SP12T, LATCHED, 0.25A, 28VDC, PANEL MOUNT-THREADED |

| MD00S1NCQF | ROTARY SWITCH-6POSITIONS, DP6T, LATCHED, 0.25A, 28VDC, THROUGH HOLE-STRAIGHT |

| MD06L1NZGD | ROTARY SWITCH-6POSITIONS, DP6T, LATCHED, 0.25A, 28VDC, PANEL MOUNT-THREADED |

相关代理商/技术参数 |

参数描述 |

|---|

发布紧急采购,3分钟左右您将得到回复。