- 您现在的位置:买卖IC网 > PDF目录98080 > SII3114CT176 PCI BUS CONTROLLER, PQFP176 PDF资料下载

参数资料

| 型号: | SII3114CT176 |

| 元件分类: | 总线控制器 |

| 英文描述: | PCI BUS CONTROLLER, PQFP176 |

| 封装: | TQFP-176 |

| 文件页数: | 100/127页 |

| 文件大小: | 564K |

| 代理商: | SII3114CT176 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页当前第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页

SiI3114 PCI to Serial ATA Controller

Data Sheet

Silicon Image, Inc.

SiI-DS-0103-D

66

2007 Silicon Image, Inc.

Bit [15]: Reserved (R). This bit field is reserved and returns zeros on a read.

Bit [14]: Watchdog Int Ena (R/W) – Channel X Watchdog Interrupt Enable. This bit is set to enable an

interrupt when the Watchdog timer expires.

Bit [13]: Watchdog Ena (R/W) – Channel X Watchdog Timer Enable. This bit is set to enable the watchdog

timer for Channel X. This bit is cleared to disable the watchdog timer.

Bit [12]: Watchdog Timeout (R/W1C) – Channel X Watchdog Timer Timeout. This bit set indicates that the

watchdog timer for Channel X timed out. When enabled, and IORDY monitoring bit is also enabled, during

Channel X PIO operation, the watchdog counter starts counting when IORDY signal is deasserted. If after

256 PCI clocks, the IORDY signal is still deasserted, the Watchdog Timer expires, this bit is set, the

SiI3114 continues its operation, and stops monitoring IORDY signal. Software writes one to clear this bit.

Once this bit is cleared, the SiI3114 starts monitoring IORDY on channel X again.

Bit [11]: Interrupt Status (R) – Channel X Interrupt Status. This bit set indicates that an interrupt is pending

on Channel X. This bit provides real-time status of the Channel X interrupt.

Bit [10]: Virtual DMA Int (R) – Channel X Virtual DMA Completion Interrupt. This bit set indicates that the

Virtual DMA data transfer has completed. This bit is cleared when PBM enable (bit 0 in PCI Bus Master –

Channel X) is cleared.

Bit [09:03]: Reserved (R). This bit field is reserved and returns zeros on a read.

Bit [02]: Channel Rst (R/W) – Channel X Reset. When this bit is set, Channel X RST signal is asserted.

Bit [01]: Buffered Cmd (R) – Channel X Buffered Command Active. This bit set indicates that a Buffered

Command is currently active. This bit is set when the first command byte is written to the command buffer.

This bit is cleared when all of the task file bytes, including the command byte, have been written to the

device.

Bit [00]: Reserved (R). This bit is reserved and returns one on a read.

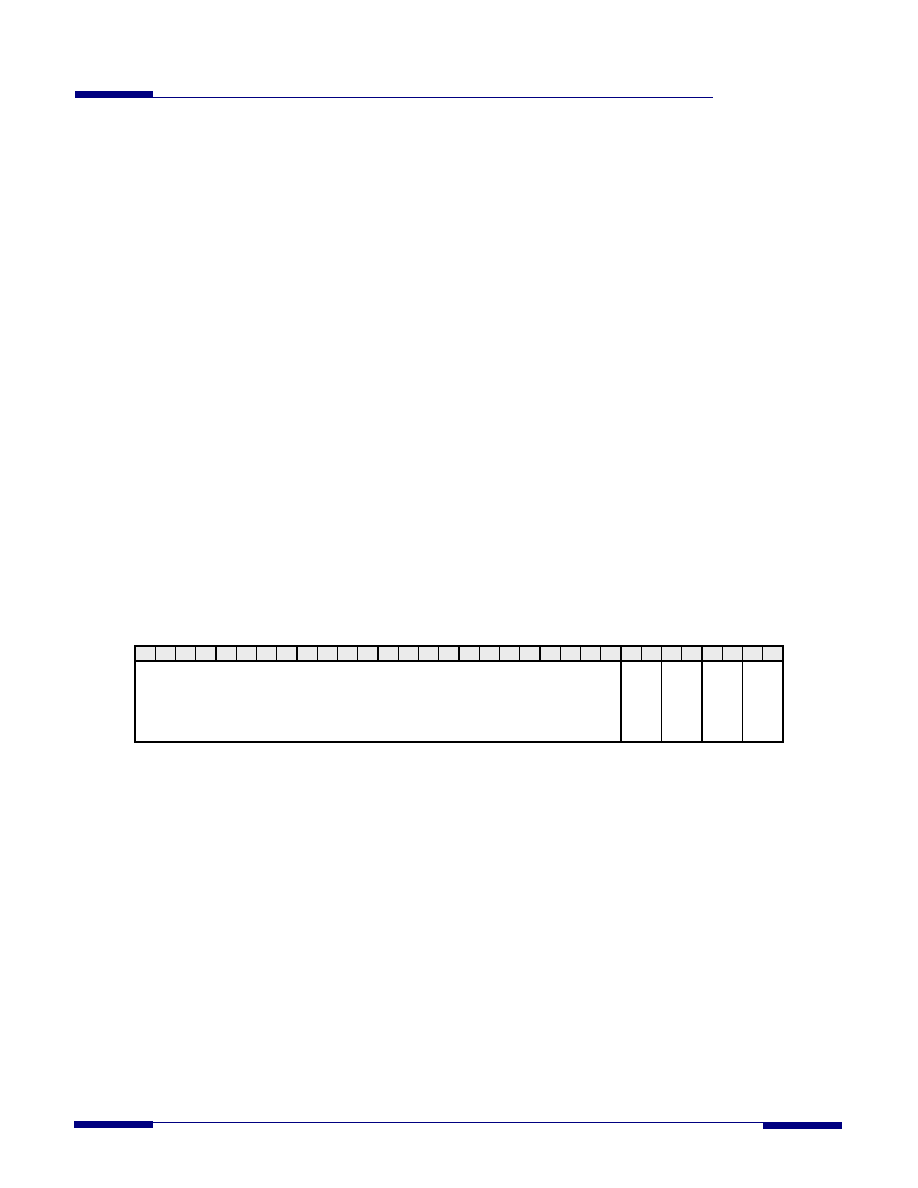

Data Transfer Mode – Channel X

Address Offset: B4H / F4H / 2B4H / 2F4H

Access Type: Read/Write

Reset Value: 0x0000_0022

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

Reserved

R

eserved

D

e

vice

1

Transf

er

Mode

R

eserved

D

evice

0

Transf

er

Mode

This register defines the transfer mode register for Channel 0 in the SiI3114. The register bits are defined below.

Bit [31:08]: Reserved (R). This bit field is reserved and returns zeros on a read.

Bit [07:06]: Reserved (R). This bit field is reserved and returns zeros on a read.

Bit [05:04]: Device 1 Transfer Mode (R/W) – Channel X Device 1 Data Transfer Mode. This bit field is used

to set the data transfer mode during PCI DMA transfer: 00B or 01B = PIO transfer; 10B or 11B = DMA

transfer.

Bit [03:02]: Reserved (R). This bit field is reserved and returns zeros on a read.

Bit [01:00]: Device 0 Transfer Mode (R/W) – Channel X Device 0 Data Transfer Mode. This bit field is used

to set the data transfer mode during PCI DMA transfer: 00B or 01B = PIO transfer; 10B or 11B = DMA

transfer.

相关PDF资料 |

PDF描述 |

|---|---|

| SII3114CTU | PCI BUS CONTROLLER, PQFP176 |

| SII3124ACBHU | PCI BUS CONTROLLER, PBGA364 |

| SII3512ECTU128 | PCI BUS CONTROLLER, PQFP128 |

| SII3531ACNU | PCI BUS CONTROLLER, QCC48 |

| SIO10N268-NU | MULTIFUNCTION PERIPHERAL, PQFP128 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SII3114CTU | 制造商:Silicon Image Inc 功能描述:PCI to Serial ATA Controller 176-Pin TQFP 制造商:SILICON 功能描述: |

| SII3124A | 制造商:SILICONIMAGE 制造商全称:SILICONIMAGE 功能描述:PCI-X to Serial ATA Controller |

| SII3124ACBHU | 制造商:SILICONIMAGE 制造商全称:SILICONIMAGE 功能描述:PCI-X to Serial ATA Controller |

| SII3132 | 制造商:SILICONIMAGE 制造商全称:SILICONIMAGE 功能描述:PCI Express to 2-Port Serial ATA II Host Controller |

| SII3132CNU | 制造商:Silicon Image Inc 功能描述:PCI Express to Serial ATA Controller 88-Pin QFN |

发布紧急采购,3分钟左右您将得到回复。