- 您现在的位置:买卖IC网 > PDF目录382636 > TMX20F2810PBKAEP (Texas Instruments, Inc.) Digital Signal Processors PDF资料下载

参数资料

| 型号: | TMX20F2810PBKAEP |

| 厂商: | Texas Instruments, Inc. |

| 元件分类: | 数字信号处理 |

| 英文描述: | Digital Signal Processors |

| 中文描述: | 数字信号处理器 |

| 文件页数: | 32/159页 |

| 文件大小: | 2084K |

| 代理商: | TMX20F2810PBKAEP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页当前第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页

Functional Overview

32

March 2004 Revised October 2004

SGUS051A

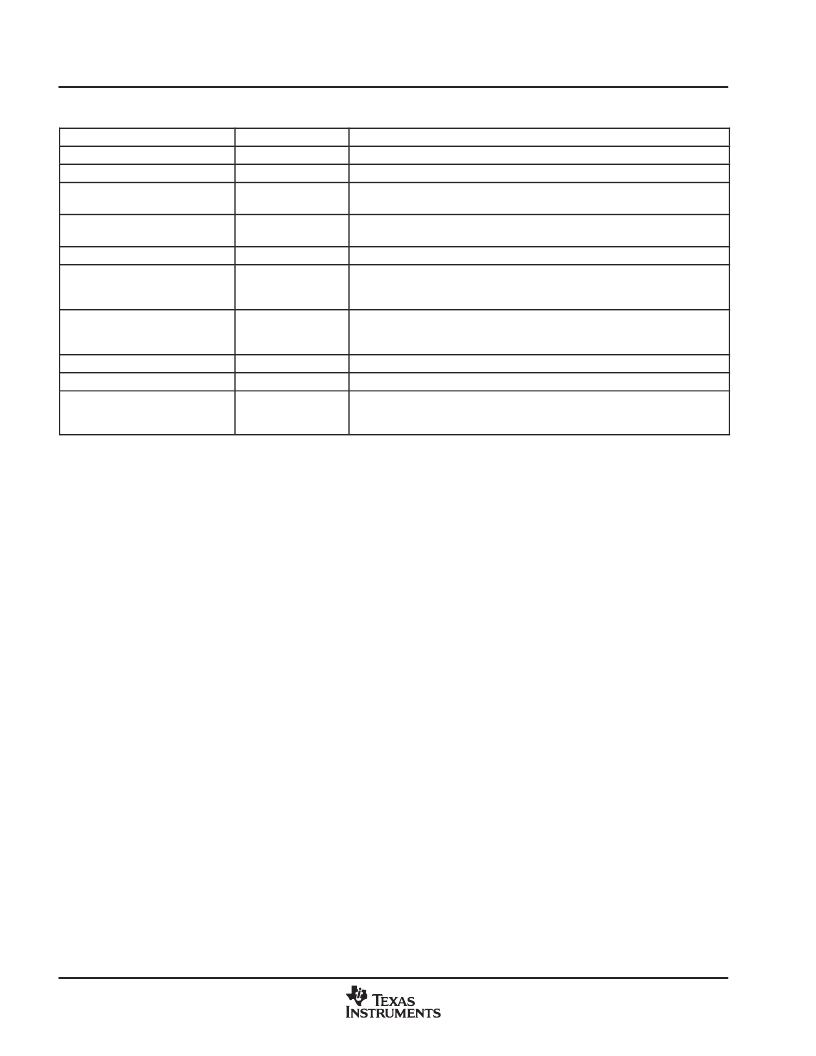

Table 33. Wait States

AREA

WAIT-STATES

COMMENTS

M0 and M1 SARAMs

0-wait

Fixed

Peripheral Frame 0

0-wait

Fixed

Peripheral Frame 1

0-wait (writes)

2-wait (reads)

Fixed

Peripheral Frame 2

0-wait (writes)

2-wait (reads)

Fixed

L0 & L1 SARAMs

0-wait

OTP (or ROM)

Programmable,

1-wait minimum

Programmed via the Flash registers. 1-wait-state operation is possible at a

reduced CPU frequency. See Section 3.2.6, Flash (F281x Only), for more

information.

Flash (or ROM)

Programmable,

0-wait minimum

Programmed via the Flash registers. 0-wait-state operation is possible at

reduced CPU frequency. The CSM password locations are hardwired for

16 wait-states. See Section 3.2.6, Flash (F281x Only), for more information.

H0 SARAM

0-wait

Fixed

Boot-ROM

1-wait

Fixed

XINTF

Programmable,

1-wait minimum

Programmed via the XINTF registers.

Cycles can be extended by external memory or peripheral.

0-wait operation is not possible.

3.2

Brief Descriptions

3.2.1

C28x CPU

The C28x

DSP generation is the newest member of the TMS320C2000

DSP platform. The C28x is source

code compatible to the 24x/240x DSP devices, hence existing 240x users can leverage their significant

software investment. Additionally, the C28x is a very efficient C/C++ engine, hence enabling users to develop

not only their system control software in a high-level language, but also enables math algorithms to be

developed using C/C++. The C28x is as efficient in DSP math tasks as it is in system control tasks that typically

are handled by microcontroller devices. This efficiency removes the need for a second processor in many

systems. The 32 x 32-bit MAC capabilities of the C28x and its 64-bit processing capabilities, enable the C28x

to efficiently handle higher numerical resolution problems that would otherwise demand a more expensive

floating-point processor solution. Add to this the fast interrupt response with automatic context save of critical

registers, resulting in a device that is capable of servicing many asynchronous events with minimal latency.

The C28x has an 8-level-deep protected pipeline with pipelined memory accesses. This pipelining enables

the C28x to execute at high speeds without resorting to expensive high-speed memories. Special

branch-look-ahead hardware minimizes the latency for conditional discontinuities. Special store conditional

operations further improve performance.

C28x and TMS320C2000 are trademarks of Texas Instruments.

相关PDF资料 |

PDF描述 |

|---|---|

| TMS320LC2404APGA | DSP CONTROLLERS |

| TMP320LC2401APAGA | DSP CONTROLLERS |

| TMP320LC2401APAGS | DSP CONTROLLERS |

| TMP320LC2401APGA | DSP CONTROLLERS |

| TMP320LC2401APGEA | DSP CONTROLLERS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TMX320C14FNL | 制造商:未知厂家 制造商全称:未知厂家 功能描述:16-Bit Digital Signal Processor |

| TMX320C16PGL | 制造商:未知厂家 制造商全称:未知厂家 功能描述:16-Bit Digital Signal Processor |

| TMX320C26FNL | 制造商:未知厂家 制造商全称:未知厂家 功能描述:16-Bit Digital Signal Processor |

| TMX320C2811GHHA | 制造商:TI 制造商全称:Texas Instruments 功能描述:TMS320R2811, TMS320R2812 Digital Signal Processors |

| TMX320C2811GHHQ | 制造商:TI 制造商全称:Texas Instruments 功能描述:TMS320R2811, TMS320R2812 Digital Signal Processors |

发布紧急采购,3分钟左右您将得到回复。