- 您现在的位置:买卖IC网 > PDF目录382636 > TMX20F2810PBKAEP (Texas Instruments, Inc.) Digital Signal Processors PDF资料下载

参数资料

| 型号: | TMX20F2810PBKAEP |

| 厂商: | Texas Instruments, Inc. |

| 元件分类: | 数字信号处理 |

| 英文描述: | Digital Signal Processors |

| 中文描述: | 数字信号处理器 |

| 文件页数: | 74/159页 |

| 文件大小: | 2084K |

| 代理商: | TMX20F2810PBKAEP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页当前第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页

Peripherals

74

March 2004 Revised October 2004

SGUS051A

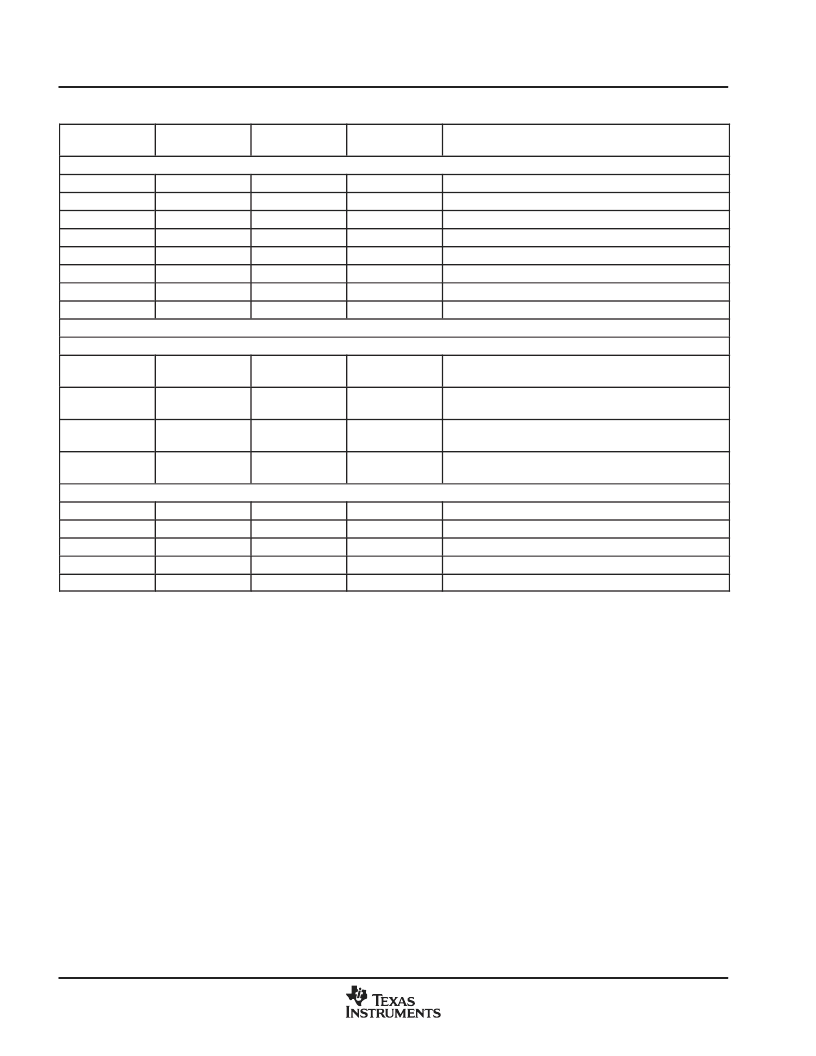

Table 47. McBSP Register Summary (Continued)

NAME

ADDRESS

0x00 78xxh

TYPE

(R/W)

RESET VALUE

(HEX)

DESCRIPTION

MULTICHANNEL CONTROL REGISTERS (CONTINUED)

RCERE

17

R/W

0x0000

McBSP Receive Channel Enable Register Partition E

RCERF

18

R/W

0x0000

McBSP Receive Channel Enable Register Partition F

XCERE

19

R/W

0x0000

McBSP Transmit Channel Enable Register Partition E

XCERF

1A

R/W

0x0000

McBSP Transmit Channel Enable Register Partition F

RCERG

1B

R/W

0x0000

McBSP Receive Channel Enable Register Partition G

RCERH

1C

R/W

0x0000

McBSP Receive Channel Enable Register Partition H

XCERG

1D

R/W

0x0000

McBSP Transmit Channel Enable Register Partition G

XCERH

1E

R/W

0x0000

McBSP Transmit Channel Enable Register Partition H

FIFO MODE REGISTERS (applicable only in FIFO mode)

FIFO Data Registers

DRR2

00

R

0x0000

McBSP Data Receive Register 2 Top of receive FIFO

Read First FIFO pointers will not advance

DRR1

01

R

0x0000

McBSP Data Receive Register 1 Top of receive FIFO

Read Second for FIFO pointers to advance

DXR2

02

W

0x0000

McBSP Data Transmit Register 2 Top of transmit FIFO

Write First FIFO pointers will not advance

DXR1

03

W

0x0000

McBSP Data Transmit Register 1 Top of transmit FIFO

Write Second for FIFO pointers to advance

FIFO Control Registers

MFFTX

20

R/W

0xA000

McBSP Transmit FIFO Register

MFFRX

21

R/W

0x201F

McBSP Receive FIFO Register

MFFCT

22

R/W

0x0000

McBSP FIFO Control Register

MFFINT

23

R/W

0x0000

McBSP FIFO Interrupt Register

MFFST

24

R/W

0x0000

McBSP FIFO Status Register

DRR2/DRR1 and DXR2/DXR1 share the same addresses of receive and transmit FIFO registers in FIFO mode.

FIFO pointers advancing is based on order of access to DRR2/DRR1 and DXR2/DXR1 registers.

相关PDF资料 |

PDF描述 |

|---|---|

| TMS320LC2404APGA | DSP CONTROLLERS |

| TMP320LC2401APAGA | DSP CONTROLLERS |

| TMP320LC2401APAGS | DSP CONTROLLERS |

| TMP320LC2401APGA | DSP CONTROLLERS |

| TMP320LC2401APGEA | DSP CONTROLLERS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TMX320C14FNL | 制造商:未知厂家 制造商全称:未知厂家 功能描述:16-Bit Digital Signal Processor |

| TMX320C16PGL | 制造商:未知厂家 制造商全称:未知厂家 功能描述:16-Bit Digital Signal Processor |

| TMX320C26FNL | 制造商:未知厂家 制造商全称:未知厂家 功能描述:16-Bit Digital Signal Processor |

| TMX320C2811GHHA | 制造商:TI 制造商全称:Texas Instruments 功能描述:TMS320R2811, TMS320R2812 Digital Signal Processors |

| TMX320C2811GHHQ | 制造商:TI 制造商全称:Texas Instruments 功能描述:TMS320R2811, TMS320R2812 Digital Signal Processors |

发布紧急采购,3分钟左右您将得到回复。