参数资料

| 型号: | XRT91L80IB |

| 厂商: | Exar Corporation |

| 文件页数: | 3/46页 |

| 文件大小: | 0K |

| 描述: | IC TXRX SONET/SDH 4BIT 196STBGA |

| 产品变化通告: | XRT91L80IB Obsolescence 6/Sept/2010 |

| 标准包装: | 126 |

| 类型: | 收发器 |

| 规程: | SONET/SDH |

| 电源电压: | 3.3V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 196-LFBGA |

| 供应商设备封装: | 196-STBGA(12x12) |

| 包装: | 托盘 |

第1页第2页当前第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页

xr

XRT91L80

REV. 1.0.0

2.488/2.666 GBPS STS-48/STM-16 SONET/SDH TRANSCEIVER

9

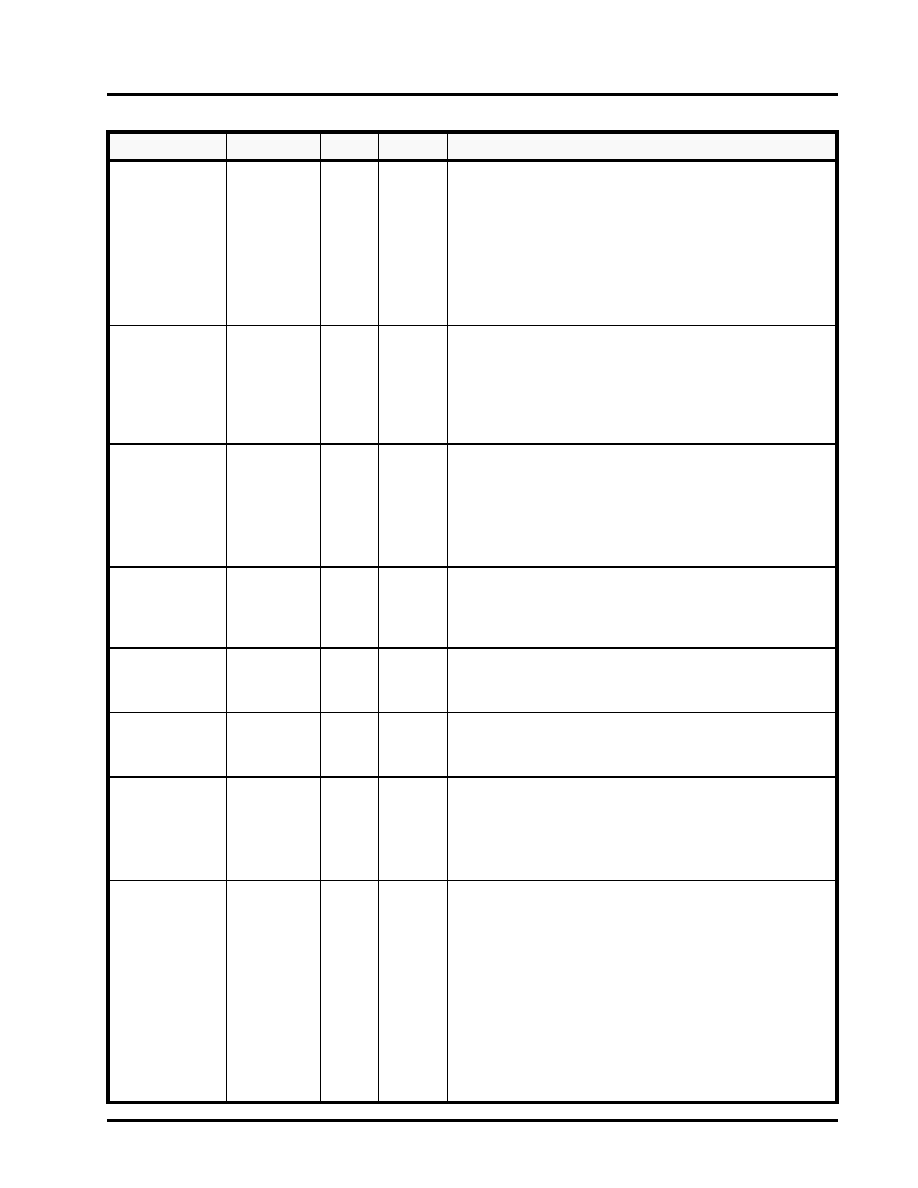

RECEIVER SECTION

NAME

LEVEL

TYPE

PIN

DESCRIPTION

RXDO0P

RXDO0N

RXDO1P

RXDO1N

RXDO2P

RXDO2N

RXDO3P

RXDO3N

LVDS

O

E13

F13

C14

D14

C13

D13

A14

B14

Receive Parallel Data Output

622Mbps 4-bit parallel receive data output is updated simulta-

neously on the rising edge of the RXPCLKOP/N output. The 4-

bit parallel interface is de-multiplexed from the receive serial

data input MSB first (RXDO3P/N).

NOTE: The XRT91L80 can output 666.51 Mbps 4-bit parallel

receive data output for Forward Error Correction (FEC)

Applications.

RXPCLKOP

RXPCLKON

LVDS

O

E14

F14

Receive Parallel Clock Output

622.08 MHz parallel clock output used to update the 4-bit paral-

lel receive data output RXDO[3:0]P/N at the rising edge of this

clock..

NOTE: The XRT91L80 can output a 666.51 MHz receive clock

output for Forward Error Correction (FEC).

DISRD

LVTTL

LVCMOS

I

C12

Parallel Receive Data Output Disable

This pin is used to disable the RXDO[3:0]P/N parallel receive

data output bus asynchronously.

"Low" = Normal Mode

"High" = Forces RXDO[3:0]P/N to a logic state "0"

This pin is provided with an internal pull-down.

RXIP

RXIN

CMLDIFF

I

C1

D1

Receive Serial Data Input

The receive serial data stream of 2.488 Gbps is applied to

these input pins. In Forward Error Correction, the receive

serial data stream is 2.666 Gbps.

XRES1P

XRES1N

-

I

G1

F1

External LVDS Biasing Resistors

A 402

resistor with +/-1% tolerance should be placed across

these 2 pins for proper biasing.

RXCLKO16P

RXCLKO16N

LVDS

O

A6

A7

Auxiliary Clock Output (155.52/166.63 MHz)

155.52/166.63 MHz auxiliary clock derived from divide-by-16

CDR recovered clock.

LOCKDET_CDR

LVCMOS

O

C7

CDR Lock Detect

This pin is used to monitor the lock condition of the clock and

data recovery unit.

"Low" = CDR Out of Lock

"High" = CDR Locked

SDEXT

LVTTL,

LVCMOS

I

B5

Signal Detect Input from Optical Module

Hardware Mode When inactive, it will immediately declare a

Loss of Signal Detect (LOSD) condition and assert LOSDET

output pin and control the activity of the RXDO[3:0]P/N parallel

data output based on LOSDMUTE pin setting.

Host Mode In addition to asserting LOSDET output pin, it will

update the LOSD condition on the registers and control the

activity of the RXDO[3:0]P/N parallel data output based on

LOSDMUTE register bit setting.

"Active" = Normal Operation

"Inactive" = LOSD Condition (SDEXT detects signal absence)

This pin is provided with an internal pull-down.

相关PDF资料 |

PDF描述 |

|---|---|

| V24B48M150BG2 | CONVERTER MOD DC/DC 48V 150W |

| VI-J52-MX-F1 | CONVERTER MOD DC/DC 15V 75W |

| V24B48M150BF2 | CONVERTER MOD DC/DC 48V 150W |

| VI-J51-MX-F4 | CONVERTER MOD DC/DC 12V 75W |

| V24B36M150BL | CONVERTER MOD DC/DC 36V 150W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XRT91L80IB-F | 功能描述:总线收发器 Transceiver RoHS:否 制造商:Fairchild Semiconductor 逻辑类型:CMOS 逻辑系列:74VCX 每芯片的通道数量:16 输入电平:CMOS 输出电平:CMOS 输出类型:3-State 高电平输出电流:- 24 mA 低电平输出电流:24 mA 传播延迟时间:6.2 ns 电源电压-最大:2.7 V, 3.6 V 电源电压-最小:1.65 V, 2.3 V 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-48 封装:Reel |

| XRT91L81 | 制造商:EXAR 制造商全称:EXAR 功能描述:2.488/2.666GBPS OC-48/STM-16 SONET/SDH TRANSCEIVER |

| XRT91L81IB | 制造商:EXAR 制造商全称:EXAR 功能描述:2.488/2.666GBPS OC-48/STM-16 SONET/SDH TRANSCEIVER |

| XRT91L82 | 制造商:EXAR 制造商全称:EXAR 功能描述:2.488/2.666 GBPS STS-48/STM-16 SONET/SDH TRANSCEIVER |

| XRT91L82ES | 功能描述:总线收发器 Transceiver RoHS:否 制造商:Fairchild Semiconductor 逻辑类型:CMOS 逻辑系列:74VCX 每芯片的通道数量:16 输入电平:CMOS 输出电平:CMOS 输出类型:3-State 高电平输出电流:- 24 mA 低电平输出电流:24 mA 传播延迟时间:6.2 ns 电源电压-最大:2.7 V, 3.6 V 电源电压-最小:1.65 V, 2.3 V 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-48 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。