参数资料

| 型号: | AD6654BBC |

| 厂商: | Analog Devices Inc |

| 文件页数: | 26/88页 |

| 文件大小: | 0K |

| 描述: | IC ADC 14BIT W/6CH RSP 256CSPBGA |

| 标准包装: | 1 |

| 位数: | 14 |

| 采样率(每秒): | 92.16M |

| 数据接口: | 串行,并联 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 2.5W |

| 电压电源: | 模拟和数字 |

| 工作温度: | -25°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 256-BGA,CSPBGA |

| 供应商设备封装: | 256-CSPBGA(17x17) |

| 包装: | 托盘 |

| 输入数目和类型: | 1 个差分,单极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页当前第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页

AD6654

Rev. 0 | Page 32 of 88

05156-

034

POWER MONITOR

HOLDING

REGISTER

ACCUMULATOR

TO

MEMORY

MAP

FROM

MEMORY

MAP

FROM

INPUT

PORTS

LOAD

CLEAR

LOAD

IS COUNT = 1?

DOWN

COUNTER

TO

INTERRUPT

CONTROLLER

POWER MONITOR

PERIOD REGISTER

Figure 45. ADC Input Mean Power Monitoring Block Diagram

THRESHOLD CROSSING MODE

Control Bits 10

In this mode of operation, the magnitude of the input port

signal is monitored over a programmable time period (given

by AMPR) to count the number of times it crosses a certain

programmable threshold value. This mode is set by program-

ming Logic 1x (where x is a don’t care bit) in the power monitor

function select bits in the power monitor control register of the

DDC input port. Before activating this mode, the user needs to

program the 24-bit AMPR and the 10-bit upper threshold register

of the DDC input port. The same upper threshold register is

used for both power monitoring and gain control (see the ADC

Gain Control section).

After entering this mode, the value in the AMPR is loaded into

a monitor period timer, and the countdown is started. The

magnitude of the input signal is compared to the upper

threshold register (programmed previously) on each input clock

cycle. If the input signal has a magnitude greater than the upper

threshold register, then the MSR register is incremented by 1.

The initial value of the MSR is set to 0. This comparison and

incrementing of the MSR register continues until the monitor

period timer reaches a count of 1.

When the monitor period timer reaches a count of 1, the value

in the MSR is transferred to the power monitor holding register,

which can be read through the microport or the serial port. The

monitor period timer is reloaded with the value in the AMPR,

and the countdown is started. The MSR register is also cleared

to a value of 0. If interrupts are enabled, an interrupt is gener-

ated, and the interrupt status register is updated when the

AMPR reaches a count of 1. Figure 46 illustrates the threshold

crossing logic. The value in the MSR is the number of samples

that have an amplitude greater than the threshold register.

05156-

035

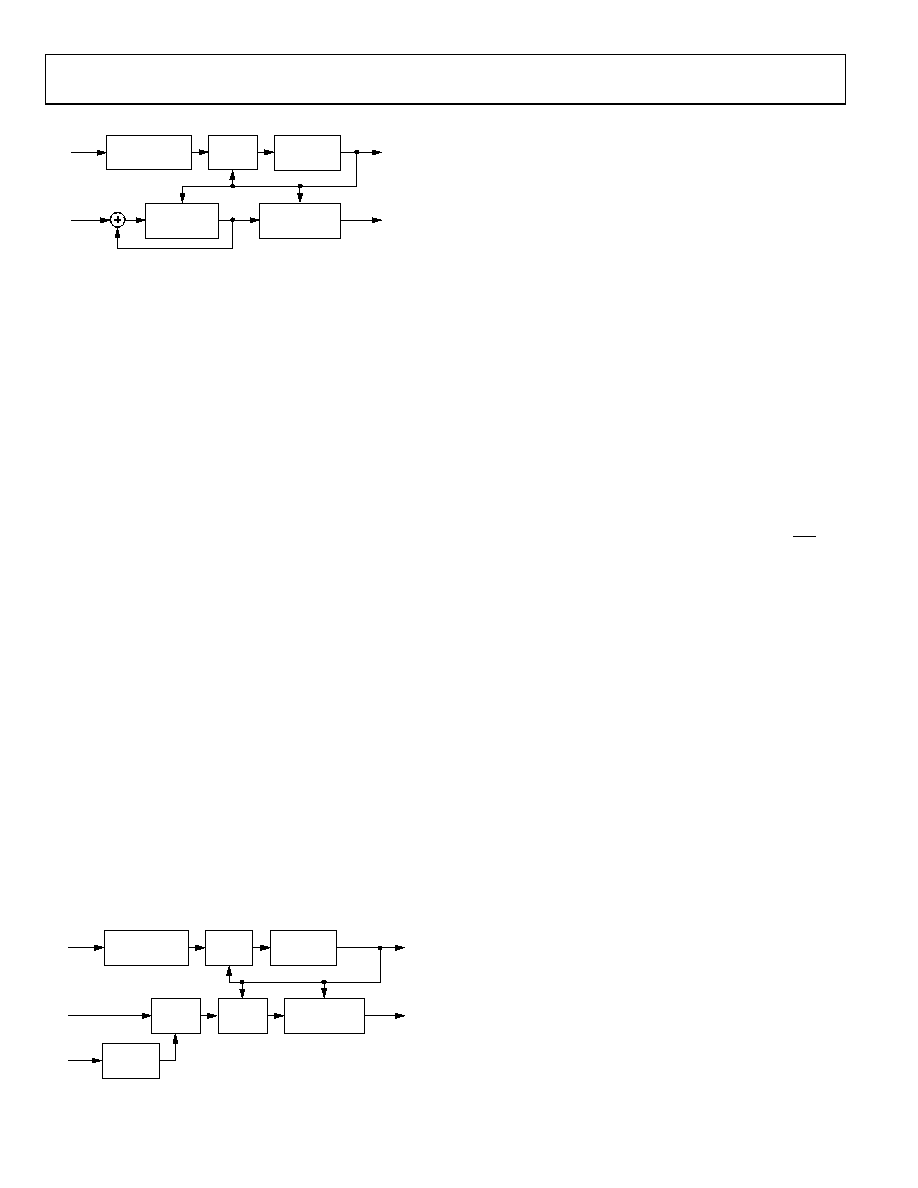

POWER MONITOR

HOLDING

REGISTER

COMPARE

A

> B

UPPER

THRESHOLD

REGISTER

COMPARE

A

> B

TO

MEMORY

MAP

FROM

MEMORY

MAP

FROM

MEMORY

MAP

FROM

INPUT

PORTS

LOAD

CLEAR

LOAD

IS COUNT = 1?

DOWN

COUNTER

TO

INTERRUPT

CONTROLLER

POWER MONITOR

PERIOD REGISTER

B

A

Figure 46. ADC Input Threshold Crossing Block Diagram

ADDITIONAL CONTROL BITS

For additional flexibility in the power monitoring process, two

control bits are provided in the power monitor control register.

The two control bits are the disable monitor period timer bit

and the clear-on-read bit. These options have the same function

in all three modes of operation.

Disable Monitor Period Timer Bit

When the disable monitor period timer bit is written with

Logic 1, the timer continues to run but does not cause the

contents of the MSR to be transferred to the holding register

when the count reaches 1. This function of transferring the

MSR to the power monitor holding register and resetting the

MSR is now controlled by a read operation on the microport or

serial port.

When a microport or serial port read is performed on the

power monitor holding register, the MSR value is transferred to

the holding register. After the read operation, the timer is

reloaded with the AMPR value. If the timer reaches 1 before the

microport or serial port read, the MSR value is not transferred

to the holding register, as in normal operation. The timer still

generates an interrupt on the AD6654 interrupt pin and updates

the interrupt status register. An interrupt appears on the IRP

pin, if interrupts are enabled in the interrupt enable register.

Clear-on-Read Bit

This control bit is valid only when the disable monitor period

timer bit is Logic 1. When both of these bits are set, a read

operation to either the microport or the serial port reads the

MSR value, and the monitor period timer is reloaded with the

AMPR value. The MSR is cleared (written with current input

signal magnitude in peak power and mean power modes;

written with a 0 in threshold crossing mode), and normal

operation continues.

When the monitor period timer is disabled and the clear-on-

read bit is set, a read operation to the power monitor holding

register clears the contents of the MSR and, therefore, the power

monitor loop restarts.

If the clear-on-read bit is Logic 0, the read operation to the

microport or serial port does not clear the MSR value after it is

transferred into the holding register. The value from the

previous monitor time period persists, and it continues to be

compared, accumulated, or incremented, based on new input

signal magnitude values.

相关PDF资料 |

PDF描述 |

|---|---|

| AD670KNZ | IC ADC 8BIT SGNL COND 20DIP |

| AD673JNZ | IC ADC 8BIT REF/CLK/COMP 20DIP |

| AD674BJN | IC ADC 12BIT MONO 3OUT 28-DIP |

| AD676BD | IC ADC 16BIT SAMPLING 28-CDIP |

| AD677BD | IC ADC 16BIT SAMPLING 16-CDIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD6654BBCZ | 功能描述:IC ADC 14BIT W/6CH RSP 256CSPBGA RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:250 系列:- 位数:12 采样率(每秒):1.8M 数据接口:并联 转换器数目:1 功率耗散(最大):1.82W 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-LQFP 供应商设备封装:48-LQFP(7x7) 包装:管件 输入数目和类型:2 个单端,单极 |

| AD6654CBC | 功能描述:IC ADC 14BIT W/4CH RSP 256CSPBGA RoHS:否 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:250 系列:- 位数:12 采样率(每秒):1.8M 数据接口:并联 转换器数目:1 功率耗散(最大):1.82W 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-LQFP 供应商设备封装:48-LQFP(7x7) 包装:管件 输入数目和类型:2 个单端,单极 |

| AD6654CBCZ | 功能描述:IC ADC 14BIT W/4CH RSP 256CSPBGA RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:250 系列:- 位数:12 采样率(每秒):1.8M 数据接口:并联 转换器数目:1 功率耗散(最大):1.82W 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-LQFP 供应商设备封装:48-LQFP(7x7) 包装:管件 输入数目和类型:2 个单端,单极 |

| AD6654XBCZ | 制造商:Analog Devices 功能描述:14-BIT, 92.16 MSPS, 4 & 6-CHANNEL WIDEBAND IF TO BASE BAND R - Bulk |

| AD6655 | 制造商:AD 制造商全称:Analog Devices 功能描述:IF Diversity Receiver |

发布紧急采购,3分钟左右您将得到回复。