参数资料

| 型号: | AD6654BBC |

| 厂商: | Analog Devices Inc |

| 文件页数: | 88/88页 |

| 文件大小: | 0K |

| 描述: | IC ADC 14BIT W/6CH RSP 256CSPBGA |

| 标准包装: | 1 |

| 位数: | 14 |

| 采样率(每秒): | 92.16M |

| 数据接口: | 串行,并联 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 2.5W |

| 电压电源: | 模拟和数字 |

| 工作温度: | -25°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 256-BGA,CSPBGA |

| 供应商设备封装: | 256-CSPBGA(17x17) |

| 包装: | 托盘 |

| 输入数目和类型: | 1 个差分,单极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页当前第88页

AD6654

Rev. 0 | Page 9 of 88

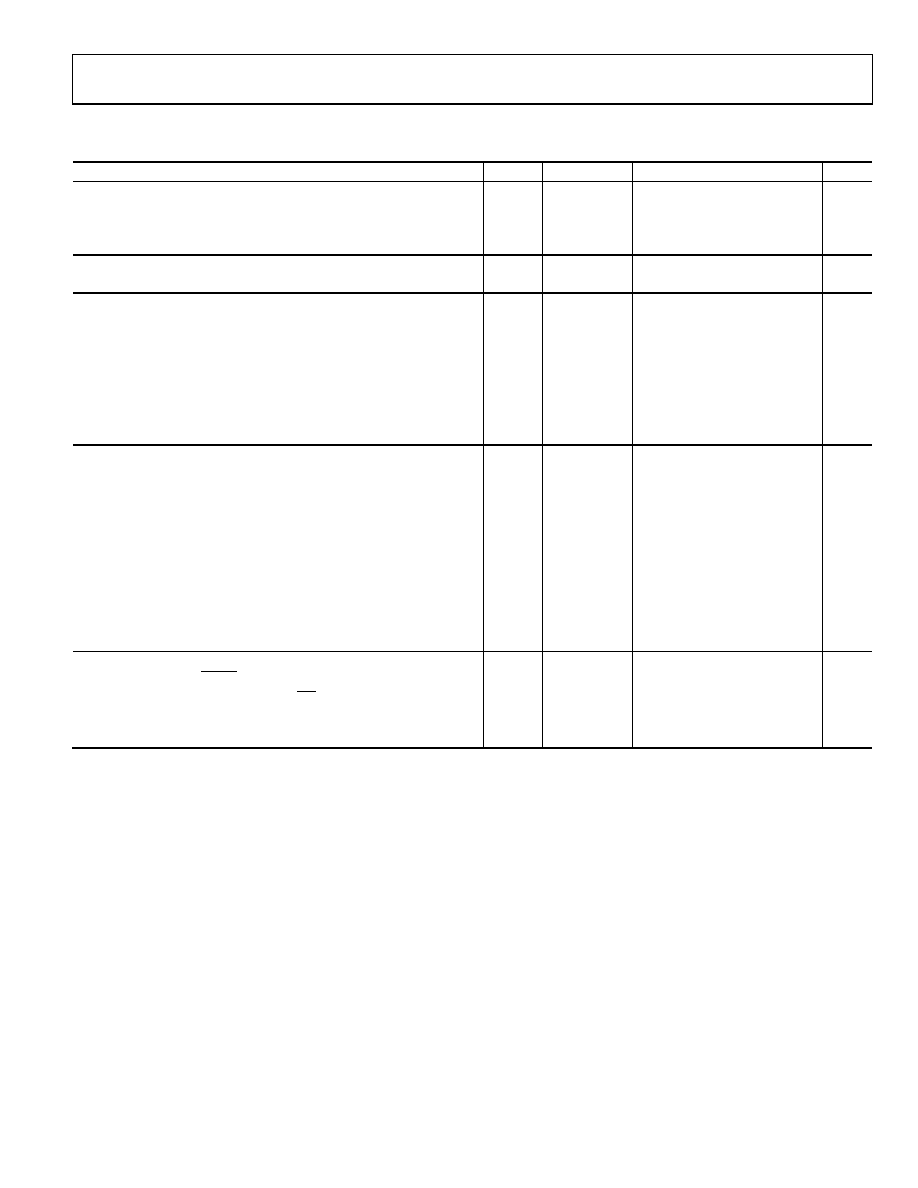

TIMING CHARACTERISTICS

Table 7.

Temp

Test Level

Min

Typ

Max

Unit

CLK TIMING REQUIREMENTS

tCLK

CLK Period

Full

IV

10.85

ns

tCLKL

CLK Width Low

Full

IV

5.154

0.5 × tCLK

ns

tCLKH

CLK Width High

Full

IV

5.154

0.5 × tCLK

ns

INPUT WIDEBAND DATA TIMING REQUIREMENTS

tDEXP

↑CLK to EXP[2:0] Delay

Full

IV

5.98

10.74

ns

PARALLEL OUTPUT PORT TIMING REQUIREMENTS (MASTER)

tDPREQ

↑PCLK to ↑Px REQ Delay (x = A, B, C)

Full

IV

1.77

3.86

ns

tDPP

↑PCLK to Px[15:0] Delay (x = A, B, C)

Full

IV

2.07

5.29

ns

tDPIQ

↑PCLK to Px IQ Delay (x = A, B, C)

Full

IV

0.48

5.49

ns

tDPCH

↑PCLK to Px CH[2:0] Delay (x = A, B, C)

Full

IV

0.38

5.35

ns

tDPGAIN

↑PCLK to Px Gain Delay (x = A, B, C)

Full

IV

0.23

4.95

ns

tSPA

Px ACK to

↑PCLK Setup Time (x = A, B, C)

Full

IV

4.59

ns

tHPA

Px ACK to

↑PCLK Hold Time (x = A, B, C)

Full

IV

0.90

ns

PARALLEL OUTPUT PORT TIMING REQUIREMENTS (SLAVE)

tPCLK

PCLK Period

Full

IV

5.0

ns

tPCLKL

PCLK Low Period

Full

IV

1.7

0.5 × tPCLK

ns

tPCLKH

PCLK High Period

Full

IV

0.7

0.5 × tPCLK

ns

tDPREQ

↑PCLK to ↑Px REQ Delay (x = A, B, C)

Full

IV

4.72

8.87

ns

tDPP

↑PCLK to Px[15:0] Delay (x = A, B, C)

Full

IV

4.8

8.48

ns

tDPIQ

↑PCLK to Px IQ Delay (x = A, B, C)

Full

IV

4.83

10.94

ns

tDPCH

↑PCLK to Px CH[2:0] Delay (x = A, B, C)

Full

IV

4.88

10.09

ns

tDPGAIN

↑PCLK to Px Gain Delay (x = A, B, C)

Full

IV

5.08

11.49

ns

tSPA

Px ACK to

↓PCLK Setup Time (x = A, B, C)

Full

IV

6.09

ns

tHPA

Px ACK to

↓PCLK Hold Time (x = A, B, C)

Full

IV

1.0

ns

MISC PINS TIMING REQUIREMENTS

tRESET

RESET Width Low

Full

IV

30

ns

tDIRP

CPUCLK/SCLK to IRP Delay

Full

V

7.5

ns

tSSYNC

SYNC(0, 1, 2, 3) to

↑CLK Setup Time

Full

IV

0.87

ns

tHSYNC

SYNC(0, 1, 2, 3) to

↑CLK Hold Time

Full

IV

0.67

ns

1 All timing specifications are valid over the VDDCORE range of 1.7 V to 1.9 V, and the VDDIO range of 3.0 V to 3.6 V.

2 CLOAD = 40 pF on all outputs, unless otherwise noted.

3 These timing parameters are derived from the ADC ENC rate with DDC CLK driven directly from ADC DR output.

相关PDF资料 |

PDF描述 |

|---|---|

| AD670KNZ | IC ADC 8BIT SGNL COND 20DIP |

| AD673JNZ | IC ADC 8BIT REF/CLK/COMP 20DIP |

| AD674BJN | IC ADC 12BIT MONO 3OUT 28-DIP |

| AD676BD | IC ADC 16BIT SAMPLING 28-CDIP |

| AD677BD | IC ADC 16BIT SAMPLING 16-CDIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD6654BBCZ | 功能描述:IC ADC 14BIT W/6CH RSP 256CSPBGA RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:250 系列:- 位数:12 采样率(每秒):1.8M 数据接口:并联 转换器数目:1 功率耗散(最大):1.82W 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-LQFP 供应商设备封装:48-LQFP(7x7) 包装:管件 输入数目和类型:2 个单端,单极 |

| AD6654CBC | 功能描述:IC ADC 14BIT W/4CH RSP 256CSPBGA RoHS:否 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:250 系列:- 位数:12 采样率(每秒):1.8M 数据接口:并联 转换器数目:1 功率耗散(最大):1.82W 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-LQFP 供应商设备封装:48-LQFP(7x7) 包装:管件 输入数目和类型:2 个单端,单极 |

| AD6654CBCZ | 功能描述:IC ADC 14BIT W/4CH RSP 256CSPBGA RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:250 系列:- 位数:12 采样率(每秒):1.8M 数据接口:并联 转换器数目:1 功率耗散(最大):1.82W 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-LQFP 供应商设备封装:48-LQFP(7x7) 包装:管件 输入数目和类型:2 个单端,单极 |

| AD6654XBCZ | 制造商:Analog Devices 功能描述:14-BIT, 92.16 MSPS, 4 & 6-CHANNEL WIDEBAND IF TO BASE BAND R - Bulk |

| AD6655 | 制造商:AD 制造商全称:Analog Devices 功能描述:IF Diversity Receiver |

发布紧急采购,3分钟左右您将得到回复。