参数资料

| 型号: | AD6654BBC |

| 厂商: | Analog Devices Inc |

| 文件页数: | 75/88页 |

| 文件大小: | 0K |

| 描述: | IC ADC 14BIT W/6CH RSP 256CSPBGA |

| 标准包装: | 1 |

| 位数: | 14 |

| 采样率(每秒): | 92.16M |

| 数据接口: | 串行,并联 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 2.5W |

| 电压电源: | 模拟和数字 |

| 工作温度: | -25°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 256-BGA,CSPBGA |

| 供应商设备封装: | 256-CSPBGA(17x17) |

| 包装: | 托盘 |

| 输入数目和类型: | 1 个差分,单极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页当前第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页

AD6654

Rev. 0 | Page 77 of 88

<10>: ADC Port CLK Invert Bit. When this bit is set, the

inverted ADC port clock is used to register ADC input data into

the part. When this bit is cleared, the clock is used as is, without

any inversion or phase change.

<9>: Reserved. This bit must be written with Logic 0.

<8>: Reserved. This bit must be written with Logic 0.

<7:6>: ADC Pre PLL Clock Divider Bits.: These bits control the

PLL clock divider. The PLL clock is derived from the ADC data

port CLK.

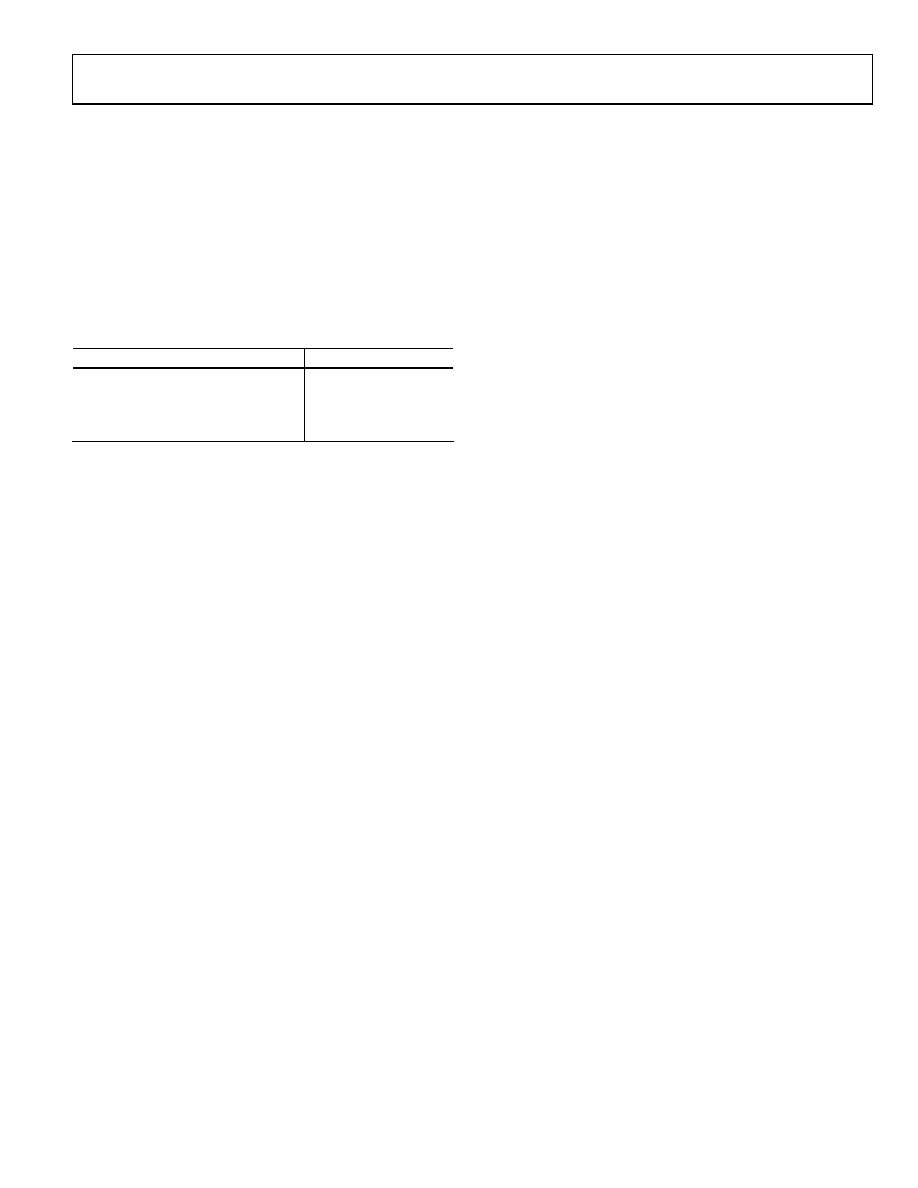

Table 31. Divide-by Values for PLL Clock Divider Bits

PLL Clock Divider Bits <12:11>

Divide-by Value

00

Divide by 1, bypass

01

Divide by 2

10

Divide by 4

11

Divide by 8

<5:1>: PLL Clock Multiplier Bits. These bits control the PLL

clock multiplier. The output of the PLL clock divider is

multiplied with the binary value of these bits. Valid range for

the multiplier is from 4 to 20. A value outside this range powers

down the PLL, resulting in the PLL clock being the same as the

ADC data port CLK.

<0>: This bit is open.

ADC Port Gain Control <7:0>

<7>: This bit is open.

<6:1>: This 6-bit word specifies the relinearization pipe delay to

be used in the ADC input gain control block. The decimal

representation of these bits is the number of input clock cycle

pipeline delays between the external EXP data output and the

internal application of relinearization based on EXP.

<0>: Gain Control Enable Bit. This bit controls the configura-

tion of the EXP<2:0> bits for the ADC input port. When the

gain control enable bit is Logic 1, the EXP<2:0> bits are

configured as outputs. When this bit is cleared, the EXP<2:0>

bits are inputs.

ADC Port Dwell Timer <19:0>

This register is used to set the dwell time for the gain control

block. When the gain control block is active and detects a

decrease in the signal level below the lower threshold value

(programmable), a dwell-time counter is initiated to provide

temporal hysteresis. Doing so prevents the gain from being

continuously switched. Note that the dwell timer is turned on

only after a drop below the lower threshold is detected in the

signal level.

ADC Port Power Monitor Period <23:0>

This register is used in the power monitoring logic to set the

period of time for which ADC input data is monitored. This

value represents the monitor period in number of ADC port

clock cycles.

ADC Port Power Monitor Output <23:0>

This register is read only and contains the current status of the

power monitoring logic output. The output is dependent on the

power monitoring mode selected. When the power monitor

block is enabled, this register is updated at the end of each

power monitor period. This register is updated even if an

interrupt signal is not generated.

ADC Port Upper Threshold <9:0>

This register serves the dual purpose of specifying the upper

threshold value in the gain control block and in the power

monitoring block, depending on which block is active. ADC

port input data having a magnitude greater than this value

triggers a gain change in the gain control block. ADC port input

data having a magnitude greater than this value is monitored in

the power monitoring block (in peak detect or threshold

crossing mode). The value of the register is compared with the

absolute magnitude of the input port data.

ADC Port Lower Threshold <9:0>

This register is used in the gain control block and represents the

magnitude of the lower threshold for ADC port input data. Any

ADC input data having a magnitude below the lower threshold

initiates the dwell time counter. The value of the register is

compared with the absolute magnitude of the input port data.

ADC Port Signal Monitor <4:0>

This register controls the functions of the power monitoring

block.

<4>: Disable Power Monitor Period Timer Bit. When this bit is

set, the power monitor period timer no longer controls the

update of the power monitor holding register. A user read to the

power monitor holding register updates this register. When this

bit is cleared, the power monitor period register controls the

timer and, therefore, controls the update rate of the power

monitor holding register.

<3>: Clear-on-Read Bit. When this bit is set, the power monitor

holding register is cleared every time this register is read. This

bit controls whether the power monitoring function is cleared

after a read of the power monitor period register. If this bit is

set, the monitoring function is cleared after the read. If this bit

is Logic 0, the monitoring function is not cleared. This bit is a

don’t care bit, if the disable integration counter bit is cleared.

相关PDF资料 |

PDF描述 |

|---|---|

| AD670KNZ | IC ADC 8BIT SGNL COND 20DIP |

| AD673JNZ | IC ADC 8BIT REF/CLK/COMP 20DIP |

| AD674BJN | IC ADC 12BIT MONO 3OUT 28-DIP |

| AD676BD | IC ADC 16BIT SAMPLING 28-CDIP |

| AD677BD | IC ADC 16BIT SAMPLING 16-CDIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD6654BBCZ | 功能描述:IC ADC 14BIT W/6CH RSP 256CSPBGA RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:250 系列:- 位数:12 采样率(每秒):1.8M 数据接口:并联 转换器数目:1 功率耗散(最大):1.82W 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-LQFP 供应商设备封装:48-LQFP(7x7) 包装:管件 输入数目和类型:2 个单端,单极 |

| AD6654CBC | 功能描述:IC ADC 14BIT W/4CH RSP 256CSPBGA RoHS:否 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:250 系列:- 位数:12 采样率(每秒):1.8M 数据接口:并联 转换器数目:1 功率耗散(最大):1.82W 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-LQFP 供应商设备封装:48-LQFP(7x7) 包装:管件 输入数目和类型:2 个单端,单极 |

| AD6654CBCZ | 功能描述:IC ADC 14BIT W/4CH RSP 256CSPBGA RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:250 系列:- 位数:12 采样率(每秒):1.8M 数据接口:并联 转换器数目:1 功率耗散(最大):1.82W 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-LQFP 供应商设备封装:48-LQFP(7x7) 包装:管件 输入数目和类型:2 个单端,单极 |

| AD6654XBCZ | 制造商:Analog Devices 功能描述:14-BIT, 92.16 MSPS, 4 & 6-CHANNEL WIDEBAND IF TO BASE BAND R - Bulk |

| AD6655 | 制造商:AD 制造商全称:Analog Devices 功能描述:IF Diversity Receiver |

发布紧急采购,3分钟左右您将得到回复。