参数资料

| 型号: | AD6654BBC |

| 厂商: | Analog Devices Inc |

| 文件页数: | 81/88页 |

| 文件大小: | 0K |

| 描述: | IC ADC 14BIT W/6CH RSP 256CSPBGA |

| 标准包装: | 1 |

| 位数: | 14 |

| 采样率(每秒): | 92.16M |

| 数据接口: | 串行,并联 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 2.5W |

| 电压电源: | 模拟和数字 |

| 工作温度: | -25°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 256-BGA,CSPBGA |

| 供应商设备封装: | 256-CSPBGA(17x17) |

| 包装: | 托盘 |

| 输入数目和类型: | 1 个差分,单极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页当前第81页第82页第83页第84页第85页第86页第87页第88页

AD6654

Rev. 0 | Page 82 of 88

format of the AGC error threshold register is four bits to the left

of the binary point and eight bits to the right.

See the Automatic Gain Control section for details.

256

)

2

(

log

20

10

×

=

Threshold

Error

round

Value

Register

AGC Average Samples <5:0>

This 6-bit register contains the scale used for the CIC filter and

the number of power samples to be averaged before being sent

to the CIC filter.

<5:2>: CIC Scale. This 4-bit word defines the scale used for the

CIC filter. Each increment of this word increases the CIC scale

by 6.02 dB.

<1:0>: Number of AGC Average Samples. This defines the

number of samples to be averaged before they are sent to the

CIC decimating filter. See Table 41.

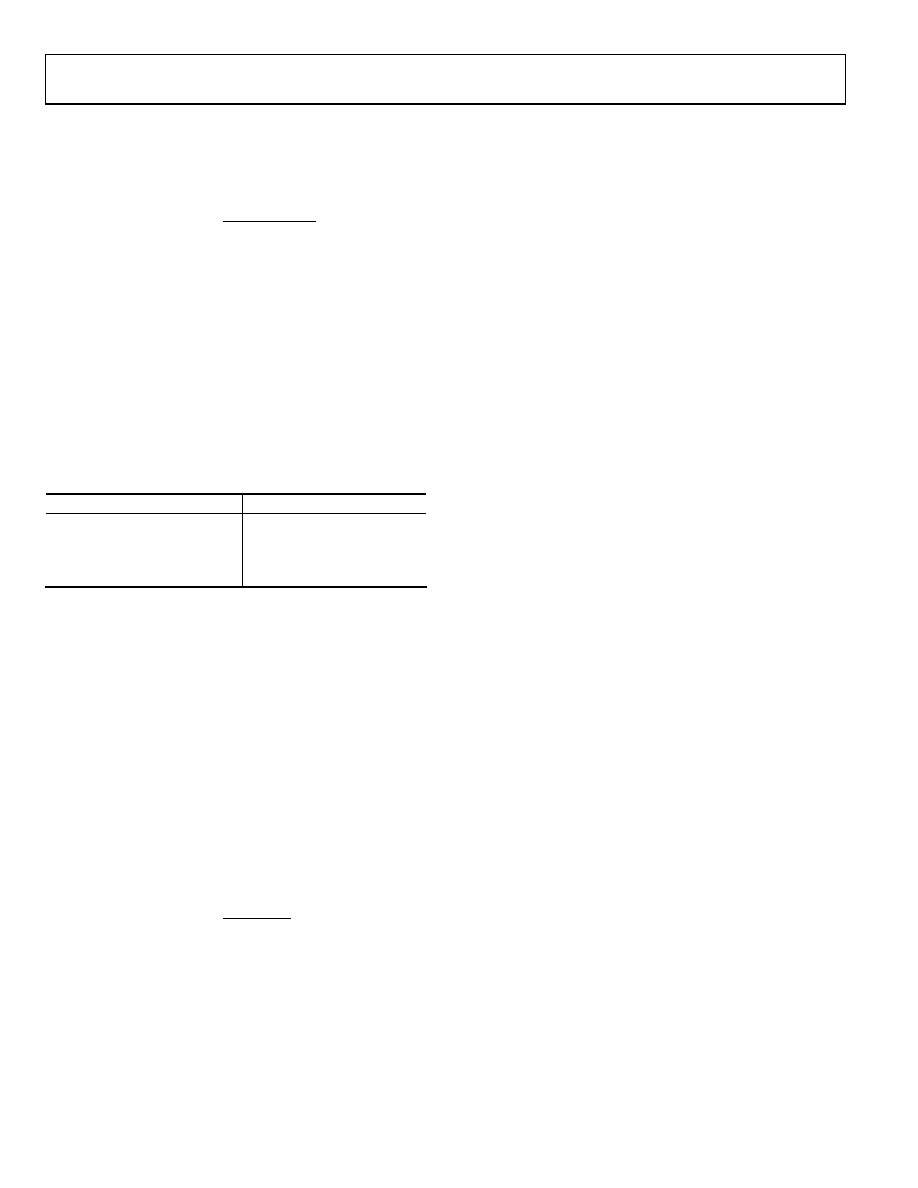

Table 41. Number of AGC Average Samples

AGC Average Samples <1:0>

Number of Samples Taken

00

1

01

2

10

3

11

4

AGC Pole Location <7:0>

This 8-bit register is used to define P, the open-loop filter pole

location. Its value can be set from 0 to 0.996 in steps of 0.0039.

This value of P is updated in the AGC loop each time the AGC

is initialized. This open-loop pole location directly impacts the

closed-loop pole locations, as explained in the Automatic Gain

Control section.

AGC Desired Level <7:0>

This register contains the desired signal level or desired clipping

level, depending on operational mode. This desired request

level (R) can be set in dB from 0 to 23.99 in steps of 0.094 dB.

The request level (R) in dB should be converted to a register

setting using the following formula:

×

=

64

)

2

(

log

20

10

R

round

Value

Register

AGC Loop Gain 2 <7:0>

This 8-bit register is used to define K2, the second possible

open-loop gain. Its value can be set from 0 to 0.996 in steps of

0.0039. This value of K2 is updated each time the AGC is

initialized. When the magnitude-of-error signal in the loop is

greater than the AGC error threshold, then K2 is used by the

loop. K2 is updated only when the AGC is initialized.

AGC Loop Gain 1 <7:0>

This 8-bit register is used to define K1, the open-loop gain. Its

value can be set from 0 to 0.996 in steps of 0.0039. This value of

K is updated in the AGC loop each time the AGC is initialized.

When the magnitude-of-error signal in the loop is less than the

AGC error threshold, then K1 is used by the loop. K1 is updated

only when the AGC is initialized.

I Path Signature Register <15:0>

This 16-bit signature register is for the I path of the channel

logic. The signature register records data on the networks that

leave the channel logic, just before entering the second data

router.

Q Path Signature Register <15:0>

This 16-bit signature register is for the Q path of the channel

logic. The signature register records data on the networks that

leave the channel logic, just before entering the second data

router.

BIST Control <15:0>

<15>: Disable Signature Generation Bit. When this bit is active

high, the signature registers do not produce a pseudorandom

output value, but instead directly load the 24-bit input data.

When this bit is cleared, the signature register produces a

pseudorandom output for every clock cycle that it is active. See

the User-Configurable Built-In Self-Test (BIST) section for

details.

<14:0>: BIST Timer Bits. The <14:0> bits of this register form a

15-bit word that is loaded into the BIST timer. After loading the

BIST timer, the signature register is enabled for operation while

the timer is actively counting down. See the User-Configurable

Built-In Self-Test (BIST) section for details.

OUTPUT PORT REGISTER MAP

This part of the memory map deals with the output data and

controls for parallel output ports.

Parallel Port Output Control <23:0>

<23>: Port C Append RSSI Bit. When this bit is set, an RSSI

word is appended to every I/Q output sample, regardless of

whether the RSSI word is updated in the AGC. When this bit is

cleared, an RSSI word is appended to an I/Q output sample only

when the RSSI word is updated. The RSSI word is not output for

subsequent I/Q samples until the next time the RSSI is updated

in the AGC.

<22>: Port C, Data Format Bit. When this bit is set, the port is

configured for 8-bit parallel I/Q mode. When cleared, the port

is configured for 16-bit interleaved I/Q mode. See the Parallel

Port Output section for details.

<21>: Port C, AGC5 Enable Bit. When this bit is set, AGC5

data (I/Q data) is output on parallel Output Port C (data bus).

相关PDF资料 |

PDF描述 |

|---|---|

| AD670KNZ | IC ADC 8BIT SGNL COND 20DIP |

| AD673JNZ | IC ADC 8BIT REF/CLK/COMP 20DIP |

| AD674BJN | IC ADC 12BIT MONO 3OUT 28-DIP |

| AD676BD | IC ADC 16BIT SAMPLING 28-CDIP |

| AD677BD | IC ADC 16BIT SAMPLING 16-CDIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD6654BBCZ | 功能描述:IC ADC 14BIT W/6CH RSP 256CSPBGA RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:250 系列:- 位数:12 采样率(每秒):1.8M 数据接口:并联 转换器数目:1 功率耗散(最大):1.82W 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-LQFP 供应商设备封装:48-LQFP(7x7) 包装:管件 输入数目和类型:2 个单端,单极 |

| AD6654CBC | 功能描述:IC ADC 14BIT W/4CH RSP 256CSPBGA RoHS:否 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:250 系列:- 位数:12 采样率(每秒):1.8M 数据接口:并联 转换器数目:1 功率耗散(最大):1.82W 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-LQFP 供应商设备封装:48-LQFP(7x7) 包装:管件 输入数目和类型:2 个单端,单极 |

| AD6654CBCZ | 功能描述:IC ADC 14BIT W/4CH RSP 256CSPBGA RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:250 系列:- 位数:12 采样率(每秒):1.8M 数据接口:并联 转换器数目:1 功率耗散(最大):1.82W 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-LQFP 供应商设备封装:48-LQFP(7x7) 包装:管件 输入数目和类型:2 个单端,单极 |

| AD6654XBCZ | 制造商:Analog Devices 功能描述:14-BIT, 92.16 MSPS, 4 & 6-CHANNEL WIDEBAND IF TO BASE BAND R - Bulk |

| AD6655 | 制造商:AD 制造商全称:Analog Devices 功能描述:IF Diversity Receiver |

发布紧急采购,3分钟左右您将得到回复。