- 您现在的位置:买卖IC网 > PDF目录16836 > AD9549A/PCBZ (Analog Devices Inc)BOARD EVALUATION FOR AD9549A PDF资料下载

参数资料

| 型号: | AD9549A/PCBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 49/76页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION FOR AD9549A |

| 设计资源: | AD9549 Schematics AD9549 Gerber Files |

| 标准包装: | 1 |

| 主要目的: | 计时,时钟发生器 |

| 嵌入式: | 否 |

| 已用 IC / 零件: | AD9549A |

| 主要属性: | 8 kHz ~ 750 MHz 输入 |

| 次要属性: | 差分输出 |

| 已供物品: | 板 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页当前第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页

AD9549

Rev. D | Page 53 of 76

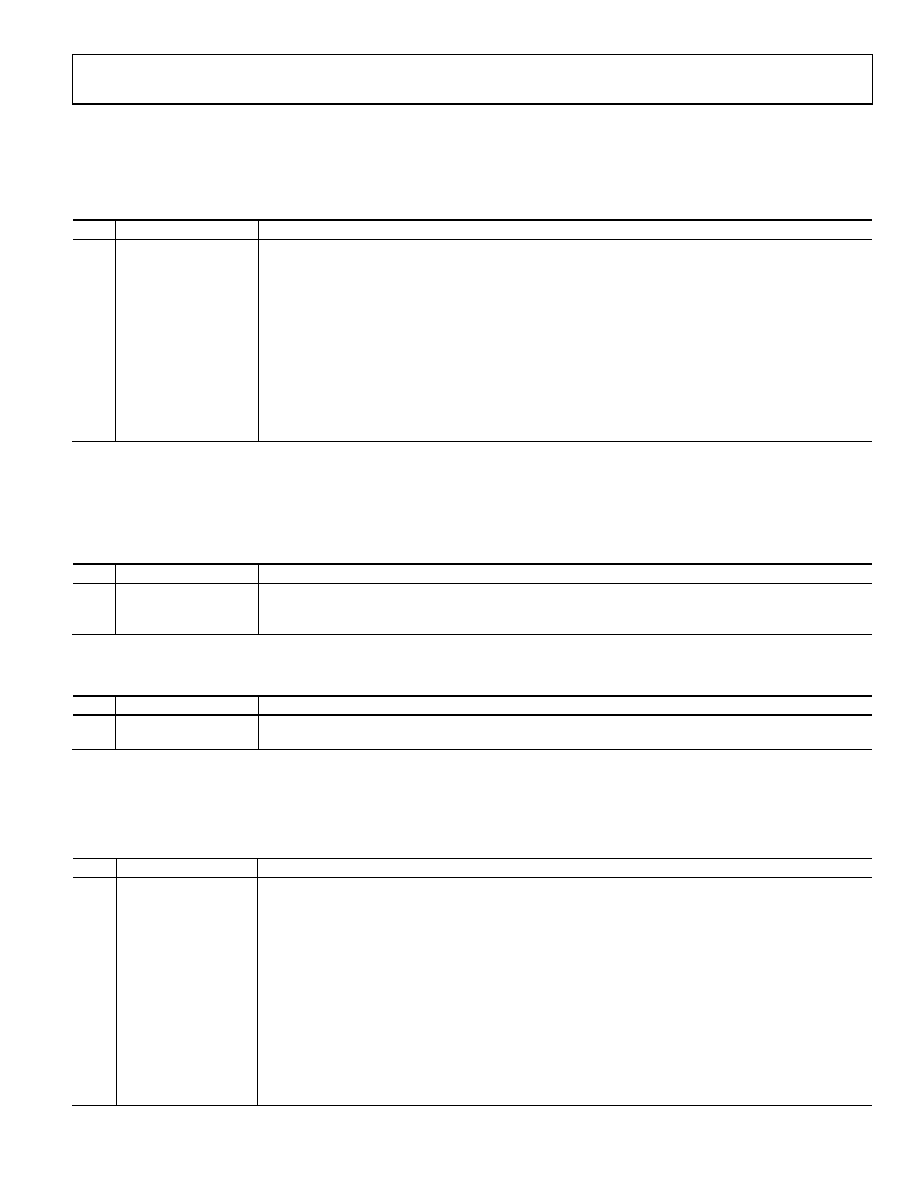

I/O REGISTER DESCRIPTIONS

SERIAL PORT CONFIGURATION (REGISTER 0x0000 TO REGISTER 0x0005)

Register 0x0000—Serial Configuration

Table 14.

Bits

Bit Name

Description

[7:4]

These bits are the mirror image of Bits[3:0].

3

Long instruction

Read-only. The AD9549 supports only long instructions.

2

Soft reset

Resets register map, except for Register 0x0000. Setting this bit forces a soft reset, meaning that S1 to S4

are not tristated, nor is their state read when this bit is cleared. The AD9549 assumes the values of S1 to S4

that were present during the last hard reset. This bit is not self-clearing, and all other registers are restored

to their default values after a soft reset.

1

LSB first

Sets bit order for serial port.

1 = LSB first.

0 = MSB first. I/O update must occur for MSB first to take effect.

0

SDO active

Enables SDO pin.

1 = SDO pin enabled (4-wire serial port mode).

0 = 3-wire mode.

Register 0x0001—Reserved

Register 0x0002 and Register 0x0003—Part ID (Read Only)

Register 0x0004—Serial Options

Table 15.

Bits

Bit Name

Description

0

Read buffer register

For buffered registers, serial port readback reads from actual (active) registers instead of the buffer.

1 = reads the buffered values that take effect during the next I/O update.

0 = reads values that are currently in effect.

Register 0x0005—Serial Options (Self-Clearing)

Table 16.

Bits

Bit Name

Description

0

Register update

Software access to the register update pin function. Writing a 1 to this bit is identical to performing an I/O

update.

POWER-DOWN AND RESET (REGISTER 0x0010 TO REGISTER 0x0013)

Register 0x0010—Power-Down and Enable

Power-up default is defined by the startup pins.

Table 17.

Bits

Bit Name

Description

7

PD HSTL driver

Power down HSTL output driver.

1 = HSTL driver powered down.

6

Enable CMOS driver

Power up CMOS output driver.

1 = CMOS driver on.

5

Enable output doubler

Power up output clock generator doubler. Output doubler must still be enabled in Register 0200.

4

PD SYSCLK PLL

System clock multiplier power-down.

1 = system clock multiplier powered down.

3

PD REFA

Power-down reference clock A input (and related circuits).

2

PD REFB

Power-down reference clock B input (and related circuits).

1

Full PD

Setting this bit is identical to activating the PD pin and puts all blocks (except serial port) into power-down

mode. SYSCLK is turned off.

0

Digital PD

Remove clock from most of digital section; leave serial port usable. In contrast to full PD, setting this bit

does not debias inputs, allowing for quick wake-up.

相关PDF资料 |

PDF描述 |

|---|---|

| ESC05DRTS-S734 | CONN EDGECARD 10POS DIP .100 SLD |

| MAX6250BEPA+ | IC VREF SERIES BURIED ZNR 8-PDIP |

| MAX6133A30+T | IC VREF SERIES PREC 3V 8-UMAX |

| MAX6133A41+T | IC VREF SERIES PREC 4.096V 8UMAX |

| MAX6133A50+T | IC VREF SERIES PREC 5V 8-UMAX |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9549BCPZ | 制造商:Analog Devices 功能描述: |

| AD9549BCPZ-REEL7 | 制造商:Analog Devices 功能描述:PLL CLOCK SYNTHESIZER SGL 64LFCSP EP - Tape and Reel |

| AD9549BCPZ-TR | 制造商:Analog Devices 功能描述:650MHZ DDS CLK GEN W/SYNCH REEL - Tape and Reel |

| AD9549XCPZ | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual Input Network Clock Generator/Synchronizer |

| AD9550 | 制造商:AD 制造商全称:Analog Devices 功能描述:Integer-N Clock Translator for Wireline Communications |

发布紧急采购,3分钟左右您将得到回复。